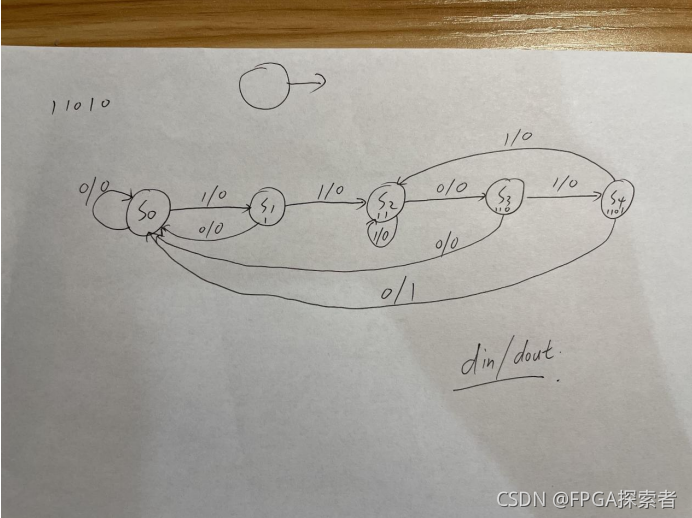

1.“11010序列检测器”状态转移图

2.Verilog代码

module fsm(x,z,clk,rst,data);

input clk,rst,x;

input [20:0]data;

output reg z;

reg[2:0]state,nstate;

parameter s0 = 3'b000,//状态编码

s1 = 3'b001,

s2 = 3'b011,

s3 = 3'b010,

s4 = 3'b110;

always @(posedge clk)

begin

if(rst)state<=s0;

else state<=nstate;

end

always @(state or x) //产生次态

begin

case(state)

s0:if(x==1) nstate<=s1;

else nstate<=s0;

s1:if(x==1) nstate<=s2;

else nstate<=s0;

s2: if(x==0) nstate<=s3;

else nstate<=s2;

s3: if(x==1) nstate<=s4;

else nstate<=s0;

s4: if(x==0) nstate<=s0;

else nstate<=s2;

default:nstate <= s0;

endcase

end

always @(state)//输出

begin

case(state)

s4:z=1'b1;

default:z=1'b0;

endcase

end

endmodule3.testbench仿真代码

`timescale 1ns/1ps

//声明定义

module tb();

reg clk;

reg rst;

reg x;

reg[20:0] data;

wire z;

//例化模块

fsm uut (

.data(data),

.x(x),

.z(z),

.clk(clk),

.rst(rst)

);

assign x=data[20];

//产生激励

initial begin

clk = 0;

rst = 1;

#3

rst=0;

#20

rst=1;

data=21'b 1101_0110_0101_0011_01001;

end

always #10 clk=~clk;

always@(posedge clk)

begin

#2 data={data[19:0],data[20]};

end

endmodule

4.仿真结果

771

771

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?