目录

各个定时器的时钟频率

APB1总线时钟为4分频即42M,APB2总线时钟为2分频即84M;所以TIM1、TIM8~TIM11的时钟为APB2时钟的两倍即168M;TIM2~TIM7、TIM12~TIM14的时钟为APB1的时钟的两倍即84M。

时间计算公式

Tout = ((arr+1)*(psc+1))/Tclk;

寄存器配置步骤-以定时器2为例

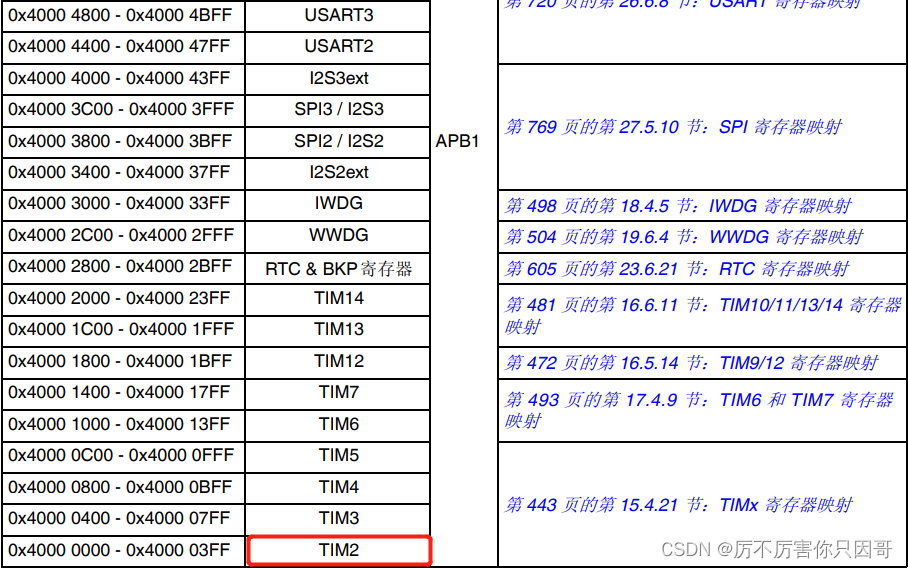

查看定时器2在哪个总线上

由于在APB1的总线上,APB1的时钟频率为42Mhz。当 APBx presc不等于1时

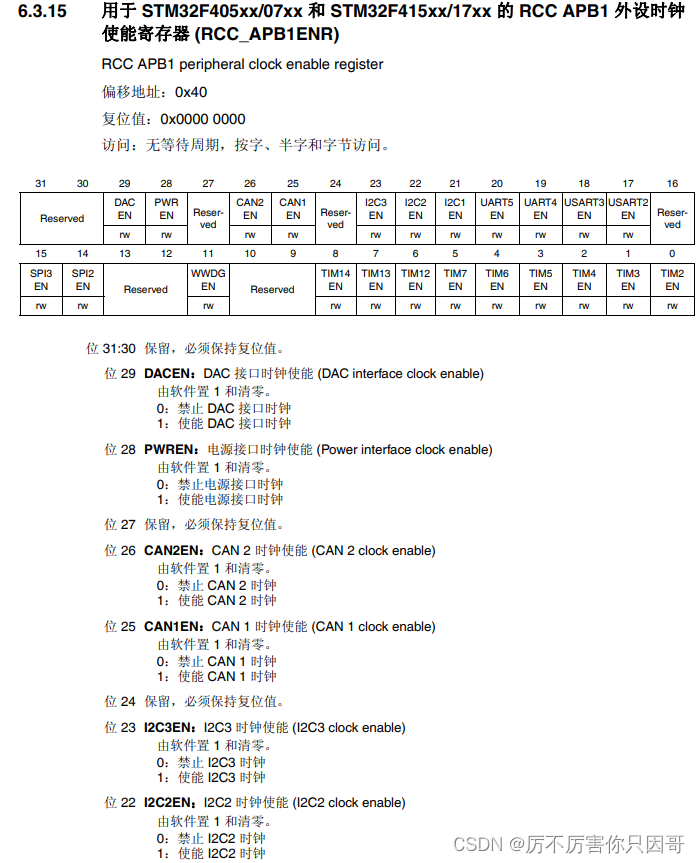

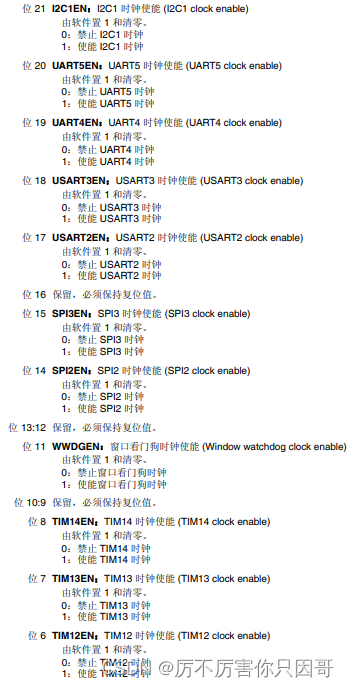

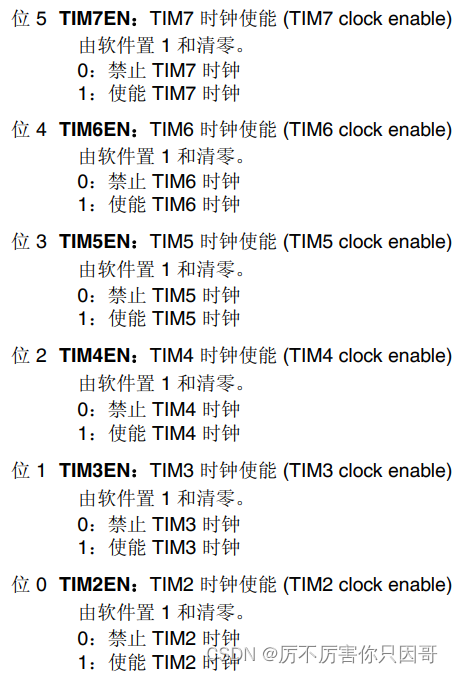

需要进行2倍频 所以TIM2的定时器时钟频率为84Mhz设置RCC->APB1ENR寄存器上的TIM2时钟

查看寄存器列表TIM2EN在APB1ENR寄存器中的第0位

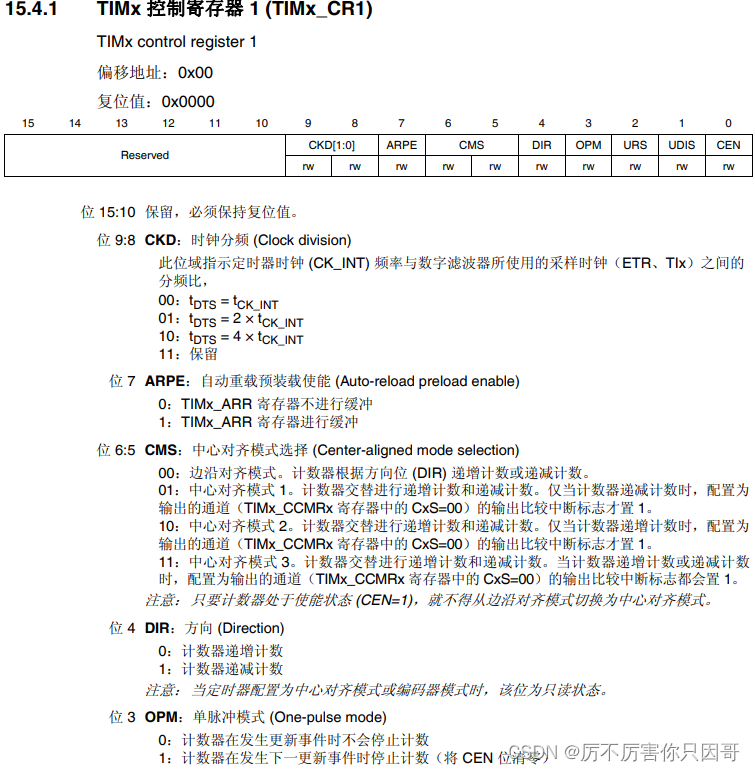

RCC ->APB1ENR |= (1<<0) ;//使能时钟APB1设置TIMx控制寄存器1(TIMx_CR1)

TIM2 ->CR1 |=1<<0;//使能TIM2计数器

//当ARPE位=0 ARR寄存器被写值时,将立即更新到计数器寄存器中,马上进行计数。

//当ARPE位=1 ARR寄存器被写值时,将数值放入自动重载活动寄存器中,

//等到更新事件出现时自动重载活动寄存器会将寄存器放入计数器寄存器中

TIM2 ->CR1 &= (~(1<<7));

//DIR位:取为0时 是计数器递增计数 (向上计数方式)

//没有进行设置的值默认都为0

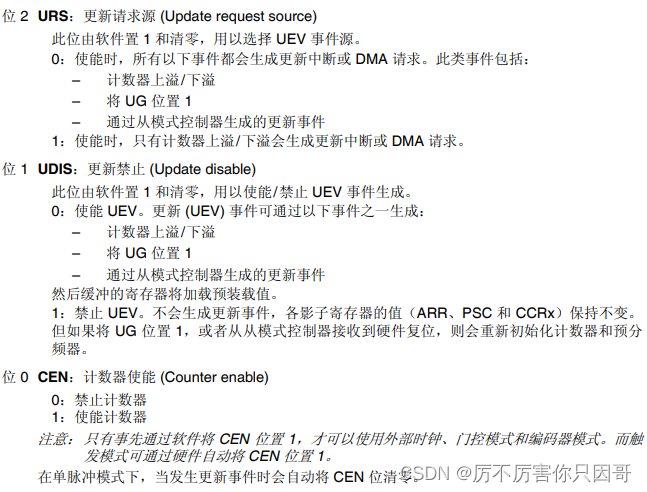

设置预分频寄存器(TIMx_PSC)

预分频寄存器可以将APB1总线的频率进行分频给到计数器的时钟频率 比如预分频值为999

则计数器时钟频率为 84Mhz/999+1

TIM2 ->PSC = psc-1;//设置预分频系数设置自动重装载值(TIMx_ARR)

此寄存器为计数值的数量,向下计数时 有最大值减为0则进行更新事件

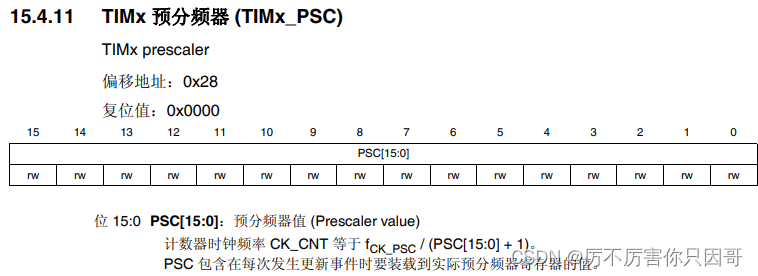

TIM2 ->ARR = arr-1;//设置自动重装载值设置中断使能寄存器(TIMx_DIER)

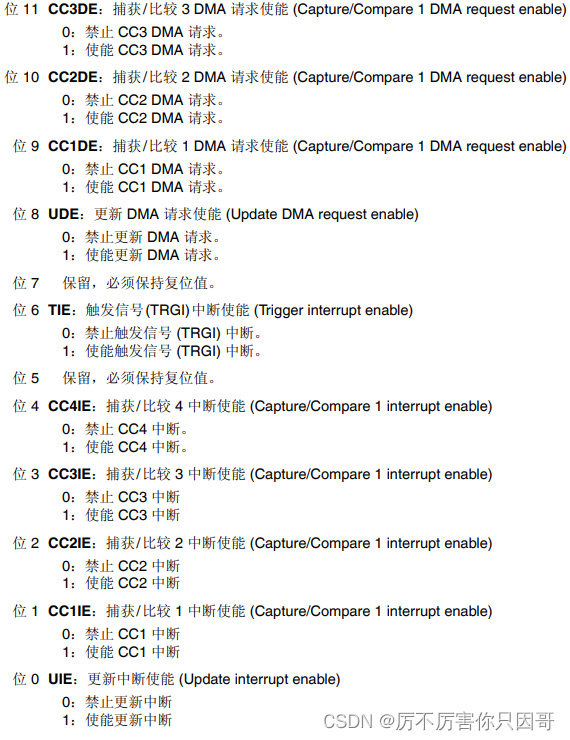

这里由于我们是普通定时器没有用到DMA,触发,捕获/比较这些功能,所以选择更新中断使能

UIE更新中断使能是第0位

TIM2 ->DIER |= 1<<0;//开启定时器中断在中断处理函数中进行读取状态寄存器(TIMx_SR)

TIM2_IRQHandler这个中断指向可以在 “startup_stm32f40_41xx.s” 中查询到

void TIM2_IRQHandler(void)

{

if(TIM2 ->SR & 0X01) //说明引起了更新中断

{

TIM2 ->SR &=(~(1<<0)); //中断清零

//处理函数

//

}

}NVIC的配置方式

| CMSIS interrupt control function | Description | 功能说明 |

| void NVIC_SetPriorityGrouping(uint32_t priority_grouping) | Set the priority grouping | 进行分组设置详情看分组列表 |

| void NVIC_EnableIRQ(IRQn_t IRQn) | Enable IRQn | 启用中断,详情查看中断列表(入参:中断号) |

| void NVIC_DisableIRQ(IRQn_t IRQn) | Disable IRQn | 将中断禁止 |

| uint32_t NVIC_GetPendingIRQ (IRQn_t IRQn) | Return true (IRQ-Number) if IRQn is pending | 查看中断是否为挂起状态 如果 IRQn 处于挂起状态,则返回 true(IRQ 编号) |

| void NVIC_SetPendingIRQ (IRQn_t IRQn) | Set IRQn pending | 设置 IRQn 挂起 |

| void NVIC_ClearPendingIRQ (IRQn_t IRQn) | Clear IRQn pending status | 清除 IRQn 待处理状态 |

| uint32_t NVIC_GetActive (IRQn_t IRQn) | Return the IRQ number of the active interrupt | 返回活动中断的 IRQ 编号 |

| void NVIC_SetPriority (IRQn_t IRQn, uint32_t priority) | Set priority for IRQn | 设置 IRQn 的优先级(结合中断分组来进行赋值priority为4bit数值) |

| uint32_t NVIC_GetPriority (IRQn_t IRQn) | Read priority of IRQn | IRQn 的读取优先级 |

| void NVIC_SystemReset (void) | Reset the system | 重置系统 |

NVIC中断等级分组列表

中断NVIC分组等级列表

// (高两位) (低两位)

//________________ _______________________________

//| 组别 | 数值 | 抢占优先级 | 响应优先级 | AIRCR |

//| ---------------------------------------------- |

//| 0 | 7 | 0位 | 4位 | 111 |

//| ---------------------------------------------- |

//| 1 | 6 | 1位 | 3位 | 110 |

//| ---------------------------------------------- |

//| 2 | 5 | 2位 | 2位 | 101 |

//| ---------------------------------------------- |

//| 3 | 4 | 3位 | 1位 | 100 |

//| ---------------------------------------------- |

//| 4 | 3 | 4位 | 0位 | 011 |

//--------------------------------------------------

NVIC_SetPriorityGrouping(5); //程序写法将数值填入

F407拥有的中断号

//向量表查询数值

//#if defined (STM32F40_41xxx)

// CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

// CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

// CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

// CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

// EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

// TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

// TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

// TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

// TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

// TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

// TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

// TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

// I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

// I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

// I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

// I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

// SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

// SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

// USART1_IRQn = 37, /*!< USART1 global Interrupt */

// USART2_IRQn = 38, /*!< USART2 global Interrupt */

// USART3_IRQn = 39, /*!< USART3 global Interrupt */

// EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

// RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

// OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

// TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

// TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

// TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

// TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

// DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

// FSMC_IRQn = 48, /*!< FSMC global Interrupt */

// SDIO_IRQn = 49, /*!< SDIO global Interrupt */

// TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

// SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

// UART4_IRQn = 52, /*!< UART4 global Interrupt */

// UART5_IRQn = 53, /*!< UART5 global Interrupt */

// TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

// TIM7_IRQn = 55, /*!< TIM7 global interrupt */

// DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

// DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

// DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

// DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

// DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

// ETH_IRQn = 61, /*!< Ethernet global Interrupt */

// ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

// CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

// CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

// CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

// CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

// OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

// DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

// DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

// DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

// USART6_IRQn = 71, /*!< USART6 global interrupt */

// I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

// I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

// OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

// OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

// OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

// OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

// DCMI_IRQn = 78, /*!< DCMI global interrupt */

// CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

// HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

// FPU_IRQn = 81 /*!< FPU global interrupt */

//#endif /* STM32F40_41xxx */启动TIM2定时器中断

//开启中断向量,定时器2的中断向量号为28.可查询上表

NVIC_EnableIRQ(TIM2_IRQn); //使能全局中断

//等价于NVIC_EnableIRQ(28);对中断进行优先级设置

//设置抢占优先级(高二位)与响应优先级 (低二位) 例如要 抢占优先级是 2 响应优先级是 0 则值=0x80

NVIC_SetPriority(TIM2_IRQn,8);完整例程

/**

* @brief 初始化TIM2

*

* @note 由于APB1的时钟大小是42M 所以APB1的分频系数是4 (168/4=42) 当 APBx presc不等于1时

* 需要进行2倍频 所以TIM2的定时器时钟频率为84Mhz

*

* @retval None

*/

void TIM2_Init(u16 arr,u16 psc)

{

//使能时钟APB1

RCC ->APB1ENR |= (1<<0) ;

//使能TIM2计数器 1

TIM2 ->CR1 |=1<<0;

//设置预分频系数,

TIM2 ->PSC = psc-1;

//当ARPE寄存器=0 ARR寄存器被写值时,将立即更新到计数器寄存器中,马上进行计数。

//当ARPE寄存器=1 ARR寄存器被写值时,将数值放入自动重载活动寄存器中,等到更新事件出现时自动重载活动寄存器会将寄存器放入计数器寄存器中

TIM2 ->CR1 &= (~(1<<7));

//设置自动重装载值

TIM2 ->ARR = arr-1;

//开启定时器中断

TIM2 ->DIER |= 1<<0;

//TIM2 的中断进行分组

// (高两位) (低两位)

//________________ _______________________________

//| 组别 | 数值 | 抢占优先级 | 响应优先级 | AIRCR |

//| ---------------------------------------------- |

//| 0 | 7 | 0位 | 4位 | 111 |

//| ---------------------------------------------- |

//| 1 | 6 | 1位 | 3位 | 110 |

//| ---------------------------------------------- |

//| 2 | 5 | 2位 | 2位 | 101 |

//| ---------------------------------------------- |

//| 3 | 4 | 3位 | 1位 | 100 |

//| ---------------------------------------------- |

//| 4 | 3 | 4位 | 0位 | 011 |

//--------------------------------------------------

NVIC_SetPriorityGrouping(5);

//等价于 SCB ->AIRCR |=0X05<<8;

//开启中断向量,定时器2的中断向量号为28.可查询下表

NVIC_EnableIRQ(TIM2_IRQn); //使能全局中断

//等价于NVIC_EnableIRQ(28);

//设置抢占优先级(高二位)与响应优先级 (低二位) 例如要 抢占优先级是 2 响应优先级是 0 则值=0x80

NVIC_SetPriority(TIM2_IRQn,8);

}

/**

* @brief 中断处理函数

*

* @note

*

*

* @retval None

*/

void TIM2_IRQHandler(void)

{

if(TIM2 ->SR & 0X01) //说明引起了更新中断

{

LED0 = ~LED0;

TIM2 ->SR &=(~(1<<0));

}

}

//向量表查询数值

//#if defined (STM32F40_41xxx)

// CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

// CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

// CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

// CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

// EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

// TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

// TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

// TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

// TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

// TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

// TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

// TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

// I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

// I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

// I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

// I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

// SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

// SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

// USART1_IRQn = 37, /*!< USART1 global Interrupt */

// USART2_IRQn = 38, /*!< USART2 global Interrupt */

// USART3_IRQn = 39, /*!< USART3 global Interrupt */

// EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

// RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

// OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

// TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

// TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

// TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

// TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

// DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

// FSMC_IRQn = 48, /*!< FSMC global Interrupt */

// SDIO_IRQn = 49, /*!< SDIO global Interrupt */

// TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

// SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

// UART4_IRQn = 52, /*!< UART4 global Interrupt */

// UART5_IRQn = 53, /*!< UART5 global Interrupt */

// TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

// TIM7_IRQn = 55, /*!< TIM7 global interrupt */

// DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

// DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

// DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

// DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

// DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

// ETH_IRQn = 61, /*!< Ethernet global Interrupt */

// ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

// CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

// CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

// CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

// CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

// OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

// DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

// DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

// DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

// USART6_IRQn = 71, /*!< USART6 global interrupt */

// I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

// I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

// OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

// OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

// OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

// OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

// DCMI_IRQn = 78, /*!< DCMI global interrupt */

// CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

// HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

// FPU_IRQn = 81 /*!< FPU global interrupt */

//#endif /* STM32F40_41xxx */

4872

4872

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?