一、64QAM简介及设计思路

针对于振幅调制的原理可知,其所有信号的幅度值大小是相同的,想要用相位来表示更多的信息,就意味着星座图上相邻信号点的距离减小,则在相同噪声条件下,系统的误码率将增大。如何增加相邻点间的距离这个问题则被提出,容易想到的是增大圆周的半径,即增大信号的幅值,但这往往受到发射功率的限制。

于是想出了另外一种更好的设计思想:在不增加信号功率的基础上,可以通过调整某些点的幅值,重新安排信号点的位置,以增加相邻信号间的距离。即把ASK与PSK结合起来,振幅与相位联合键控的调制方式便被提出了。

针对于64QAM而言,它是将每6个比特映射到一个复数符号上,在星座图上有64个可能的点,每个点对应一个特定的幅度与相位组合。为此,可以先通过DDS产生两个正交的信号,然后将8种不同的幅值组合映射到对应正交信号上,再将两个信号相加,这样,整个64QAM映射及载波调制过程就完成了。

二、实现步骤及仿真结果

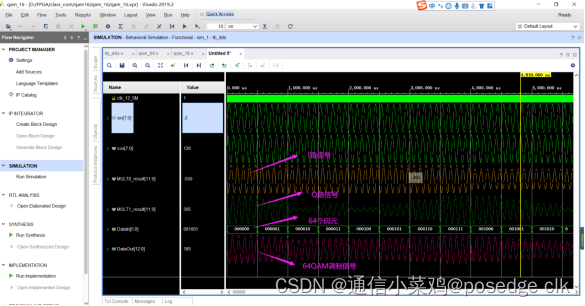

整个设计过程分成两个步骤:一个是利用DDS IP产生两个正交信号,另一个就是完成调制的映射过程(在此假设载波的频率为1MHz,数据的速率为100Kbps。),具体步骤如下:

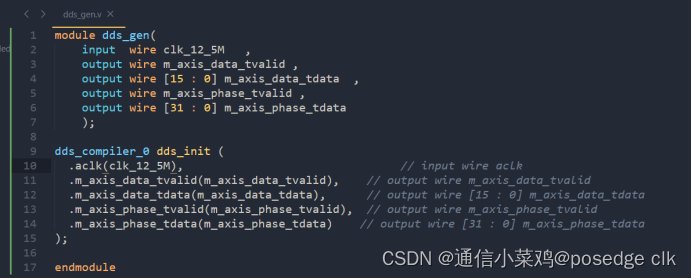

2.1 利用DDS IP核产生正交信号

DDS采用IP Core的形式实现,工作频率为12.5MHz,输出频率为1MHz,配置方式为固定频率输出。

打开vivado,搜索dds compiler ip核,并对其进行配置,配置关键界面如下:

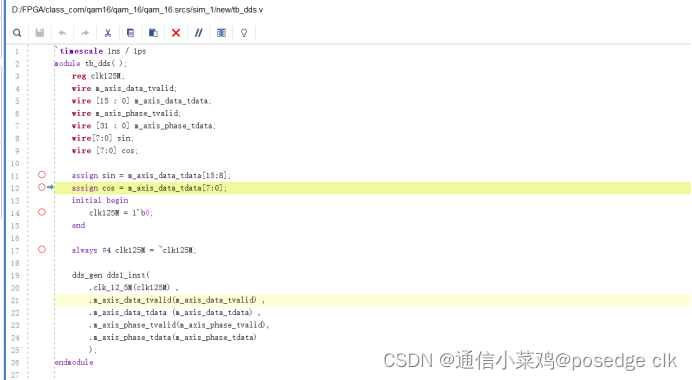

对应的测试以及仿真结果如下图所示,可以发现两个频率为1MHz的正交信号便被很好地产生了。

2.2 映射调制过程

//主要代码如下

//作者qq:1760704041

module qam_64(

input clk_12_5M ,//时钟

input [5:0] DataIn ,//输入

output [12:0] DataOut //输出16QAM信号

);

wire [7:0] sin;

wire [7:0] cos;

reg [3:0] MULT0_data;//对应1 3 5 7

reg [3:0] MULT1_data;

wire [11:0] MULT0_result;

wire [11:0] MULT1_result;

//dds 涉及到的变量

wire m_axis_data_tvalid;

wire [15 : 0] m_axis_data_tdata;

wire m_axis_phase_tvalid;

wire [31 : 0] m_axis_phase_tdata;

assign sin = m_axis_data_tdata[15:8];

assign cos = m_axis_data_tdata[7:0];

//DDS 产生正弦和余?

dds_gen dds1_inst(

.clk_12_5M(clk_12_5M) ,

.m_axis_data_tvalid(m_axis_data_tvalid) ,

.m_axis_data_tdata (m_axis_data_tdata) ,

.m_axis_phase_tvalid(m_axis_phase_tvalid),

.m_axis_phase_tdata(m_axis_phase_tdata)

);

//有符号相乘器

mult_64 u1_64 (

.CLK(clk_12_5M), // input wire CLK

.A(cos), // input wire [7 : 0] A

.B(MULT0_data), // input wire [3 : 0] B

.P(MULT0_result) // output wire [11 : 0] P

);

mult_64 u2_64 (

.CLK(clk_12_5M), // input wire CLK

.A(sin), // input wire [7 : 0] A

.B(MULT1_data), // input wire [3 : 0] B

.P(MULT1_result) // output wire [11 : 0] P

);

//有符号加法器

add_64 add_64 (

.A(MULT1_result), // input wire [11 : 0] A

.B(MULT0_result), // input wire [11 : 0] B

.CLK(clk_12_5M), // input wire CLK

.S(DataOut) // output wire [12 : 0] S

);

//格雷码映射

always @(DataIn)begin

case (DataIn)

//第一个16

6'b00_0000 :

begin

MULT0_data <= 4'b1001;

MULT1_data <= 4'b1001;

end

6'b00_0001 :

begin

MULT0_data <= 4'b1001;

MULT1_data <= 4'b1011;

end

6'b00_0011 :

begin

MULT0_data <= 4'b1001;

MULT1_data <= 4'b1101;

end

//省略·········

对应仿真波形如下图所示,可以发现64QAM调制被很好地实现了。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?