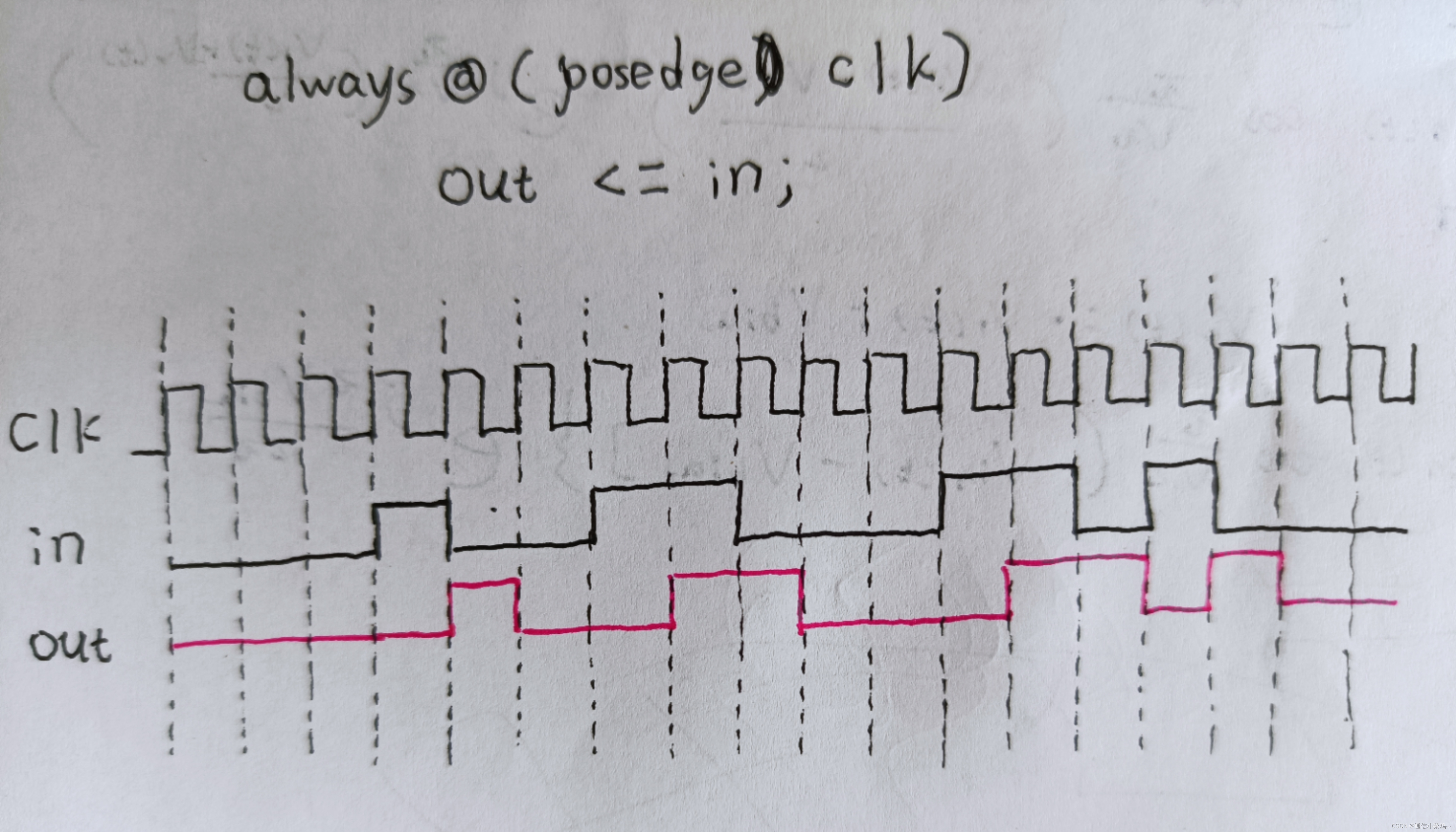

我们先来看下面的这张图,我们的语句是这样写的,在系统时钟上升沿到来的时候,将in的值通过非阻塞赋值的方式赋给输出out,这是的输出将会滞后in一个时钟周期,这是为什么呢?

通过这个输出波形我们也大致可以看出:时序逻辑电路中,每当系统时钟上升沿来临的时候,实际上采集到的是输入信号前一时刻的值。

归根到电路本身,其实可以发现是由于触发器本身的物理延迟所导致的。以D触发器为例:

在系统时钟上升沿到来的时候,这时数据D想立即更新传入到输出Q端,但由于D触发器内部的物理连线以及上一级触发器的Q传到这一级D的时间,此时的Q并不能被直接更新成最新的数据输入,因此此时刻所采集到的数据其实是上一时刻传入的D值 ,这也就造成了在时序逻辑电路中,输出会滞后与输入一个时钟节拍的原因。

6625

6625

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?