目录

ARM-translation table walk

本文主要讨论

1.MMU查询页表的过程。

2.页表的解析。

3.页表属性等等。

qcom sm8350平台的相关配置

cnfig上看:

CONFIG_ARM64_4K_PAGES=y

CONFIG_ARM64_VA_BITS_39=y

CONFIG_ARM64_VA_BITS=39

CONFIG_ARM64_PAGE_SHIFT=12 //和4k的页大小是匹配的

CONFIG_PGTABLE_LEVELS=3

从config上我们可以获取一下信息

1.寻址是39位的。

2.采用的page level是3。

3.page granule是4k。

qcom sm8350 page levels and translation gurad size

Arm支持的最大寻址空间为48位 ,qcom目前va是39位.

最多可以支持4级页表.qcom用的是3级.

页面粒度为4k,16k,64k.qcom用的是4k.

page level

当page level等于4的时候,映射关系是PGD(L0)—>PUD(L1)—>PMD(L2)—>Page table(L3)-→page.

当page level等于3的时候,没有PUD,这时候映射关系是PGD(L1)—>PMD(L2)—>Page table(L3)-→page。

参考右侧代码的实现,计算方法((PAGE_SHIFT - 3) * (4 - (n)) + 3).

1.每个index是9位。

2.由于每个index是9位,所以每个页表中有512个项,所以每个页表的大小是4K。

3.offset是12 位对应4K的page。

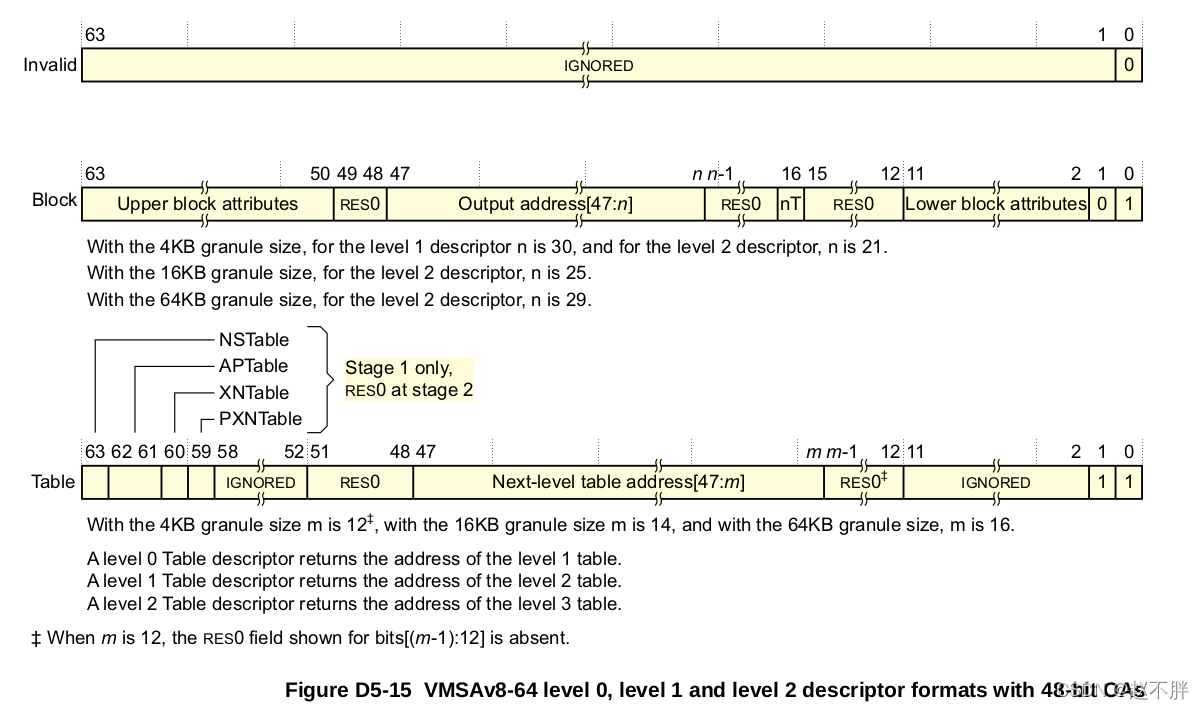

VMSAv8-64 translation table format descriptors

Translation table中的描述符可能有四种情况:

(1)是table descriptor,指向下一级的Translation table

(2)是page descriptor,指向一个PAGE size的地址区域

(3)是block descriptor,指向一个Block size的地址区域

(4)无效描述符

各个translation level支持的block属性,L3不支持block描述符

| granule | 说明 |

|---|---|

| 4KB | level0 转换表不支持Block描述符 level 1 Block转换表k描述了相关的1GB输入地址范围的映射 level 2 Block转换表k描述了相关的2MB输入地址范围的映射16KBlevel0 、level1转换表不支持Block描述符 |

| 16KB | level0 、level1转换表不支持Block描述符 level 2 Block转换表k描述了相关的32MB输入地址范围的映射 |

| 64KB | 不支持 level0 查找 如果实现了ARMv8.2-LPA : (1) level 1 Block转换表k描述了相关的4TB输入地址范围的映射; (2) level 2 Block转换表描述了相关的512MB输入地址范围的映射; 如果未实现了ARMv8.2-LPA : (1) level 1 转换表不支持Block描述符; (2) level 2 Block转换表描述了相关的512MB输入地址范围的映射 |

L0-L2的页表描述符

| 描述符类型 | bit[1] | bit[0] | 说明 |

|---|---|---|---|

| Invalid | - | 0 | 无效描述符,任何访问该地址的尝试都会生成转换错误 |

| Block | 0 | 1 | 提供内存块的基地址和该内存区域的属性 |

| Table | 1 | 1 | 提供下一级转换表的地址,对于阶段1的转换,提供该转换的一些属性 |

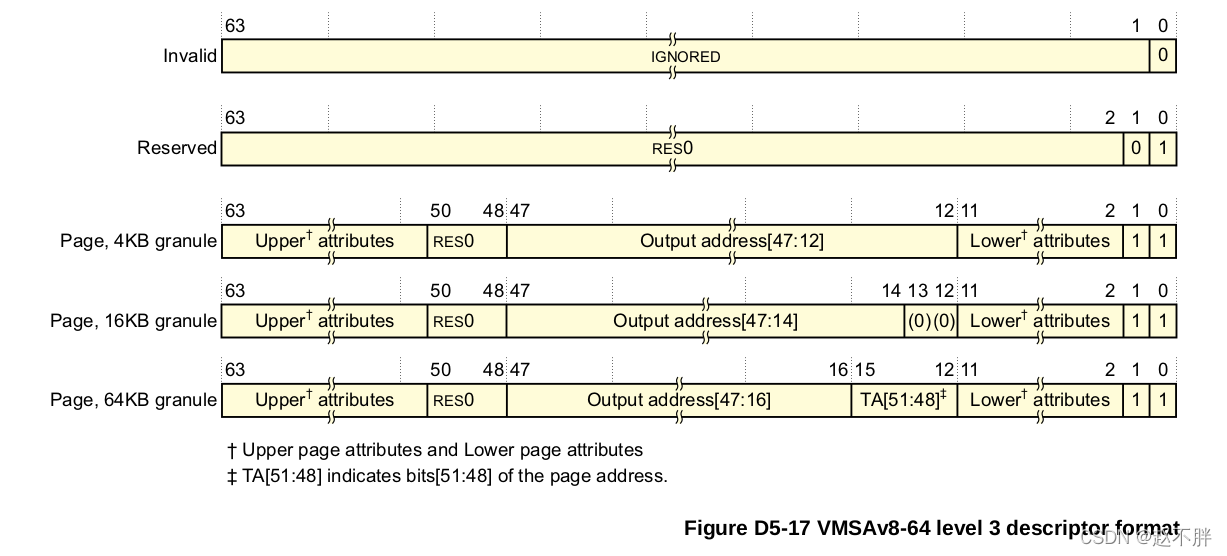

L3的页表描述符

| 描述符类型 | bit[1] | bit[0] | 说明 |

|---|---|---|---|

| Invalid | - | 0 | 无效描述符,任何访问该地址的尝试都会生成转换错误 |

| Reserved | 0 | 1 | 保留 |

| Page | 1 | 1 | 提供4KB、16KB或64KB内存页的地址和属性 |

Memory attribute fields in the VMSAv8-64 translation table format descriptors

Table descriptor:

stage 2 translations 不包含任何属性字段, stage 1 translation这些属性定义了下一个查找级别的属性.

Block and page descriptors:

Stage 1 和stage 2 translations的定义内存属性的描述符意义不同

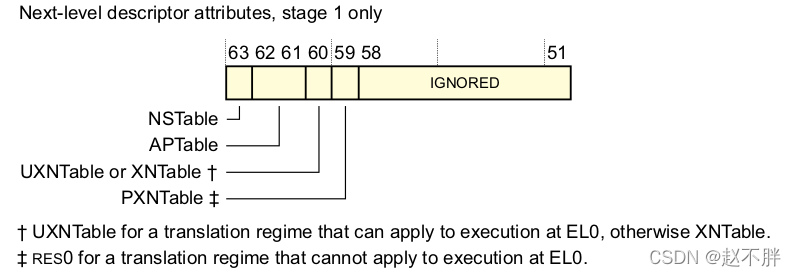

Next-level attributes in stage 1 VMSAv8-64 Table descriptors–Table descriptor

在阶段1转换的表描述符中,描述符的位[63:59]定义了下一级的属性,转换表[58:51]位是IGNORED的:

| 字段 | bit 位 | 说明 |

|---|---|---|

| NSTable(Non-secure) | [63] | 安全或非安全内存访问的分层控制: 该位指示描述符中标识的表是在安全存储器中还是在非安全存储器中。对于从安全状态进行的访问,NSTable位的含义是: (1) NSTable == 0 :定义的表地址在安全PA空间中 (2) NSTable == 1 :定义的表地址在非安全PA空间中 |

| APTable(Access permissions) | [62:61] | 数据访问权限的分层控制: APTable[1:0] 00: 在后续查找级别中对权限没有影响。 01: 不允许在EL0上进行访问. 10: 不允许在任何Exception level进行写访问。 11: 不允许在任何Exception level进行写访问, EL0不允许读取访问. |

| UXNTable or XNTable (Execute-never or Unprivileged execute-never table ) | [60] | 指令获取的分层控制: UXNTable或XNTable限制了execute-never控制: 1.当XNTable位的值为1时,在所有后续查找级别中UXN位均被视为1。 2.当UXNTable位的值为1时,XN位在所有后续查找级别中均被视为1。 3.当UXNTable或XNTable位的值为0时,该位无效。 Stage 1 支持两个VA ranges :这个字段是UXNTableStage 1 支持一个VA ranges :这个字段是XNTable |

| PXNTable (privileged execute-never table ) | [59] | 指令获取的分层控制: 对于适用于EL0和更高异常级别的转换机制,PXNTable限制了PXN控制: 1.当PXNTable的值为1时,在所有后续查找级别中,PXN位均被视为1,不管该位的实际值如何。 2.当PXNTable的值为0时,它无效。 |

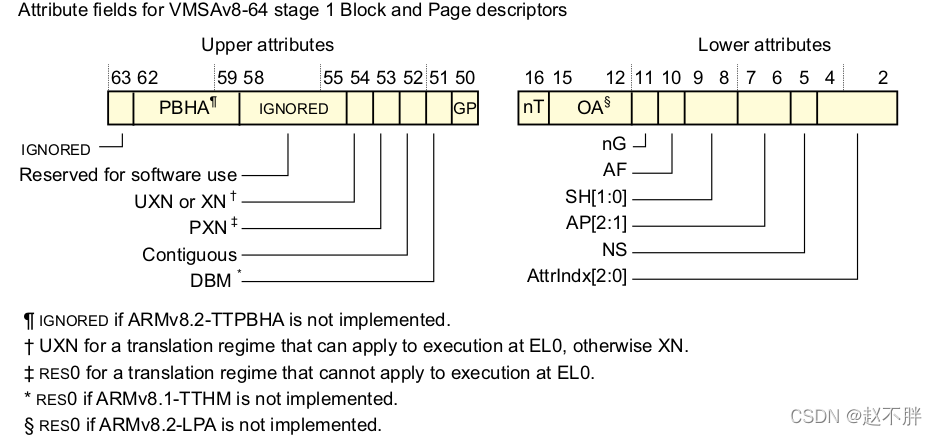

Attribute fields in stage 1 VMSAv8-64 Block and Page descriptors-- stage 1 Block and page descriptors

Block和 Page descriptors 内存属性被分为 upper block 和 lower block

| 字段 | bit位 | 说明 |

|---|---|---|

| PBHA(Page-based Hardware Attributes) | [62:59] | 基于页面的硬件属性位。如果未实现ARMv8.2- TTPBHA,这些位将被忽略。 ARMv8.2-TTPBHA, Translation table page-based hardware attributes --这个没有看过实现的. |

| XN or UXN(Execute-never or Unprivileged execute-never) | [54] | executor-never或者无特权的executor-never字段 指令执行的访问权限 Execute-never controls决定是否可以从存储区执行指令。这些控件是: 描述符bit[54]定义为UXN,仅用于stage 1支持两个VA,该字段仅适用于EL0处的执行。值为0表示此控件允许执行. 描述符bit[54]定义为XN,stage 1支持1个VA.支持Stage 2 translations(未实现ARMv8.2-TTS2UXN时) |

| PXN(Privileged execute-never) | [53] | 特权execute-never字段 指令执行的访问权限 描述符bit[53],仅用于stage 1支持两个VA.stage 1转换仅支持单个VA范围的转换方案的情况,PXN为RES0. 该字段仅适用于高于EL0的异常级别的执行。值为0表示此控件允许执行。 只有在转换stage1能够支持两个VA范围时,该字段才有效。stage1只能支持一个VA范围时值为RES0 |

| Contiguous | [52] | 连续位: 提示位,指示translation table是一个或多个连续集之一,可能会缓存在单个TLB条目中. 当连续位的值为1时,表示该条目是指向连续输出地址范围的多个相邻转换表条目之一。 |

| DBM(Dirty Bit Modifier) | [51] | 脏位修饰符: 指示是否修改了内存的页面或部分 |

| GP(Guarded Page) | [50] | 保护页: 1.如果实现了ARMv8.5-BTI,则该字段出现在阶段1块和页面转换表中条目。否则,此字段为RES 0。 2.在阶段2块和页面转换表条目中,此字段为RES0。 ARMv8.5-BTI,大家有空可以研究. |

| nT | [16] | Block转换条目: 如果实现了ARMv8.4-TTRem,则该字段出现在第1阶段块转换表条目中。 否则,此字段为RES 0。 |

| nG(not global) | [11] | 位非全局位: 如果使用此描述符的查找缓存在TLB中,请确定TLB条目是适用于所有ASID值,还是仅适用于当前ASID值 |

| AF(Access flag) | [10] | 访问标志位: 转换表描述符中的AF位是访问标志。相应转换表描述符中的访问标志设置为0之后,访问标志指示何时第一次访问内存的page或section. |

| SH(Shareability field) | [9:8] | 共享性字段: 用来指示一个内存位置对于一些处理器是否是可共享的。共享意味着需要硬件保证一个内存位置中的内容对一定范围内可访问该位置的多个处理器是一致。Shareability属性有Non-shareable、InnerShareable和Outer Shareable三个选项 使用VMSAv8-64转换表格式时,块或页面转换表描述符中的SH [1:0]字段指定相应内存区域的Shareability属性。SH[1:0]/适用于normal memory 00:Non-shareable 01:Reserved 10:Outer Shareable 11:Inner Shareable Non-shareable,Outer Shareable,Inner Shareable涉及到不同属性的指令和数据在cache和内存中存储的位置的,以及cache和内存的数据同步等等比较复杂,大家有兴趣可以自行研究. |

| AP[2:1](Access flag) | [7:6] | 数据访问权限位: 在VMSAv8-64中,对于适用于EL0和更高异常级别的转换机制,AP [2:1]位控制stage 1的数据访问权限. AP[2]:在只读和读/写访问之间选择。 AP[1]:在应用程序级别(EL0)控制和更高的异常级别控制之间进行选择。 为数据访问提供了四个权限设置:1.在所有级别均为只读。2.各个级别的读/写。3.高异常级别的只读状态,不能由在EL0执行的软件进行访问。4.高异常级别进行读/写,无法通过在EL0执行的软件进行访问。 |

| NS(Non-secure) | [5] | Non-secure位: 对于从安全状态访问内存,指定输出地址是在安全地址映射中还是在非安全地址映射中:(1) NS == 0 访问安全PA空间(2) NS == 1 访问非安全PA空间 。 对于从非安全状态进行的存储器访问,该位为RES 0,被PE忽略。 注: 同Table descriptor 的NSTable功能相同? |

| AttrIndx[2:0](Stage 1 memory attributes index) | [4:2] | stage1内存属性索引字段: 用于MAIR_ELx |

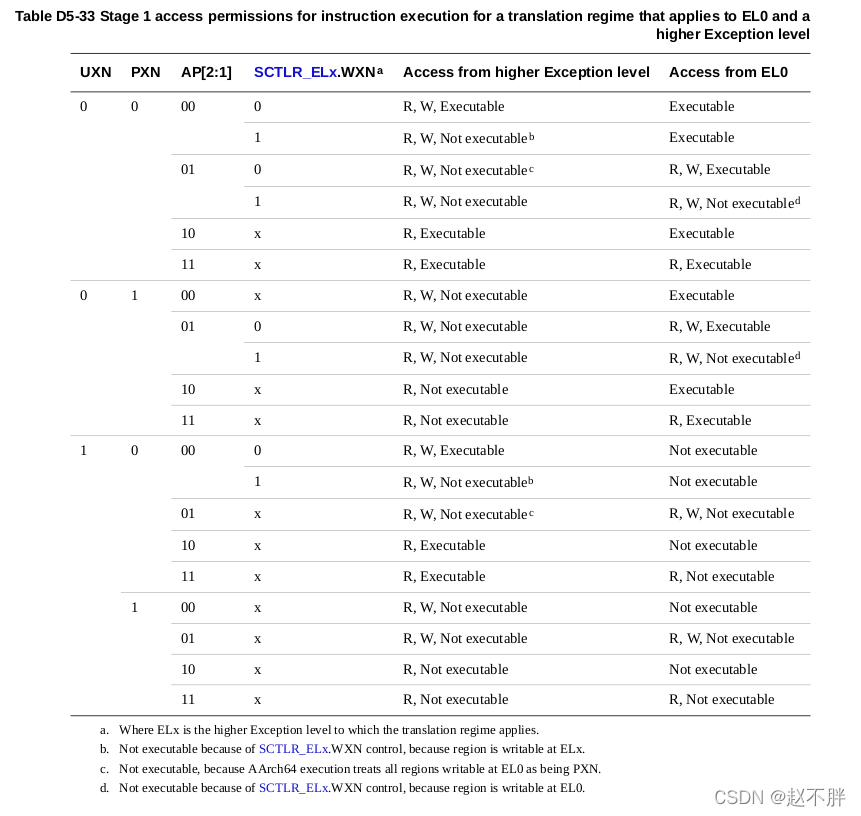

下面看一下UXN,XN,PXN,AP作用在不同的exception level上,内存的access状态:

其中对于SCTLR_ELx.WXM设置为1的时候.对于从在EL1或EL0执行的软件进行访问,在EL1&0转换方式中可写的任何区域都被强制为XN。

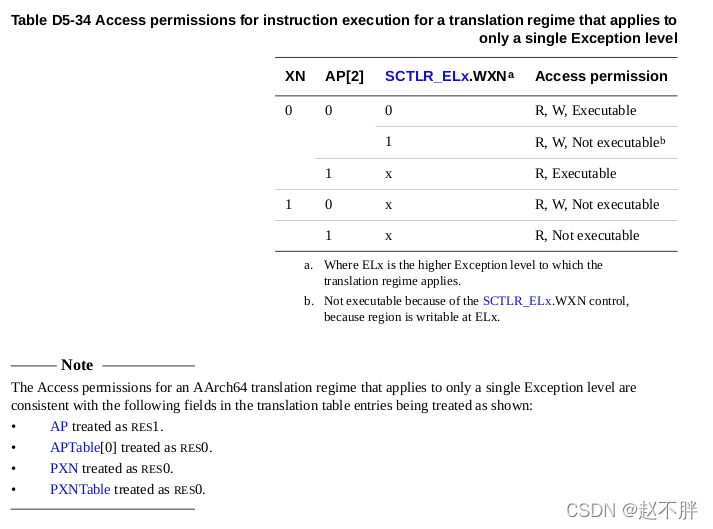

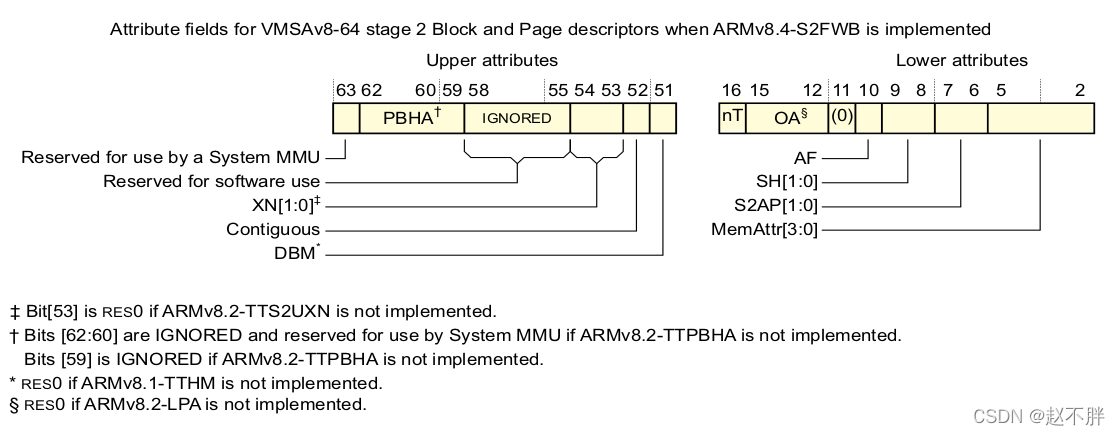

Attribute fields in stage 2 VMSAv8-64 Block and Page descriptors-- stage 2 Block and page descriptors

stage 2 同样Block和 Page descriptors 内存属性被分为 upper block 和 lower block.

| 字段 | bit位 | 说明 |

|---|---|---|

| PBHA[3:1](Page-based Hardware Attributes) | [62:60] | 基于页面的硬件属性位。如果未实现ARMv8.2- TTPBHA,这些位将被忽略。 ARMv8.2-TTPBHA, Translation table page-based hardware attributes --这个没有看过实现的. |

| PBHA[0] | [59] | 基于页面的硬件属性位。如果未实现ARMv8.2- TTPBHA,这些位将被忽略。 ARMv8.2-TTPBHA, Translation table page-based hardware attributes --这个没有看过实现的. |

| XN1:0 | [54:53] | execute-never bits[54:53]: 未实现ARMv8.2-TTS2UXN时,用于Stage 2 translations,否则为RES0. XN[1] bit XN[0] bit: 00: stage 2的控制允许在EL1和EL0处执行 01: stage 2的控制不允许在EL1上执行,但允许在EL0上执行 10:stage 2的控制不允许在EL1或EL0处执行 11:stage 2的控制允许在EL1上执行,但不允许在EL0上执行 |

| Contiguous | [52] | 连续位: 提示位,指示translation table是一个或多个连续集之一,可能会缓存在单个TLB条目中.当连续位的值为1时,表示该条目是指向连续输出地址范围的多个相邻转换表条目之一 |

| DBM(Dirty Bit Modifier) | [51] | 脏位修饰符: 指示是否修改了内存的页面或部分 |

| nT | [16] | Block转换条目: 如果实现了ARMv8.4-TTRem,则该字段出现在第1阶段块转换表条目中。 否则,此字段为RES 0。 |

| AF(Access flag) | [10] | 访问标志位: 转换表描述符中的AF位是访问标志。相应转换表描述符中的访问标志设置为0之后,访问标志指示何时第一次访问内存的page或section. |

| SH(Shareability field) | [9:8] | 使用VMSAv8-64转换表格式时,块或页面转换表描述符中的SH [1:0]字段指定相应内存区域的Shareability属性。 SH[1:0]/适用于normal memory 00:Non-shareable 01:Reserved 10:Outer Shareable 11:Inner Shareable |

| S2AP[2:1](Access flag) | [7:6] | Stage 2 数据访问权限位: 在安全或非安全EL1&0中,当启用EL2转换机制时,当启用阶段2地址转换时,阶段2转换表描述符中的S2AP字段定义数据访问权限。 00: none,任何访问都会产生权限错误。 01:Read-only 10:Write-only 11:Read/write |

| MemAttr | [5:2] | stage2内存属性: 当MemAttr[3:2] == 0b00/device memory MemAttr[1:0] 00:Device-nGnRnE memory 01:Device-nGnRE memory 10:Device-nGRE memory 11:Device-GRE memory 当MemAttr[3:2] != 0b00/normal memory 00:Reserved 01:Inner Non-cacheable 10:Inner Write-Through Cacheable 11:Inner Write-Back Cacheable |

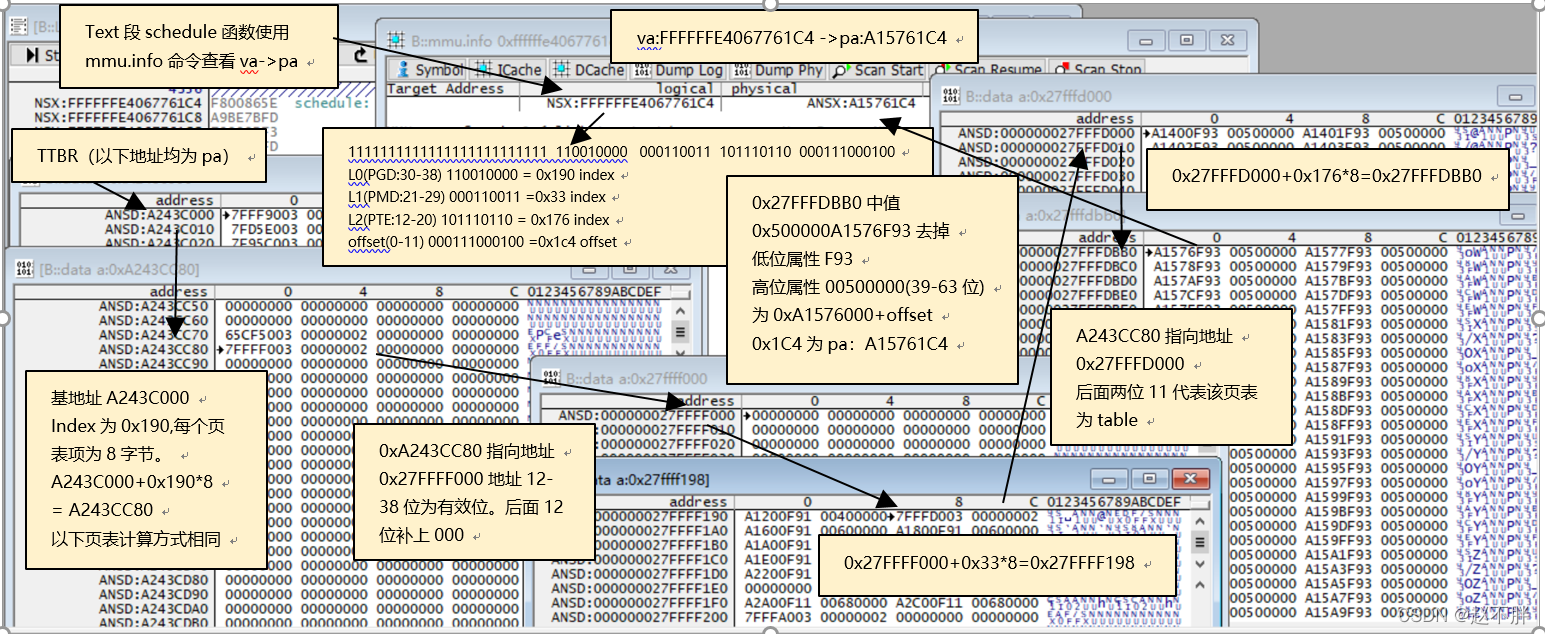

trace32解析的qcom 8350的一个 translation table walk

trace32指令mmu.info 0xFFFFFFE4067761C4 找到对应的物理地址为0xA157614.然后我们走一遍translation table walk,找到 一样的物理地址即可.

该地址为kernel的代码段。

查看内核空间的地址,EL1的基地寄存器:TTBR1_EL1。

translation table中的地址都对应PA。

IA为VA-0xFFFFFFE4067761C4, L1(PGD) 的index为0x190,L2(PMD)的index为0x33,L3(PTE)的index为0x176,offset为0x1c4 。

其中Table descriptor为NSTable 0 kernel的代码段在非安全状态进行的存储器访问中该位无意义 ,APTable 00在后续查找级别中对权限没有影响,UXNTable/XNTable 0不影响后续PXN/XN位置,PXNTable 0不影响后续PXN位置 。

其中page descriptors高位属性,UXN/XN 为1 el0不可以执行,PXN为0 el1可以执行 , Contiguous 为1连续, DBM为0 非脏叶。

其中page descriptors 低位属性, nG 1非全局位,有自己的ASID–这个感觉有点毁三观一直以为kernel的地址应该是全局的。

AF 1表示被访问过,SH 11为 Inner Shareable.AP 10加上UXN和PXN之后为 EL1有read和exe权限, EL0没有任何权限 。NS 0 非安全状态进行的存储器访问无意义,.AttrIndex 100对应MAIR_EL1中第四个attr,最后两位11代表页。

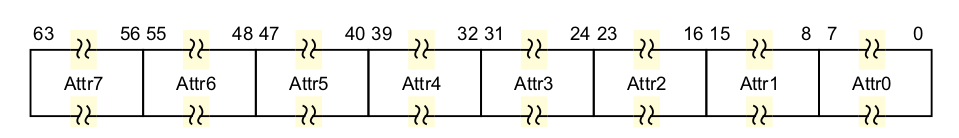

MAIR_EL1(Memory Attribute Indirection Register (EL1) ),支持配8个attr ,qcom 的 设置为 0x000000FF440C0400。

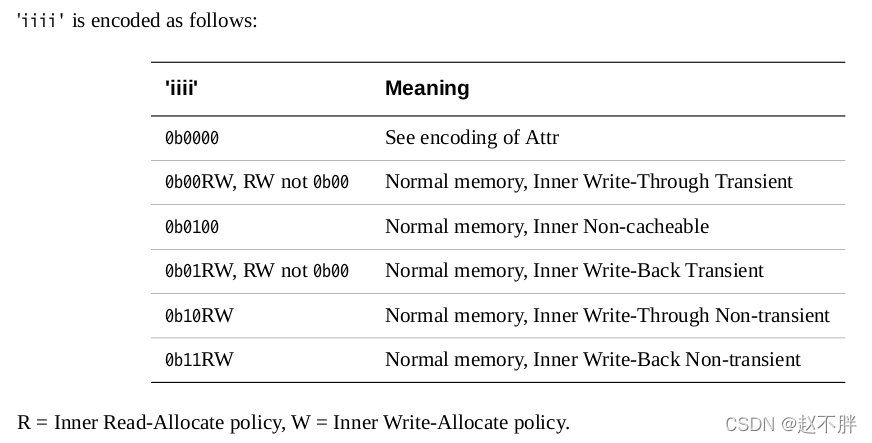

Attrx的定义如下:

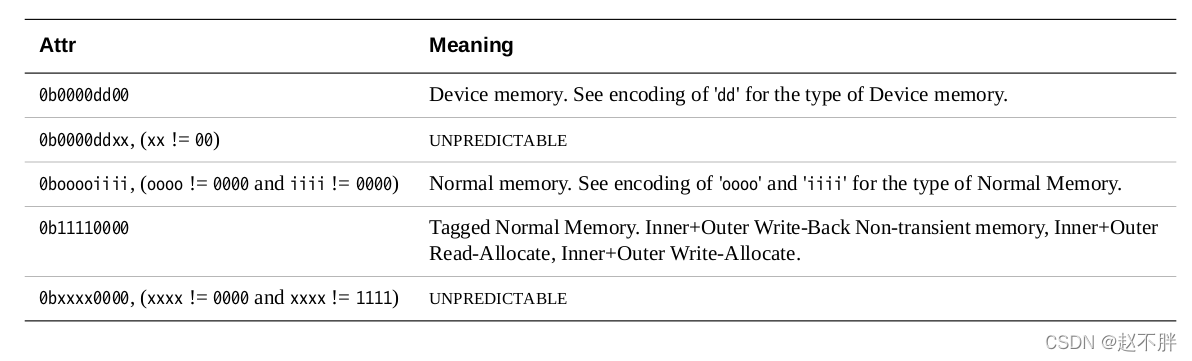

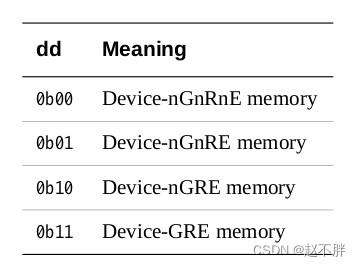

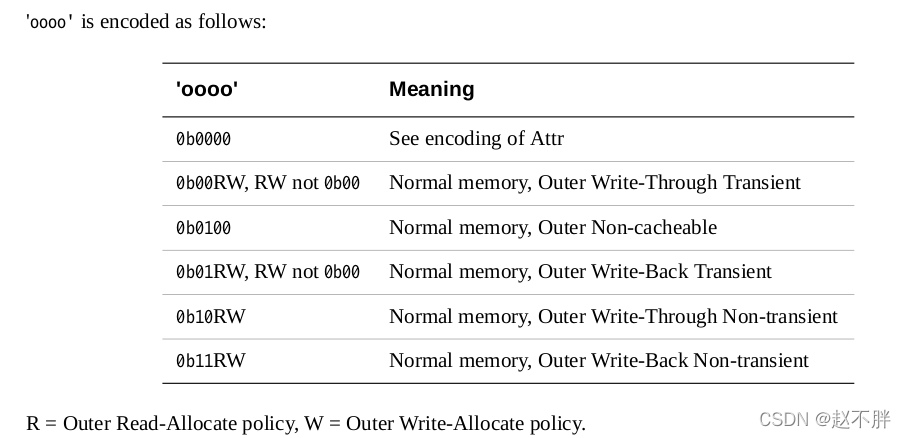

各个bit位的具体含义:

memory分成两个大类:normal memory和device

for device memory:

对于device type,其总是non cacheable的,而且是outer shareable,因此它的attribute不多,主要有下面几种附加的特性:

(1)Gathering 或者non Gathering (G or nG)。这个特性表示对多个memory的访问是否可以合并,如果是nG,表示处理器必须严格按照代码中内存访问来进行,不能把两次访问合并成一次。例如:代码中有2次对同样的一个地址的读访问,那么处理器必须严格进行两次read transaction。

(2)Re-ordering (R or nR)。这个特性用来表示是否允许处理器对内存访问指令进行重排。nR表示必须严格执行program order。

(3)Early Write Acknowledgement (E or nE)。PE访问memory是有问有答的(更专业的术语叫做transaction),对于write而言,PE需要write ack操作以便确定完成一个write transaction。为了加快写的速度,系统的中间环节可能会设定一些write buffer。nE表示写操作的ack必须来自最终的目的地而不是中间的write buffer。

for normal memory:

shareable domain的概念。如何划分shareable domain是和系统设计相关,我们假设一个系统的domain分配如下: (1)所有的cpu core属于一个inner shareable domain (2)所有的cpu core和dma controller属于一个outer shareable domain 在ARM architecture中,对一个normal memory location而言,是否是coherent是和它的页表中的shareability attribute的设定相关。 (1)non-shareable。根本不会再多个agent之间共享,不存在coherent的问题。 (2)inner-shareable。说明inner shareable domain中的所有的agent在对该内存进行数据访问的时候,硬件会保证coherent。 (3)outer-shareable。说明outer shareable domain中的所有的agent在对该内存进行数据访问的时候,硬件会保证coherent。

Write-through(直写模式)在数据更新时,同时写入缓存Cache和后端存储。此模式的优点是操作简单;缺点是因为数据修改需要同时写入存储,数据写入速度较慢。Write-back(回写模式)在数据更新时只写入缓存Cache。只在数据被替换出缓存时,被修改的缓存数据才会被写到后端存储。此模式的优点是数据写入速度快,因为不需要写存储;缺点是一旦更新后的数据未被写入存储时出现系统掉电的情况,数据将无法找回。

在有cache的单机系统中,通常有两种写策略:write through和write back。这两种写策略都是针对写命中(write hit)情况而言的:write through是既写cache也写main memory;write back是只写cache,并使用dirty标志位记录cache的修改,直到被修改的cache 块被替换时,才把修改的内容写回main memory。那么在写失效(write miss)时,即所要写的地址不在cache中,该怎么办呢?一种办法就是把要写的内容直接写回main memory,这种办法叫做no write allocate policy;另一种办法就是把要写的地址所在的块先从main memory调入cache中,然后写cache,这种办法叫做write allocate policy。

本文详细探讨了ARM64架构在qcomsm8350平台上的页表配置,包括寻址位数、页表级别和页大小。介绍了页表的各级别描述符,如table、block和page descriptor,以及它们在不同异常级别上的访问权限控制。此外,还讲解了内存属性字段,如非安全、访问权限、执行禁止等。通过对translation table walk的trace32解析,展示了实际的地址映射过程。

本文详细探讨了ARM64架构在qcomsm8350平台上的页表配置,包括寻址位数、页表级别和页大小。介绍了页表的各级别描述符,如table、block和page descriptor,以及它们在不同异常级别上的访问权限控制。此外,还讲解了内存属性字段,如非安全、访问权限、执行禁止等。通过对translation table walk的trace32解析,展示了实际的地址映射过程。

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?