学习时钟树要配合STM32CubeMX里的Clock Configuration的效果更加。

刚开始只捧着文字,看得很吃力,后来打开STM32CubeMX,结合网上的保姆教程,点亮一个灯以后,就豁然开朗了。然后再回来看火哥的文档,就非常清晰了。

确定晶振

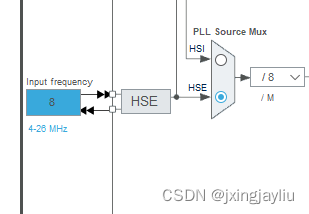

HSE 是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从 4-26MHZ 不等。

根据自己手里的板子,确定晶振的大小

HSE

HSE 是高速的外部时钟信号

当使用有源晶振时,时钟从 OSC_IN 引脚进入,OSC_OUT 引脚悬空;

当选用无源晶振时,时钟从OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。

锁相环PLL

什么是PLL

-

来自chat-gpt

PLL是锁相环(Phase Locked Loop)的缩写,它是一种常用的电路结构,用于生成高稳定性和高精度的时钟信号。在STM32系列微控制器中,PLL通常被用来将内部RC振荡器或外部晶体振荡器产生的较低频率时钟信号转换为更高频率的时钟信号,以满足各种外设模块和CPU的高速计时和通信需要。

具体来说,STM32的PLL电路包括一个VCO(Voltage Controlled Oscillator,电压控制振荡器),一个相频比(N)和一个时钟分频器(M、P、Q),其中:

- VCO通过改变输入电压的大小来调节输出频率,可以产生比输入频率更高的输出频率,通常频率范围为50MHz到400MHz。

- 相频比(N)用于控制VCO的倍频系数,即将输入时钟信号乘上N倍。

- 时钟分频器(M、P、Q)用于将VCO输出的高频时钟信号分频为不同的频率,以适应不同外设模块和CPU的需求。具体来说,M用于将VCO输出时钟进行整数分频,得到PLL输出时钟HCLK;P用于将HCLK进一步分频,得到APB1总线时钟PCLK1;Q用于将HCLK进一步分频,得到APB2总线时钟PCLK2。

通过精确控制PLL的输入时钟、相频比和分频系数等参数,可以实现高稳定性、高精度和低抖动的时钟信号,满足各种高速通信和计时要求。同时需要注意的是,由于PLL的复杂性和灵敏性,其在设计和使用过程中需要仔细考虑时钟质量、电源稳定性、布线规划等因素,以确保系统性能和可靠性。

-

来自文档

PLL 的主要作用是对时钟进行倍频,然后把时钟输出到各个功能部件。PLL 有两个,一个是主PLL,另外一个是专用的 PLLI2S,他们均由 HSE 或者 HSI 提供时钟输入信号。

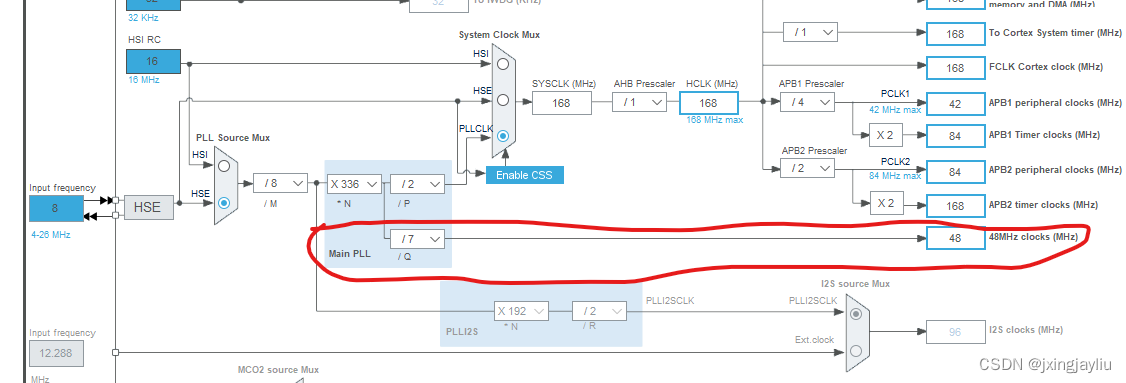

主PLL/Main PLL

主PLL有两路时钟输出

- PLLCLK

- 系统时钟

- F407最高168M

- USBCLK

- USB OTG FS 的时钟(48M)

- RNG 和 SDIO 时钟(<=48M)

PLLL2S

专用的 PLLI2S 用于生成精确时钟,给 I2S 提供时钟。

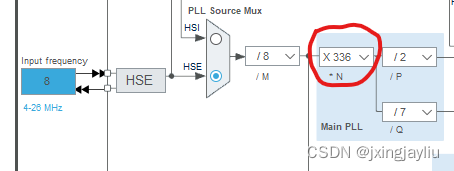

PLL时钟输入分频因子M

- HSE经过PLL时钟输入分频因子M分频后,成为VCO的时钟输入,即VCOCLK_IN;

- VCOCLK_IN处于1-2M之间。

VCO倍频因子N

- VCO 输入时钟经过 VCO 倍频因子 N 倍频之后,成为 VCO 时钟输出,即VCOCLK_OUT;

- VCOCLK_OUT必须在 192~432M之间。

PLLCLK 分频因子 p

- p 可以取值 2、4、6、8;

- 经过分频因子p,得到PLLCLK。

USB OTG FS/RNG/SDIO 时钟分频因子 Q

- Q 可以取值 4~15

- USB OTGFS 必须使用 48M;

- 使用STM32CUBEMX配置时钟树的时候,如果没有配置USB,则Q值无法修改

分频因子 R

F446 才有,F407 没有

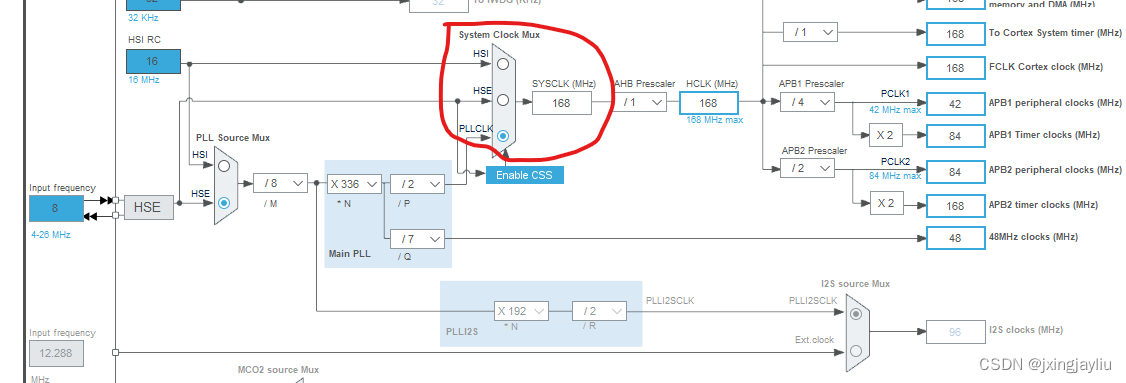

系统时钟 SYSCLK

-

系统时钟来源可以是:HSI、PLLCLK、HSE

-

如果系统时钟是由 HSE 经过 PLL 倍频之后的 PLLCLK 得到,当 HSE 出现故障的时候,系统时钟会切换为 HSI=16M,直到 HSE 恢复正常为止。

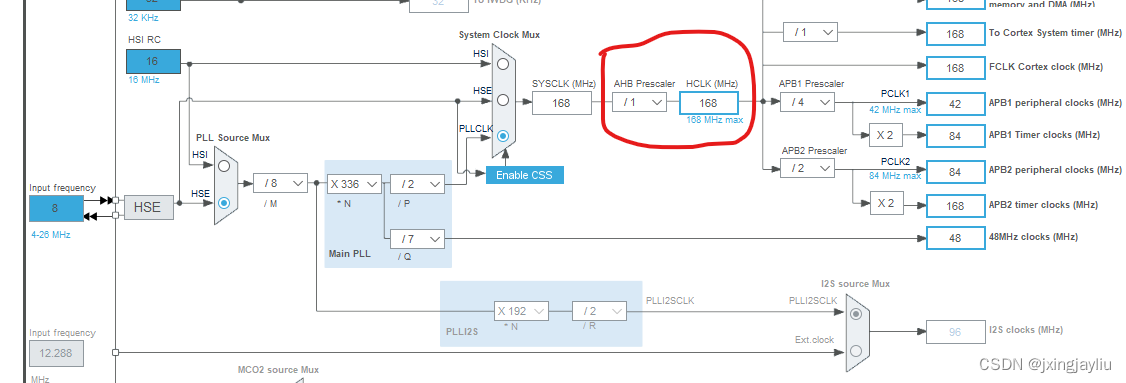

AHB总线时钟HCLK

- 系统时钟 SYSCLK 经过 AHB 预分频器分频之后得到时钟叫 AHB 总线时钟,即 HCLK,分频因子可以是:[1,2,4,8,16,64,128,256,512];

- 片上大部分外设的时钟都是经过 HCLK 分频得到

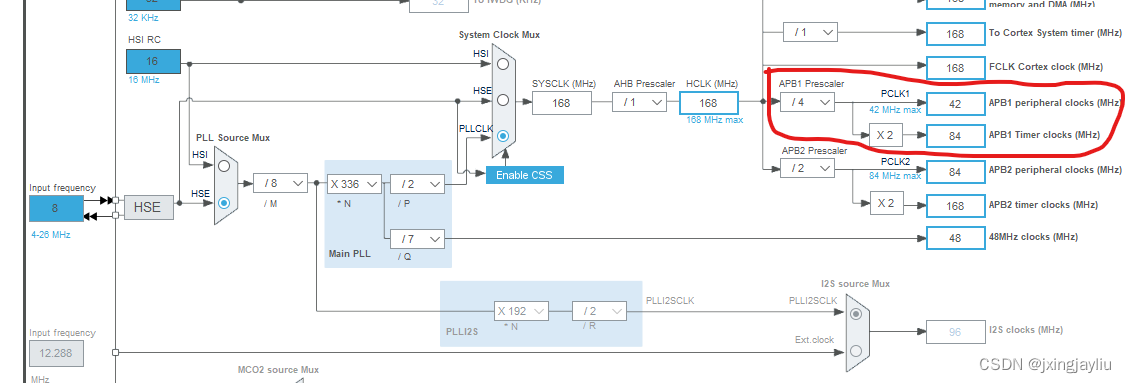

APB1 总线时钟 PCLK1

- APB1 总线时钟 PCLK1 由 HCLK 经过低速 APB 预分频器得到,分频因子可以是:[1,2,4,8,16];

- PCLK1 属于低速的总线时钟,最高为 42M,片上低速的外设就挂载到这条总线上,比如 USART2/3/4/5、SPI2/3,I2C1/2 等。

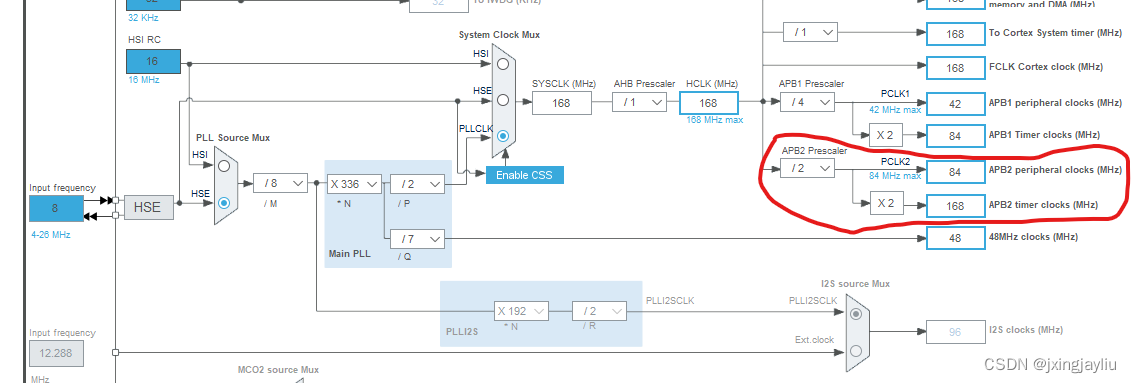

APB2 总线时钟 PCLK2

- APB2 总线时钟 PCLK2 由 HCLK 经过高速 APB2 预分频器得到,分频因子可以是:[1,2,4,8,16];

APB2 总线时钟 PCLK2

至此,整个轮廓基本上就有了,更深入的理解,就交给实践和时间了。

1659

1659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?