目录

前言

这是一个项目笔记,是我第一次用FPGA系统的做这个项目的设计。在B站特权同学《Verilog边码边学》“超声波测距设计”那四堂课的基础上,我加入了均值滤波、数码管显示、按键触发等功能,从而实现了超声波的一键测距,在本篇结尾处我会附上特权同学的视频教学地址,再次感谢特权老师的课程!

一、项目需求

设计一个一键测距的装置,使用Xilinx FPGA实现,该系统硬件由FPGA、超声波测距模块、4位数码管模块、按键以及蜂鸣器构成。

系统工作流程如下:在超声波探头n厘米处放置好物块,按下板载按键后超声波测距模块工作,测得的距离在数码管模块上以cm为单位显示,等待数据稳定后超声波模块停止工作,并且让蜂鸣器“滴滴滴”响3声,此时测得探头离物块的距离数据N,拿掉物块后数码管数据不会变化,直到再次摁下按键后超声波模块启动,数据才会继续变化。

关于测量指标,因为超声波测距模块有+/-3mm的测量误差,所以测量数据N在实际数据n的+/-3mm之内都算达到指标。

二、器件清单

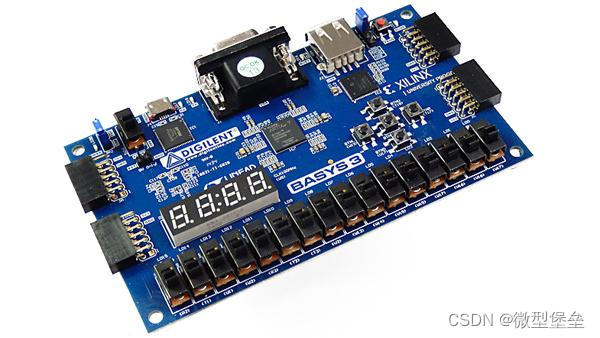

1.BASYS3开发板

板载的资源很丰富,在本项目中会用到4位数码管模块和按键这两个板载外设。

2.超声波测距模块

3.3V有源蜂鸣器

特别注意,是3V而不是5V蜂鸣器!因为我买的是5V,结果上电后工作时蜂鸣声太小了(大哭),因为板子输出的高电平为3.3<5V,导致电压不够。

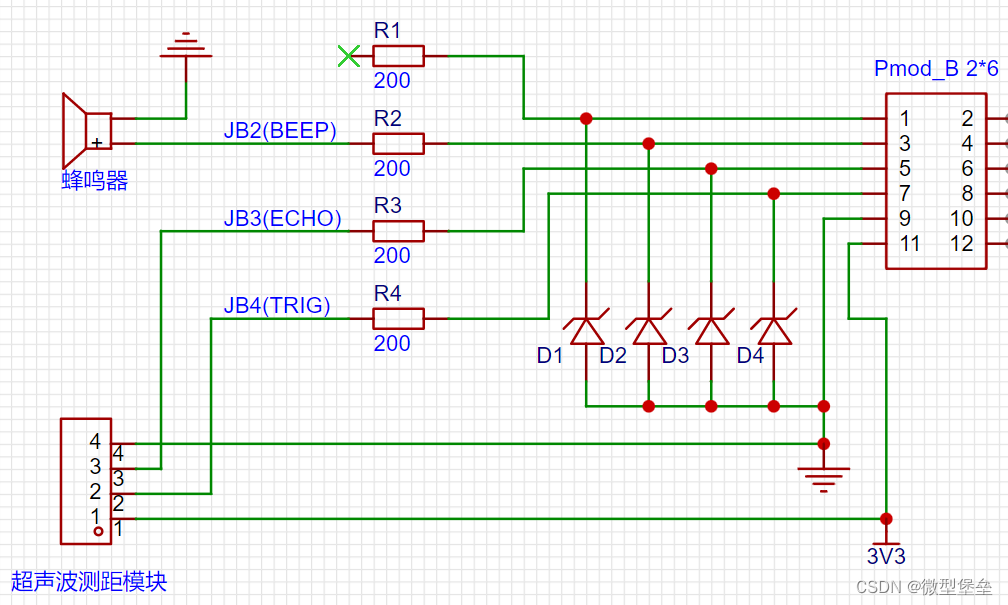

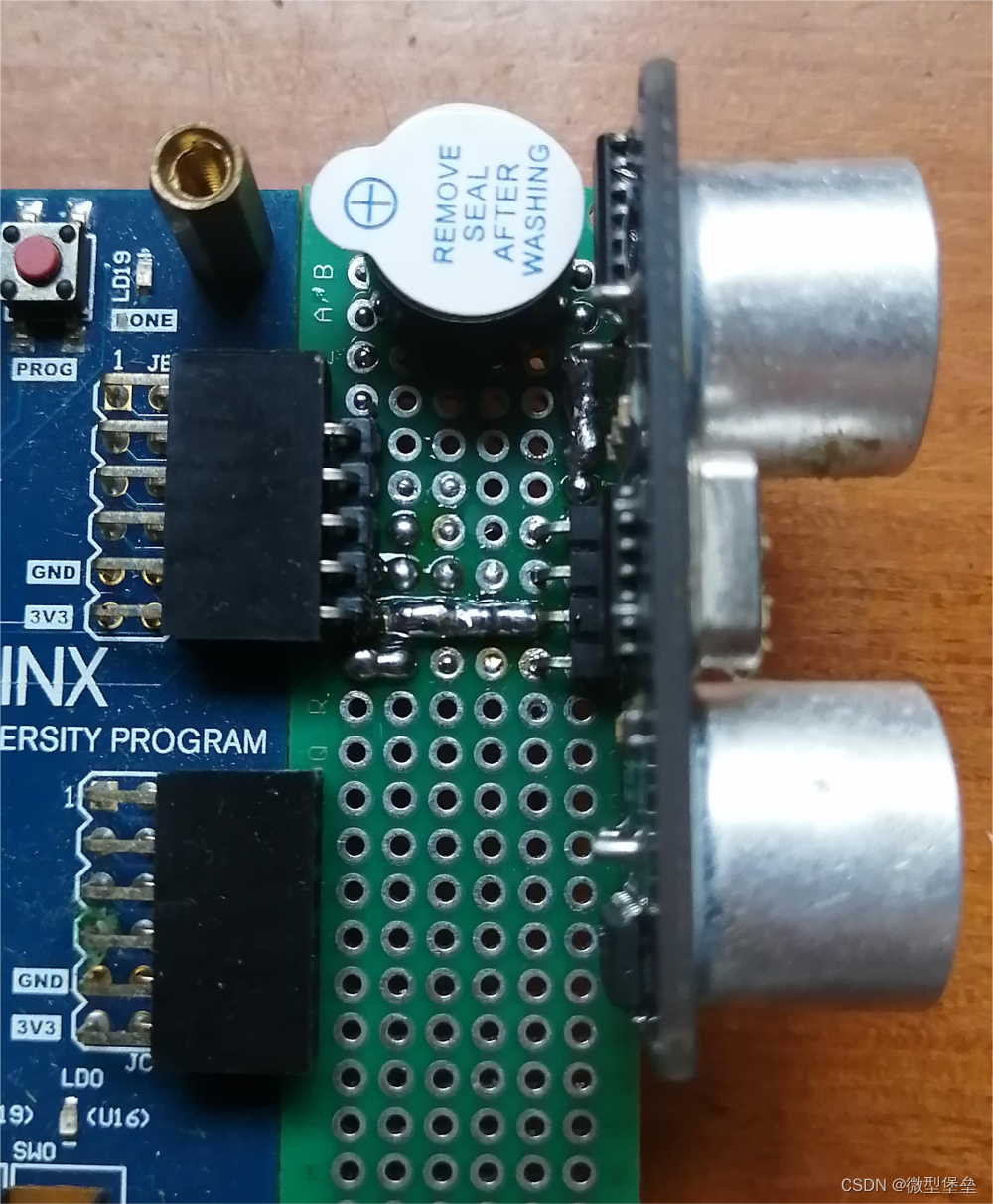

三、板卡外部接线图

板卡外部的模块有超声波测距和蜂鸣器模块,两个模块通过板卡的PMOD2*6排母B进行连接,如下图所示,板卡内部管脚的分配接线请看第五节具体模块设计中的第四篇FPGA一键测距仪之终篇。

PMODB排母位于BASYS3板卡的右上部分 ,我为了测距模块固定的方便,使用洞洞板焊接固定两个模块,并且把模块各自的引脚整合成方便插接到板卡上的排针引脚,插接方式如下图所示。

四、演示视频

因为该项目涉及到的内容较多,所以在讲实现原理、电路、程序与仿真之前,我们先上项目最终的演示视频。

我们看到这个系统受按键触发控制,可以正常运行,并且能把距离数据显示在数码管上(不足的一点是蜂鸣器的声音比较小),虽然测量精度不是很高但视频中的4次测量误差都在+/-3mm之内,所以总体来说基本符合测量指标。

五、具体模块设计

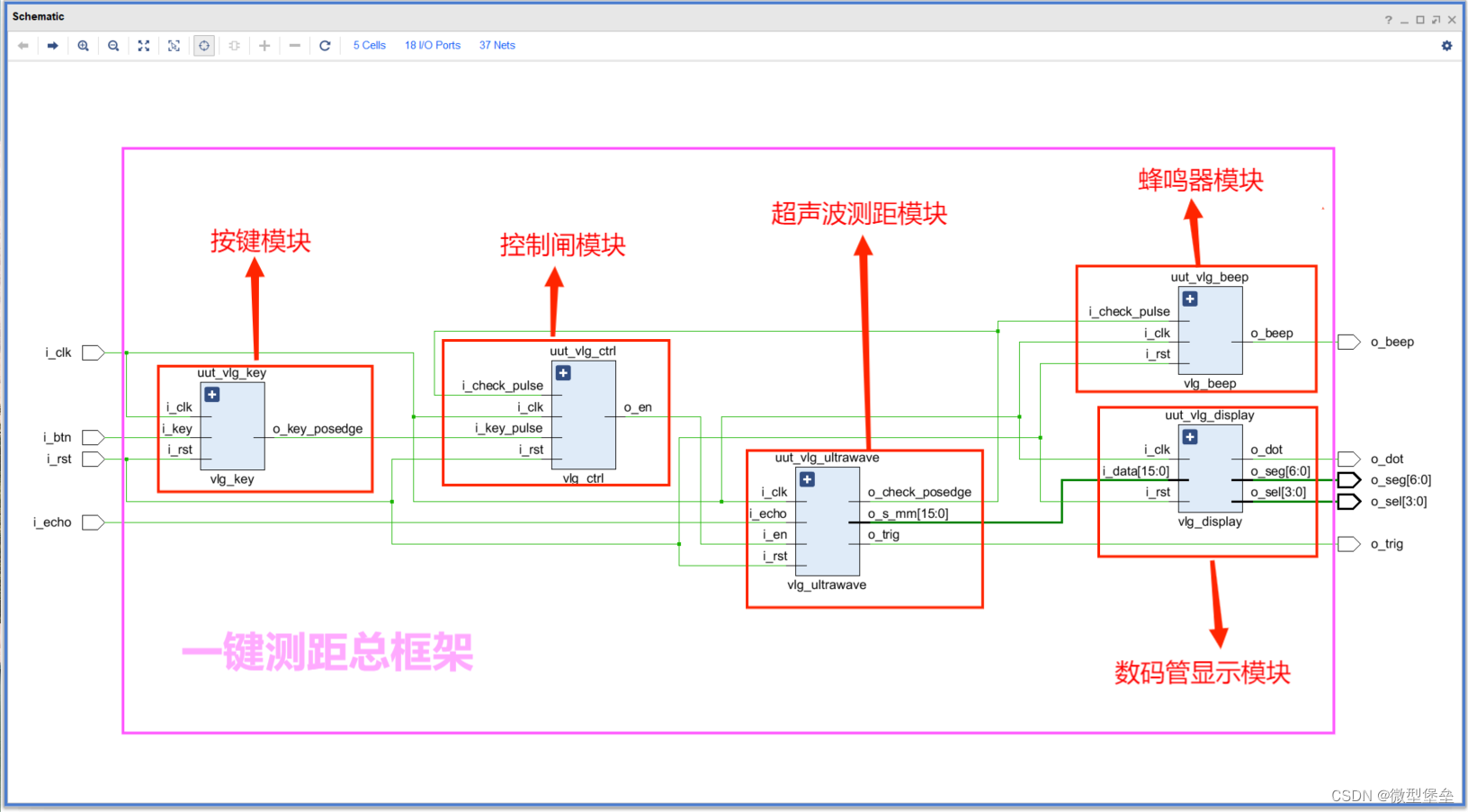

该系统总共由5个模块构成,总的电路框架原理图如下图所示。

按键模块负责产生按键摁下的触发信号;控制闸模块接收到按键信号后将“闸”打开,即使能超声波测距模块让其工作;超声波模块负责测距功能,数码管模块负责将测出来的数据进行译码显示;当测量数据趋于稳定后超声波模块会输出一个脉冲,这个脉冲会回馈到控制闸模块,此时控制闸模块将“闸”关闭,即停止测距模块的工作,直到被按键信号触发就再次启动测距;数据稳定后超声波模块输出的脉冲还会被传到蜂鸣器模块中进行处理,使蜂鸣器发出“滴滴滴”三声,以表示一次测距结束。

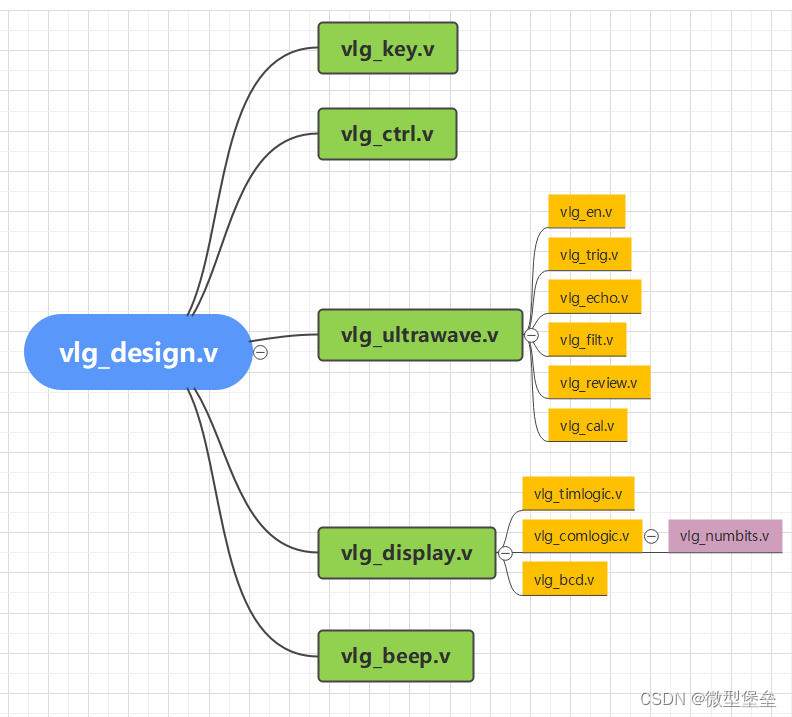

对应的verilog文件结构如下图所示。

下面我会分篇章对该项目中五个模块的讲解。

六、视频学习资料

总结

305

305

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?