1 IIC协议概述

- I2C 是一种串行通信总线,使用多主从架构,最初设计目的为了让主板、嵌

入式系统或手机用来连接低速周边设备。多用于小数据量的场合,有传输距离短,

任意时刻只能有一个主机等特性。严格意义上讲,I2C 应该是软硬件结合体。

2 IIC结构图

- 数据在传输时,需要把数据从主机发送到从设备上去,也需要将数据从从设备传输到主机设备,这涉及到数据的双向传输。

我们从一个例子来说明IIC协议工作原理:

有这样一个场景,在体育课上,老师将球传给学生,给哪个学生需要老师来指出,同样,当老师要求时,球在谁脚下就去通知该学生将球传过来。

① 发球:

a) 老师说:注意了(start);

b) 老师对 A 学生说,我要球发给你(A 就是地址);

c) 老师就把球发出去了(传输);

d) A 收到球之后,应该告诉老师一声(回应);

e) 老师说下课(停止)。

② 接球:

a) 老师说注意了(start);

b) 老师说:B 把球发给我(B 是地址);

c) B 就把球发给老师(传输);

d) 老师收到球之后,给 B 说一声,表示收到球了(回应);

e) 老师说下课(停止)。

在这个过程中:

① 老师说注意了,表示开始信号(start)

② 老师告诉某个学生,表示发送地址(address)

③ 老师发球/接球,表示数据的传输

④ 老师/学生收到球,回应表示:回应信号(ACK)

⑤ 老师说下课,表示 IIC 传输停止

3 IIC物理层

3.1 半双工

- IIC是半双工的,因为其总共只有两根线,一根是时钟信号线,一根是数据线,使用一根数据线传输数据只能做到同一时间只能作为发送或者接收数据的信号线。

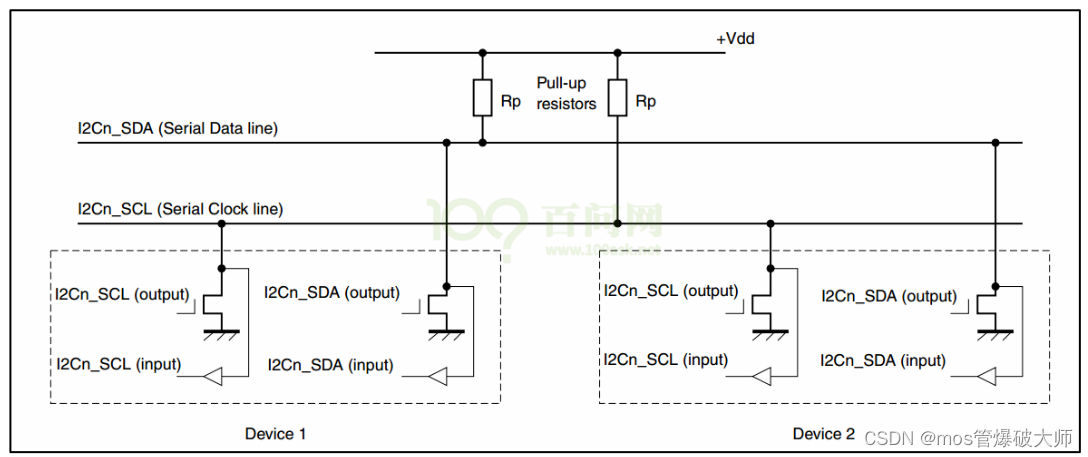

- 在IIC设备内部,有两条线,都接到了外部SDA线上。

- IIC主设备发出时钟,从设备接收时钟。

- SDA和SCL引脚的内部电路结构一致,引脚的输出驱动和输入缓冲连在一起,其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器。这样结构有如下特性:

① 由于SDA和SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的线与逻辑。

② 引脚在输出信号的同时还作为输入信号供内部进行检测,当输出与输入不一致时,就表示有问题发生了。这为 “时钟同步”和“总线仲裁”提供硬件基础。 - SDA 和 CLK 连接线上连有两个上拉电阻,当总线空闲时,两根线均为高电平。连到总线上的任一器件输出的低电平,都将使总线的信号变低。

物理层连接如下图所示:

3.2 地址和角色可配置

- 每个连接到总线的器件都可以通过唯一的地址和其它器件通信,主机/从机角色和地址可配置,主机可以作为主机发送器和主机接收器

3.3 多主机

- IIC 是真正的多主机总线,I2C 设备可以在通讯过程转变成主机。如果两个或更多的主机同时请求总线,可以通过冲突检测和仲裁防止总线数据被破坏。

3.4 传输速率

- 传输速率在标准模式下可以达到 100kb/s,快速模式下可以达到 400kb/s。

3.5 负载和距离

- 节点的最大数量受限于地址空间以及总线电容决定,另外总电容也限制了实际通信距离只有几米。

4 协议层

4.1 数据有效性

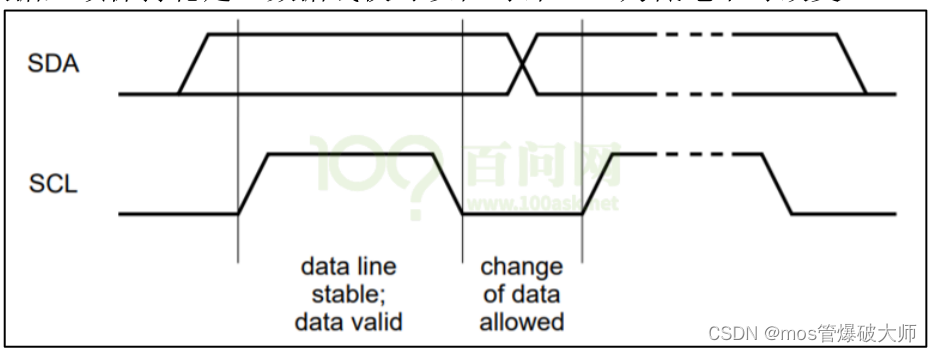

- IIC协议的数据有效性是靠时钟信号来保证的,在时钟信号的高电平周期内,SDA数据线上的数据必须保持稳定,SDA只能在SCL为低电平时改变。

4.2 起始条件和停止条件

- IIC在空闲时,SDA和SCL都为高电平,当SCL为高电平,SDA由高变低的跳变被定义为起始条件,当SCL为高电平时,SDA由低变高的跳变被定义为停止条件。

- 需要注意的是起始条件和停止条件都是由主机产生。在起始条件产生后,视为忙状态,在停止条件产生后,视为空闲状态。

4.3 应答信号

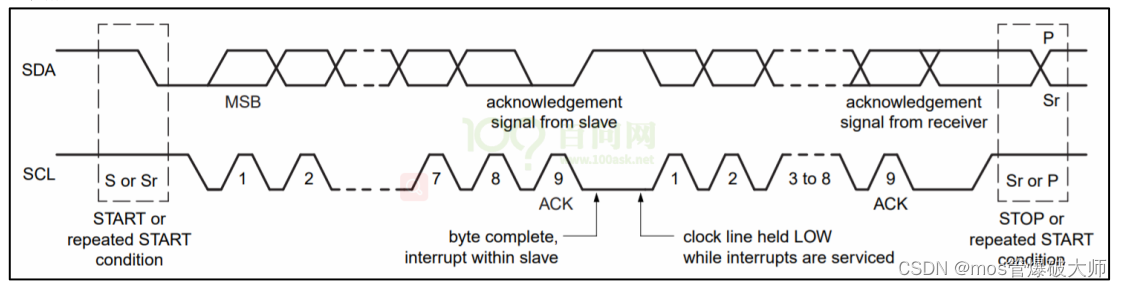

- 每当主机发送一个字节的数据给从机后,就要等待从机的应答信号,从而确认从机是否成功接收到了数据,从机应答主机所需要的时钟仍然是主机提供的,应答出现在每一个主机完成8个数据位的传输后紧跟着的时钟周期,低电平表示应答,高电平表示非应答。

4.4 数据帧格式

- SDA线上的每个字节必须是8位,在每个传输中所传输字节数没有限制,每个字节后面必须跟着一个ACK,在每次传输中,先传输最高有效位。

5 时序

5.1 写时序

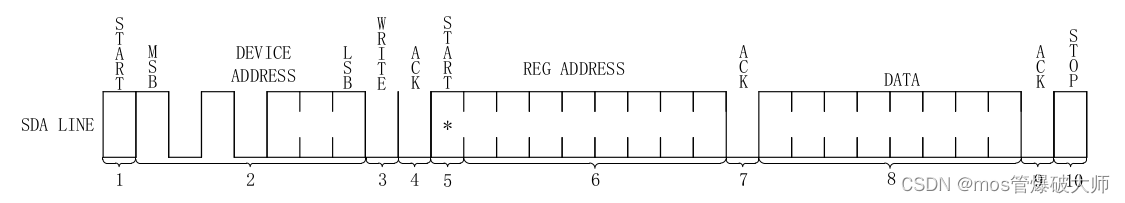

- 主机与从机的通信无外乎读和写,IIC总线单字节写时序如图所示:

- 据上图可知,主机需要发送数据时,先发送一个起始信号,接着将从机地址发送到总线上,如果总线上挂载有该从机,那么从机就会响应主机,给一个ACK信号,主机在接到ACK信号后,再次发送起始信号,接着将要写入数据的从机寄存器地址发送到总线上,在收到ACK应答信号后便可发送数据,每发送一个数据必须要有一个应答信号,只要没有发送停止信号,便可继续发送数据。

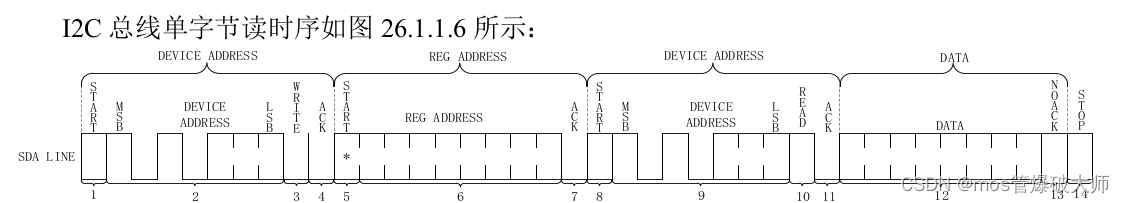

5.2 读时序

- 据上图可知,读取数据的过程相比写入数据要稍微复杂一些,主机在发送从机地址(写数据)后,发送要读取的寄存器地址,接着从新发送一次从机地址(读数据),从机便会将前面发送的寄存器地址中的数据发送出来,直到主机发送非应答信号之前,从机会不断的向主机传输数据,传输的数据为前面发送的寄存器地址递增后所指向的数据。

5260

5260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?