引言:

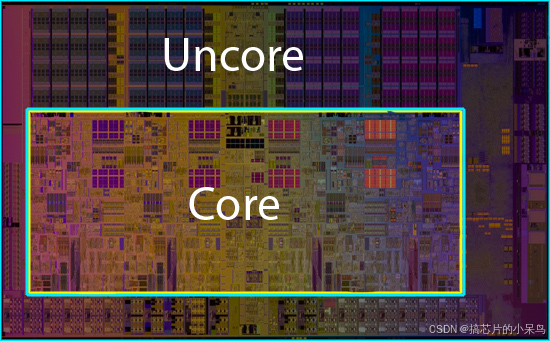

在半导体制造工艺逼近物理极限的今天,现代CPU架构师们正在上演一场精妙的平衡术。当我们在任务管理器中看到CPU使用率时,那个百分比数字背后隐藏着远比表面复杂的架构设计。Core(核心)与Uncore(非核心)的协同工作机制,恰似交响乐团中独奏家与伴奏乐队的完美配合,共同演绎着计算性能的华章。

一、核心舞台:CPU的运算中枢

每个CPU核心都是完整的计算单元,配备ALU(算术逻辑单元)、FPU(浮点运算单元)和三级缓存体系。在Intel Golden Cove架构中,单个核心包含:

-

4个整数ALU和3个AGU(地址生成单元)

-

2个256位FMA浮点单元

-

48KB L1数据缓存+32KB指令缓存

-

1.25MB专属L2缓存

多核架构通过MESI协议维护缓存一致性,当8个核心同时访问共享的LLC(末级缓存)时,环形总线上的每个节点都配备缓存代理,确保数据在环形拓扑中高效传递。AMD Zen4架构采用分片式设计,每个CCD(核心复合芯片)包含8个核心和32MB共享L3缓存,通过Infinity Fabric总线互联。

二、幕后指挥:Uncore的全局调度

Uncore子系统犹如城市交通指挥中心,管理着数据流动的每个环节。以Intel Xeon Scalable处理器的Uncore架构为例:

-

内存控制器:支持8通道DDR5-4800,每个通道集成32nS调度器

-

PCIe 5.0控制器:64条通道采用时分复用技术,支持CXL 1.1协议

-

网状互连网络:采用双向256位数据通路,延迟较环形总线降低23%

-

电源管理单元:集成16相数字PWM控制器,支持0.5mV电压调节精度

在AMD EPYC处理器中,Uncore的Infinity Fabric总线采用异步时钟域设计,允许不同CCD以独立频率运行,同时通过自适应路由算法优化数据传输路径,将跨Die延迟控制在12ns以内

三、协同进化:从北桥到3D封装

CPU架构的演进史就是Core与Uncore的融合史。2008年Nehalem架构首次将内存控制器纳入Uncore,使内存延迟从120ns骤降至60ns。近年来,3D封装技术推动Uncore革新:

-

Intel Foveros封装将Base Die作为Uncore载体,集成96MB LLC

-

AMD 3D V-Cache在垂直堆叠的SRAM上实现192MB共享L3

-

台积电CoWoS技术将HBM控制器与CPU整合,带宽达2TB/s

这些创新使Uncore从单纯的连接部件进化为智能数据枢纽。在Intel Sapphire Rapids中,Uncore内置的DLB(动态负载均衡器)能实时分析数据流模式,动态调整缓存分配策略,将AI工作负载的吞吐量提升40%。

四、未来之战:异构计算的挑战

随着CXL协议普及,Uncore正在演变为异构计算调度中心。NVIDIA Grace CPU通过900GB/s的NeoLink总线,使Uncore能同时管理CPU、GPU和DPU的缓存一致性。Arm Neoverse V2架构在Uncore中集成CMN-700网状网络,支持256个设备的一致性互联。

但挑战随之而来:当Uncore面积占比超过40%时,其功耗可能达到整颗芯片的35%。Intel采用混合键合技术将Uncore模块分解为多个小芯片(Chiplet),通过2.5D EMIB封装实现1.6Tb/mm的互连密度,使功耗降低22%。

在这个每平方毫米集成1亿晶体管的时代,Core与Uncore的界限正在模糊。当计算指令在核心的流水线中奔涌时,Uncore如同隐形的数据洪流引导者,用精密的时序控制和智能的路由策略,让每个电子都找到最高效的路径。这场持续进化的架构革命,终将引领我们突破计算的物理边界。

2392

2392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?