任务:

1、根据以下描述功能用verilog编写一段代码,并用状态机来实现该功能。

(1)状态机:实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程;

(2)描述状态跳转时间;

(3)编码实现。

2、画出可以检测10010串的状态图, 并用verilog编程实现之。

操作:

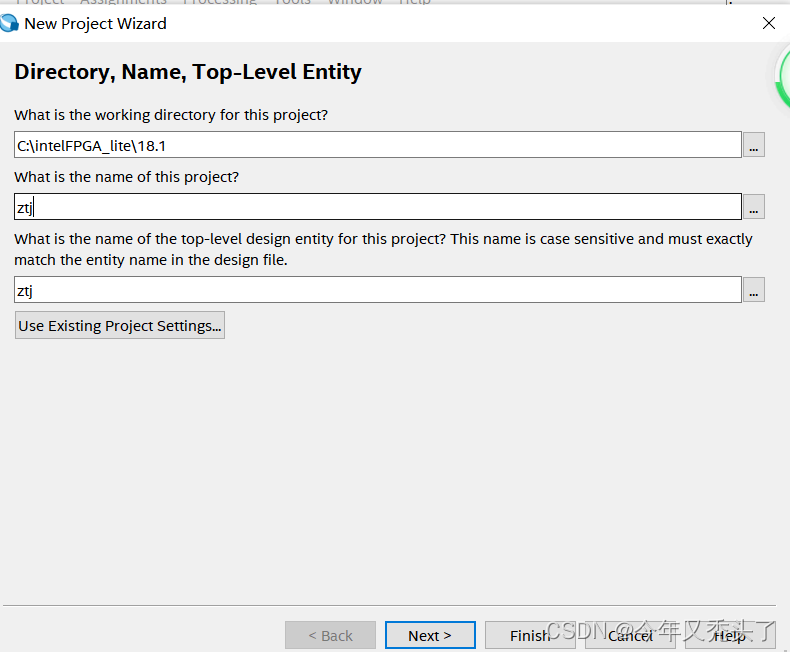

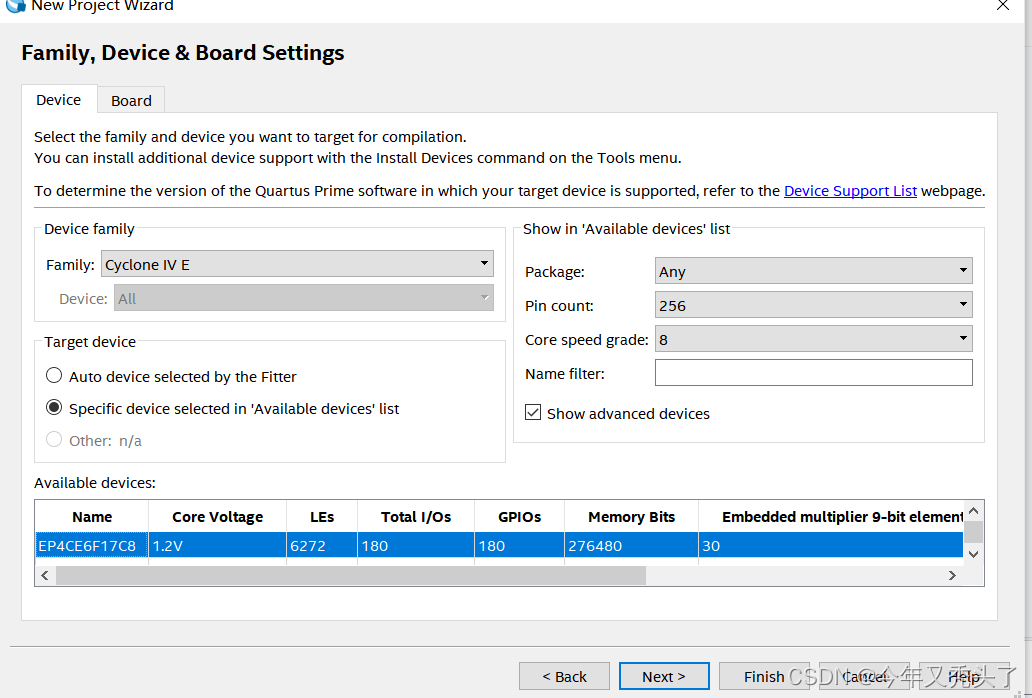

1.新建工程:

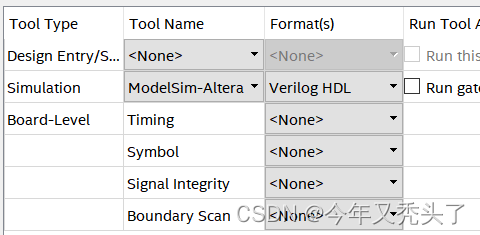

选择仿真:

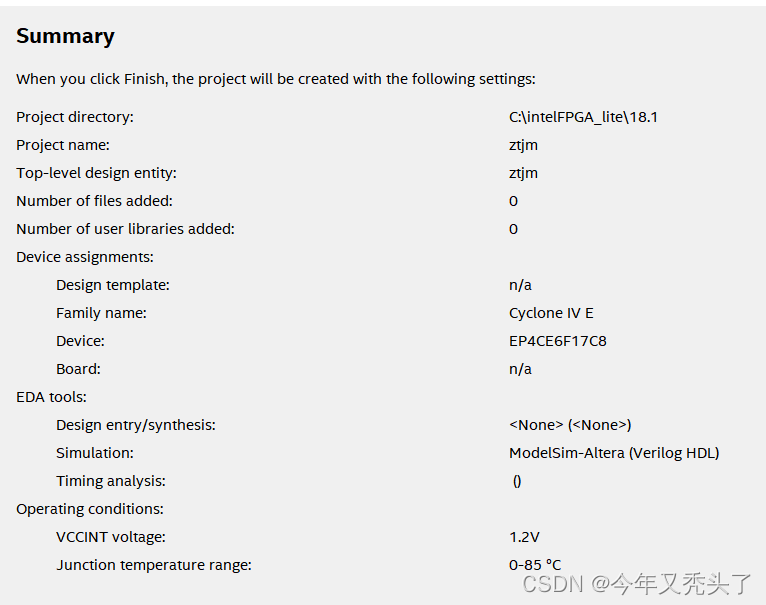

工程信息:

2.代码部分:

计时器模块:

//15s脉冲信号

module time_count(

input wire clk, //时钟,50MHZ

input wire rst_n, //复位信号,下降沿有效,negative

output wire sec_15//15s输出一个脉冲信号

);

parameter MAX_NUM = 30'd749_999_999;//记最大数15s,750_000_000次

reg [29:0] cnt_15;//计数寄存器

reg sec_15_r;

//0.5s计时器

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_15 <= 25'd0;

end

else if(cnt_15 == MAX_NUM)begin

cnt_15 <= 25'd0;

end

else begin

cnt_15 <= cnt_15 + 1'd1;

end

end

//0.5s脉冲信号

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

sec_15_r <= 1'b0;

end

else if(cnt_15 == MAX_NUM)begin

sec_15_r <= 1'b1;

end

else begin

sec_15_r <= 1'b0;

end

end

assign sec_15 = sec_15_r;//当右边改变,立马赋值给左边 assign和always并行

endmodule

状态机切换模块:

module fsm(

input clk,

input rst_n,

input wire sec_15

);

reg [2:0] cstate; //现态

reg [2:0] nstate; //次态

//状态划分

localparam state_ready = 0; //启动准备状态

localparam state_start = 1; //启动测试

localparam state_stop = 2; //停止测试

localparam state_query = 3; //查询测试结果

localparam state_display = 4; //显示测试结果

localparam state_initialize = 5; //初始化

//第一段:现态跟随次态,时序逻辑,非阻塞赋值

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cstate <= state_initialize;//复位键被按下,当前状态设置为初始化

else

cstate <= nstate; //下一次状态赋值给当前状态

end

//第二段:组合逻辑,阻塞赋值

always@(*)begin

if(!rst_n)

begin

nstate = state_initialize;

end

else

case(cstate)

state_initialize: begin

if(sec_15 == 1'b1) //该状态持续时间为1s,1s后,下一次状态更改为led1亮

nstate = state_ready;

else

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3165

3165

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?