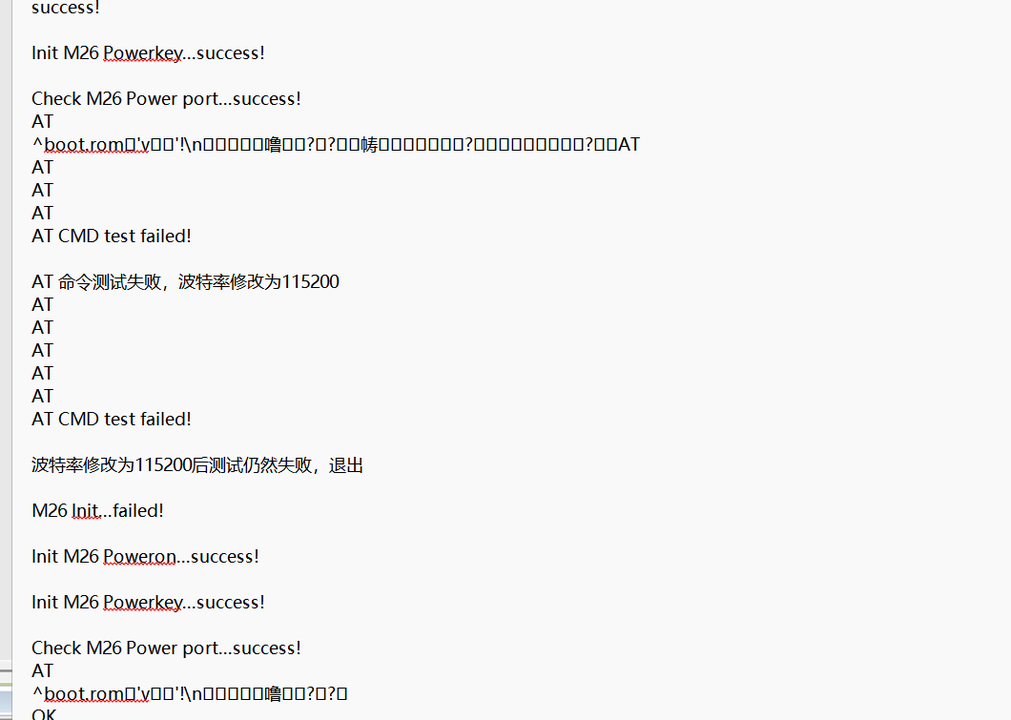

如下图所示,给电表发送AT指令会出现模组不回复的情况:

主要是开机的时序图写的有点问题。下面分析一下这个问题;

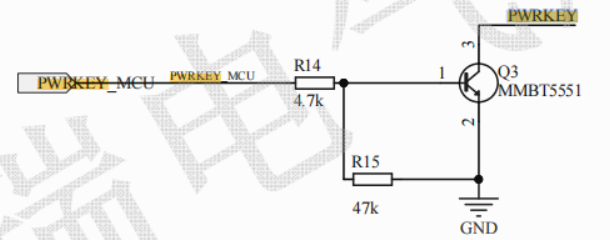

首先是mcu的引脚接到三极管,进而控制模块 PWRKEY,首先分析一下电路图;

电路图分析(NPN 三极管控制模块 PWRKEY)

1. 核心元件:

- Q3(MMBT3551):NPN 型三极管,起开关作用(控制

PWRKEY引脚电平)。 - R14(4.7kΩ):基极限流电阻,保护三极管。

- R15(47kΩ):基极下拉电阻,确保三极管默认截止(避免误触发)。

2. 工作逻辑(以 MCU 引脚 PWRKEY_MCU 控制为例):

PWRKEY_MCU 电平 | 三极管状态 | PWRKEY 电平 | 功能意义 |

|---|---|---|---|

| 高电平(Vcc) | 导通 | 接近 0V(低电平) | 触发模块开机 / 关机动作 |

| 低电平(GND) | 截止 | 由模块内部上拉决定(高电平) | 模块默认待机状态 |

3. 关键细节:

- 下拉电阻 R15:确保 MCU 输出低电平时,基极可靠接地,三极管必截止,避免杂波导致误导通。

- 限流电阻 R14:限制基极电流(

I_B ≈ (Vcc - 0.7V)/R14),防止三极管过流损坏。 - 电平反向:MCU 输出高电平时,

PWRKEY被拉低(NPN 导通时集电极接地),实现 **“高→低” 电平反转 **,匹配模块对PWRKEY的触发要求(通常低电平触发开机)。

模组开机时序图:

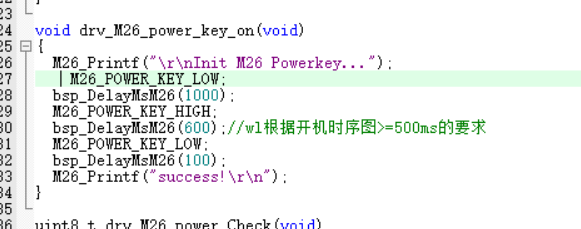

目前代码修改为:

时序图要求(PWRKEY 部分):

- 核心逻辑:

PWRKEY需 先拉低 → 保持 ≥500ms 低电平 → 再拉高(完成开机触发)。

根据之间原理图的分析,就对应的PWERKEY引脚:

核心逻辑:PWRKEY 需 先拉高 → 保持 ≥500ms 高电平 → 再拉低(完成开机触发)。

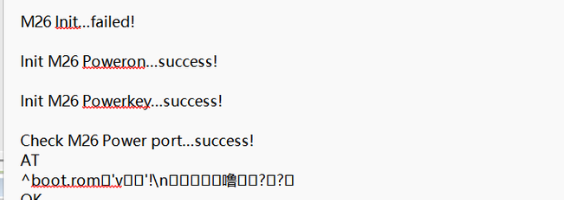

修改之后,模组可以正常回复:

更多嵌入式学习资料关注:

1141

1141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?