1、DDR供电

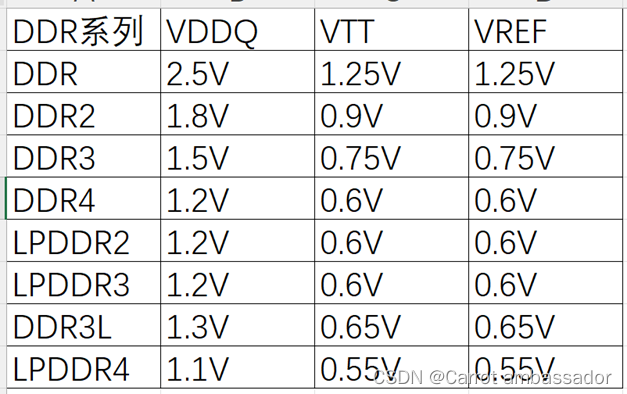

了解sink and source DDR termination regulator(灌电流和拉电流双倍数据速率(DDR) 终端稳压器)之前需要先了解DDR的供电。

其中主电源有VDDQ、VDD,VDDQ是给IO buffer供电的电源,VDD是给内核供电,两者通常拉到一起。

参考电源Vref,是一种低电流、精确的参考电压,它在逻辑高电平(1)和逻辑低电平(0)之间提供一个阈值,要求跟随VDDQ,并且Vref=VDDQ/2以适应I/O电源电压的变化,能适应比固定阈值更大的噪声。

VTT是改善信号质量,最常见的规格是0.49到0.51倍VDDQ,VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

常见不同类型DDR供电如下表。

2、sink and source在DDR供电中的应用

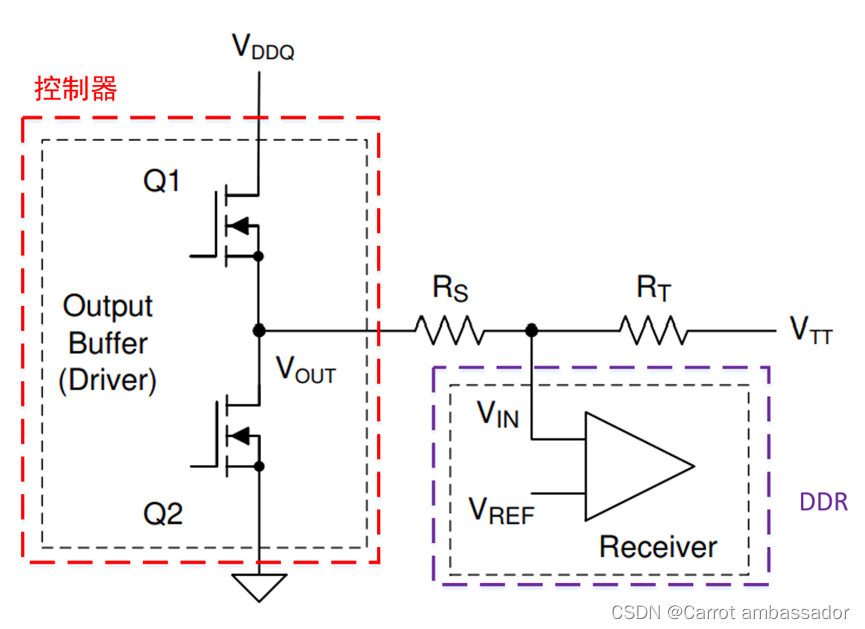

如下图是SSTL(series stub termination logicl)电平在DDR地址级控制信号的应用,信号方向为控制器输出,DDR输入。控制器和DDR接收之间串接电阻Rs,并在接收端通过上拉电阻Rt上拉到VTT。通常设计中VTT和Vref都等于VDQQ/2,且VIN有特定的范围要求,如在SSTL_18(DDR2)的应用中,高电平VIN必须大于Vref+125 mV, 低电平VIN必须小于Vref-125mV,否则就容易导致误码。

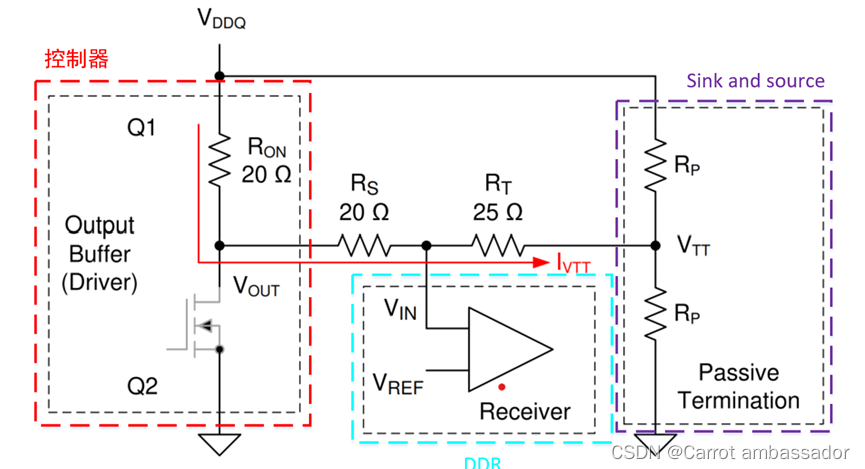

如下图为SSTL_18输出为高时的电流流向图,此时控制器中的Q1导通,Q2关闭,VDDQ供电,如果只有这一个信号,电流流向为从VDDQ流向VTT,此时sink and source表现为灌电流(sink current)。

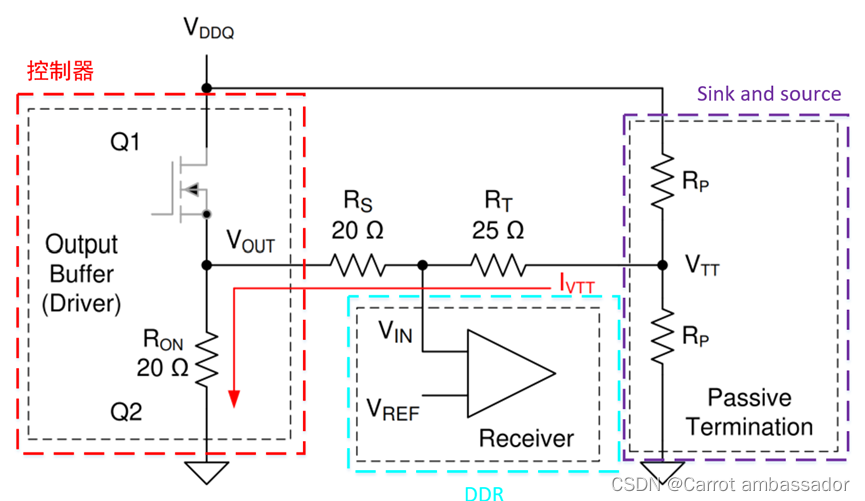

如下图为SSTL_18输出为低时的电流流向图,此时控制器中的Q1关闭,Q2打开,此时由VTT供电,如果只有这一个信号,电流流向为从VTT流向GND,此时sink and source表现为拉电流(source current)。

实际应用中,DDR中并行的接口数量较多,sink and source表现为灌电流还是拉电流,需要根据同一时间高低电平的数量来判断,如果控制器输出高多于低则表现为灌电流,高少于低则表现为拉电流,高低数量相等时VTT电流等于0。

3、sink and source

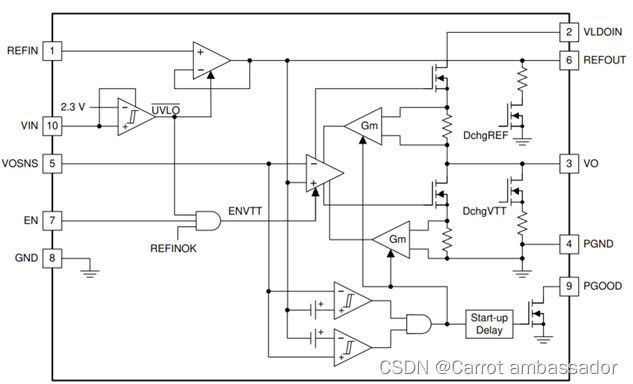

如下图为TI的灌电流和拉电流双倍数据速率(DDR) 终端稳压器TPS51200的结构框图。

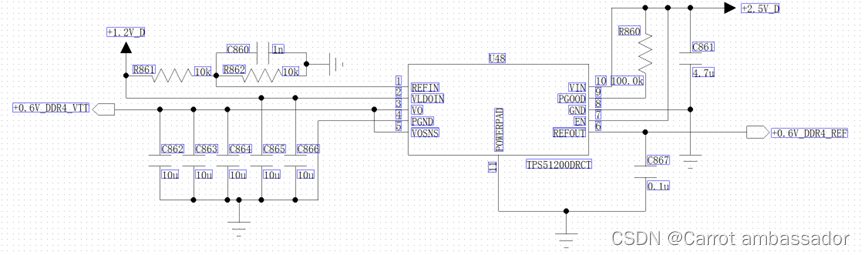

其典型应用如下图中的DDR4供电设计图。VLDOIN-VO(VTT输出)为一个LDO,通过VOSNS监测输出VTT的电压,构成一个快速响应的反馈环路,保证能适应DDR的快速翻转造成的灌电和拉电需求。

REFOUT则是简单的通过VDDQ分压得到VDDQ/2,达到跟随VDDQ的效果。

文章详细介绍了DDR内存的供电系统,包括VDDQ、VDD、Vref和VTT的作用,以及SSTL电平标准在DDR地址和控制信号中的应用。SinkandSource分别代表灌电流和拉电流,在DDR中根据信号状态调整电流方向,维持信号质量。TI的TPS51200DDR终端稳压器用于适应快速翻转的灌电和拉电需求,确保VTT电压稳定。

文章详细介绍了DDR内存的供电系统,包括VDDQ、VDD、Vref和VTT的作用,以及SSTL电平标准在DDR地址和控制信号中的应用。SinkandSource分别代表灌电流和拉电流,在DDR中根据信号状态调整电流方向,维持信号质量。TI的TPS51200DDR终端稳压器用于适应快速翻转的灌电和拉电需求,确保VTT电压稳定。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?