综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL 级的 电路转换到门级的过程;Design Compiler 是 Synopsys 公司用于做电路综合的核心工具,它 可以方便地将 HDL 语言描述的电路转换到基于工艺库的门级网表。本章将初步介绍综合的 原理以及使用Design Compiler 做电路综合的全过程。

企鹅号 3270516346,欢迎交流学习以及获取资料

1.1 什么是综合

- 综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的 一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性 能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。即实现 在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单 元电路的连接。

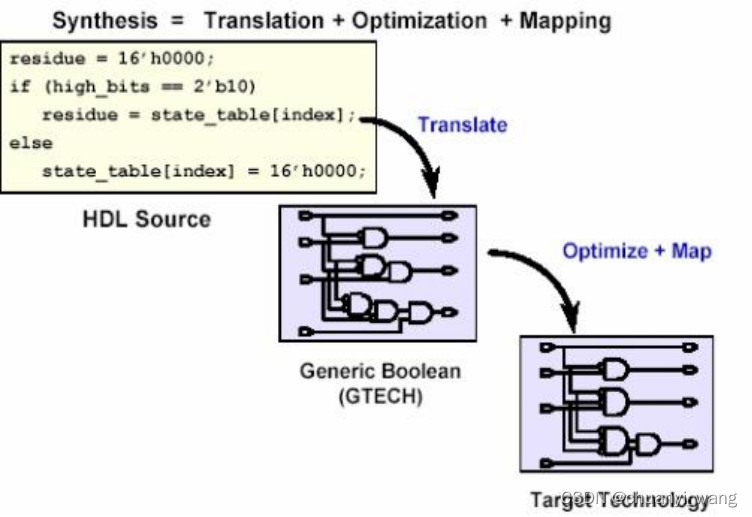

- 如 图 所示,综合主要包括三个阶段:转换(translation) 、映射(mapping) 与优化 (optimization) 。综合工具首先将 HDL 的描述转换成一个与工艺独立(technology-independent)的 RTL 级网表(网表中 RTL 模块通过连线互联) ,然后根据具体指定的工艺库,将 RTL 级网表 映射到工艺库上,成为一个门级网表,最后再根据设计者施加的诸如延时、面积方面的约束条件,对门级网表进行优化。

1.2 综合的不同层次

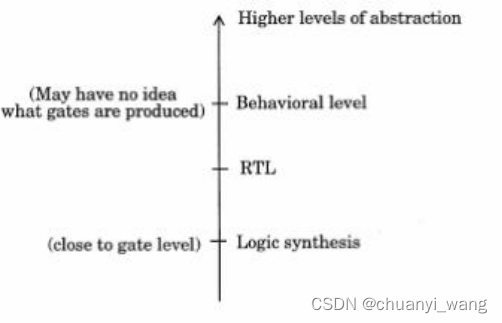

- 设计的不同的抽象层次如图 2 所示,随着抽象层次的升高,设计者对于最终硬件(门和 触发器)的控制能力越来越小。设计者可以在上述的三个层次用 HDL 语言描述他的设计,

- 根据 HDL 语言描述的层次的高低,综合也相应的可以分为逻辑级综合,RTL 级综合以及行 为级综合。

1.2.1逻辑级综合

- 在逻辑级综合中,设计被描述成布尔等式的形式,触发器、锁存器这样的基本单元采用 元件例化(instantiate)的方式表达出来。下面是一个加法器的逻辑级描述,输出寄存器

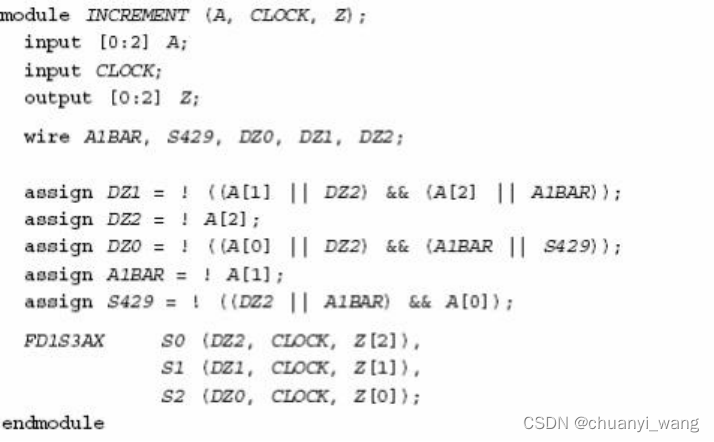

- 它综合以后的电路网表如下图 所示,对比一下不难看出,逻辑级描述实际上已经暗示 了综合以后的网表。

1.2.2 RTL级综合

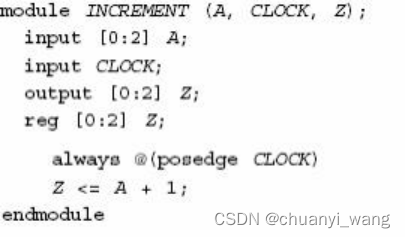

- 与逻辑级综合不同,在 RTL 级综合中,电路的数学运算和行为功能分别通过 HDL 语言特 定的运算符和行为结构描述出来。对于时序电路,我们可以明确的描述它在每个时钟边沿的行 为。下面同样是一个加法器的描述,它综合以后的网表如图 3 所示——

- 注意到,图 3中的三个触发器不是例化而是通过 HDL 的特定结构推断出来的。这种推 断是根据一些推断法则(Inference rule)进行的,例如在这个例子中,当一个信号(变量)在 的边沿进行赋值( always 语句),那么这个信号( 变量)可以推断为一个触发器。

1.2.3 行为级综合

- 行为级综合比 RTL 级综合层次更高,同时它描述电路也越抽象,在 RTL 级中,电路在每个时钟边沿的行为必须确切的描述出来,而行为级描述却不是这样,这里没有明确规定电路的时钟周期,推断法则也不是用来推断寄存器。 电路的行为可以描述成一个时序程序 (sequential program) ,综合工具的任务就是根据指定的设计约束,找出哪些运算可以在哪个周期内完成,需要在多个周期内用到的变量值需要通过寄存器寄存起来。

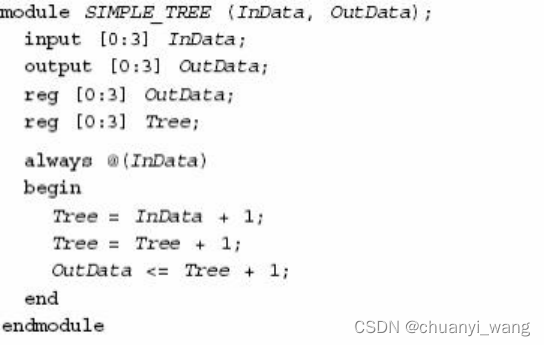

请看一个简单的行为综合的例子——

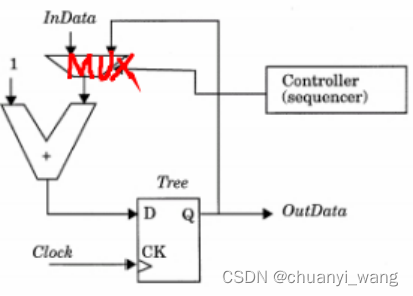

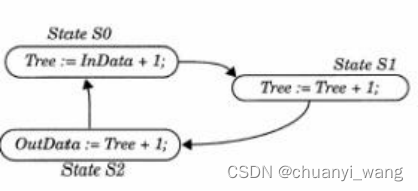

- 上面这个例子没有任何时钟的信息,现在假设一次加法操作(加法器)需要 5ns 的延时并且 设系统的时钟是 6ns ,那么可以看出执行完上述操作需要 3 个周期的时间。另外,所有 的三个加法语句可以通过重用一个加法器来实现,而且只需要一个叫做 Tree 的寄存器保存 中间变量的值(不同时钟周期的变量值) 。这种假设下的电路结构图如图 所示,控制器的时 序关系如图 5所示。

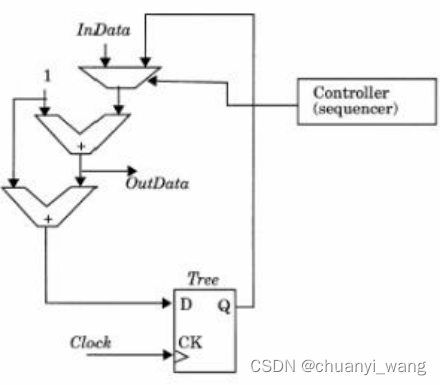

- 如果改变约束条件,假设时钟周期是 11ns,那么完成全部操作仅需 2 个周期,同时需 要 2 个加法器,下图 分别是此时的电路结构图和控制器时序图。

1.2.4 Design Compiler 所处的位置

- 上图向我们展示了一个设计从最初的最抽象的概念阶段到最终的芯片阶段的转化过程, 在这个过程当中,Design Compiler 主要完成将设计的 RTL 级描述转化到门级网表的过程, 比 RTL 更高的行为级的综合,将由 Synopsys 的另外一个工具——Behavior Compiler 来完成。 在以下的章节中,我们主要围绕怎样将一个 RTL 级描述的设计转化为门级网表来进行讨论。

1.3 使用 Design Compiler 做综合的流程示意图

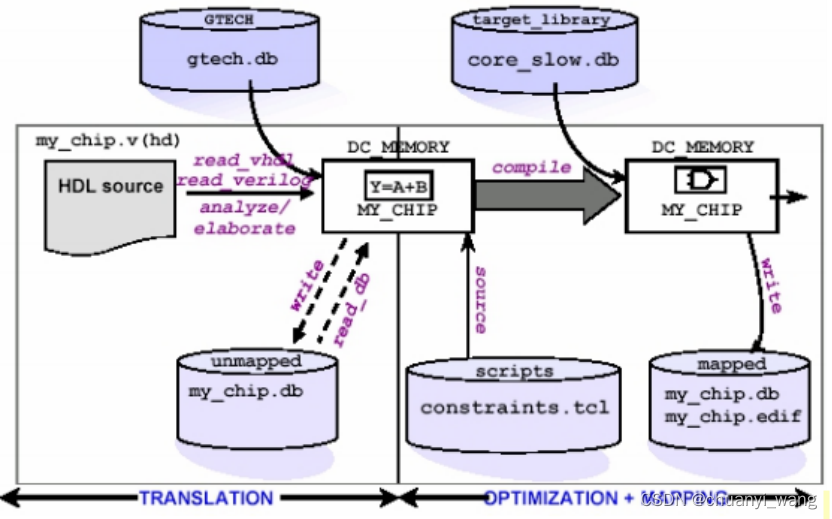

- 与一般的综合过程相同,使用 DC 做综合也包含转换、优化和映射三个阶段。转换阶段 综合工具将 HDL 语言描述的电路或未映射的电路用工艺独立的 RTL 级的逻辑来实现,对于 Synopsys 的综合工具DC 来说,就是使用gtech.db①库中的RTL级单元来组成一个中间的网表。优化与映射是综合工具对已有的中间网表进行分析,去掉其中的冗余单元,并对不满足限制条件(如constraints.tcl)的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上(如 core_slow.db)。

1.4 超深亚微米给综合工具带来的挑战

- 当半导体工艺的最小特征尺寸小于 1um 时,称之为亚微米设计技术,当最小特征尺寸 小于 0.5um 时称为深亚微米设计技术(DSM:Deep Sub Micrometer) ,而当进一步小于 0.25um 时,则称为超深亚微米设计技术(VDSM:VeryDeep Sub Micrometer) 。当进入超深亚微米设计 后,原有的综合工具受到了很大的挑战,其中一个主要表现是:连线的延时迅速上升。

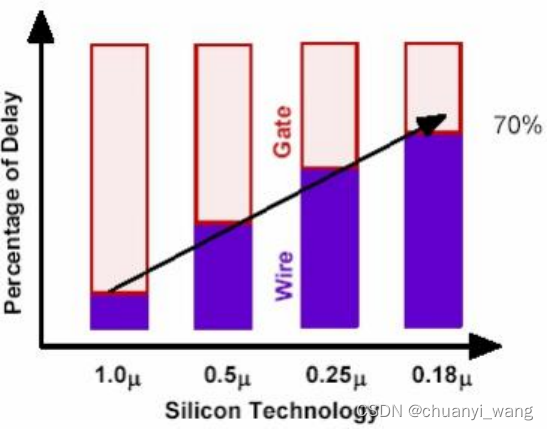

- 当特征尺寸大于 0.5um 时,电路的延时主要集中在门级单元的延时上,如果门级单元延 系统延时的 70% 以上 ,则前端综合后的电路延时与后端进行布局布线以后反标(back- annotate)回来的电路延时相差不大。从图 10 可以看出,当特征尺寸进一步缩小时,单位时连线上的延时以及互连线的总长度迅速上升,这 方面的因素都使得连线延时在系统总延, 于 。合通出u时m相设差计会时比, 较连大线,延单时靠已准5%估以计上电 路的延时情况,此时需要经过前端后端工具不断叠代来达到比较真实的结果。在 0. 18um 的时候,连线延时已经达到了 70% ,这时就算增加叠代的次数也不一定能得到满意 的结果, 因而必须引入新的综合手段,保证优化叠代过程的收敛, 这就是物理综合方法 (Physical Synthesis Flow)。

- Physical Compiler 是 Synopsys 推出的新一代综合工具,它逐渐打破了前后端设计分离的 设计方法而将它们结合在一起。它与 DesignCompiler 的最大区别是综合出的门级网表除了 电路的连接关系之外还有它在版图中具体位置的信息,有了单元的位置信息,综合工具就 可以比较准确的估算出互连线的延时,从而减少叠代次数,提高设计效率。

5322

5322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?