覆盖率概述

设计的功能描述文档,知道其边界信号,时序协议,寄存器,功能。便可设置测试功能点。 到了系统级测试,难度增加。

是否所有设计的功能在验证中都已验证?

代码中的某些部分是否从未执行过?

覆盖率——指标。

覆盖率爬坡,越到后面越慢。覆盖率就是衡量验证的精度和完备性的数据的指标。

激励多样化。 验证环境的完善,要能产生丰富的激励,而且monitor和checker也要足够健壮。

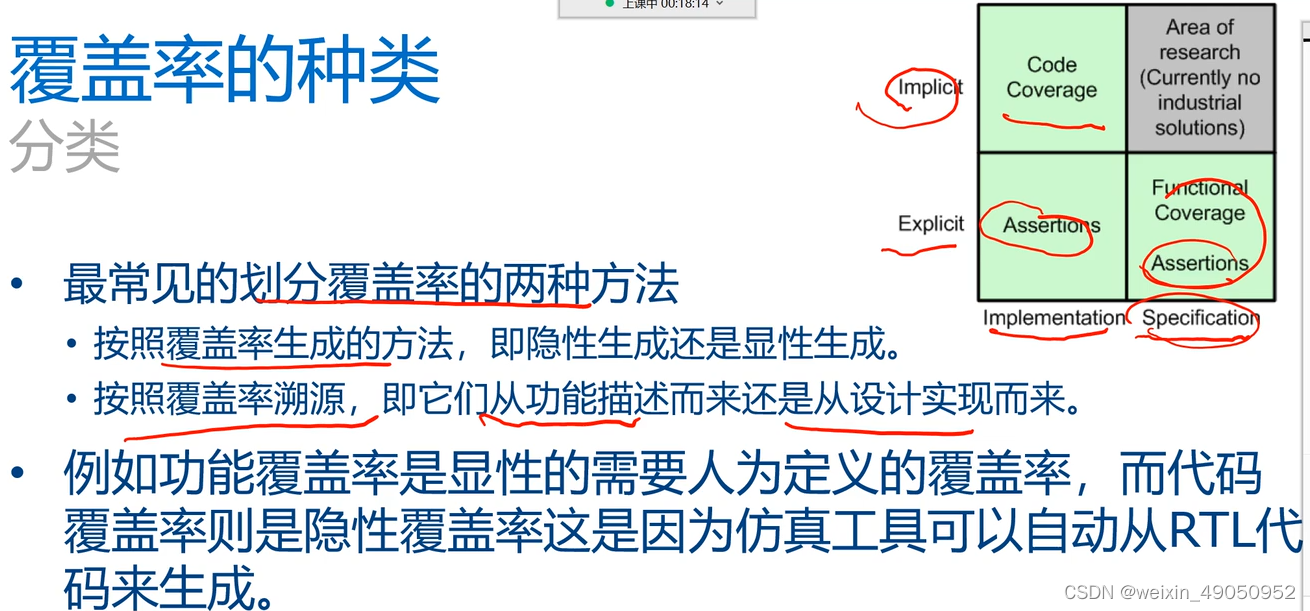

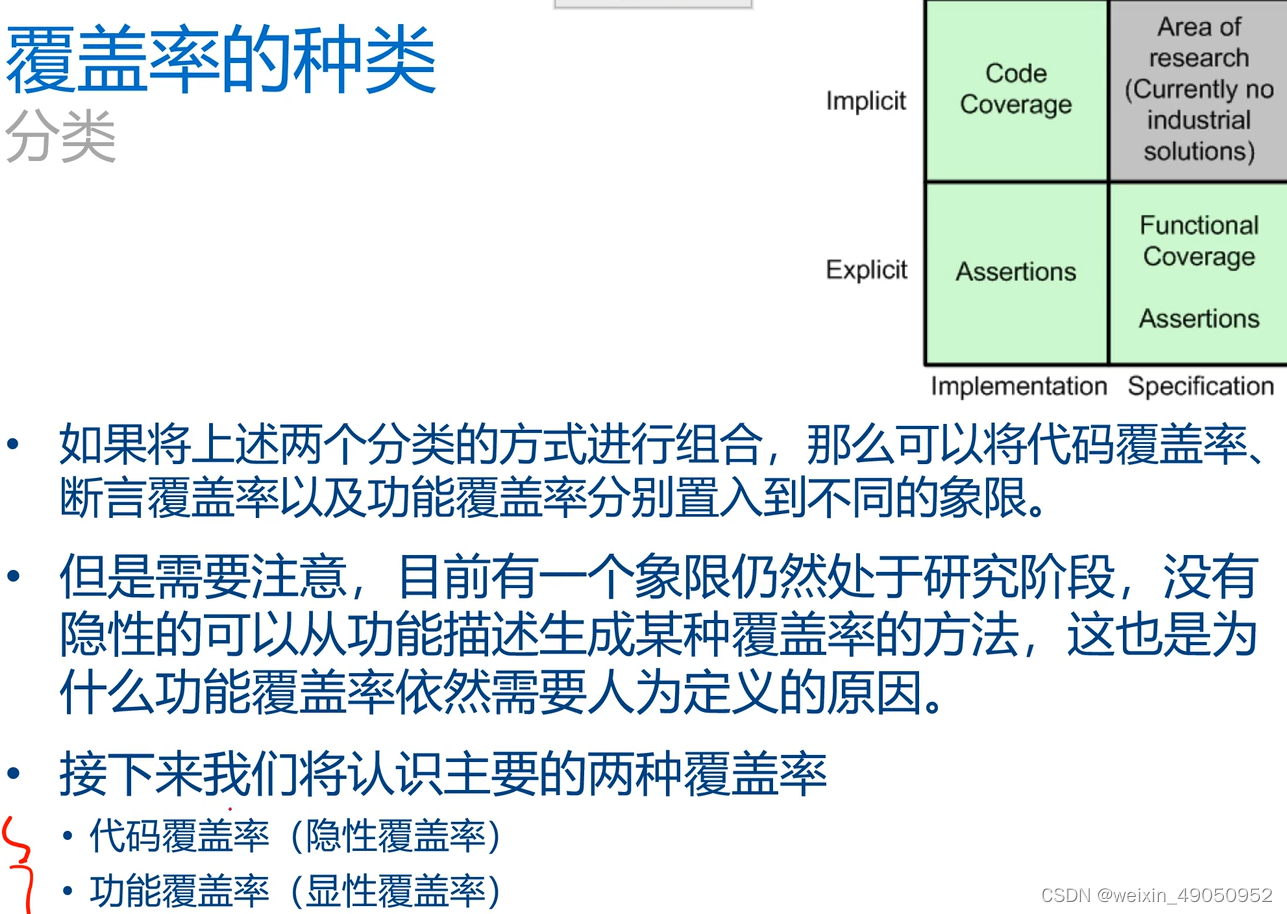

覆盖率种类

即使达到100%代码覆盖率,并不一定到100%功能覆盖率。

划分覆盖率。 从覆盖率生成的方法——1.隐形/显性的,隐形的不需要自己写,code coverage自动去检测,去告诉哪些代码已经执行过了; 显性的,断言覆盖率、功能覆盖率都是要自己写的。 2.覆盖率溯源,这部分的覆盖率规定是跟着,specification功能or设计implementation走的

9495

9495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?