目录

Chapter 11 FM demodulator implementation

11.1 鉴频器(Frequency Discriminator)

11.2锁相环(Phase-Locked Loop, PLL)

前言

本笔记是基于北京都柏林学院2022年EEEN3005J Communication Theory课程课件总结出的笔记。任课教师为Dr Deepu John。

阳老板建议: 本节内容之前的为期中考试内容,前11章内容配合期末试卷一同使用效果最佳。

Chapter 11 FM demodulator implementation

我们将考虑调频信号的解调。解调调频信号有两种主要方法:

11.1 鉴频器(Frequency Discriminator)

频率鉴别器如图11.1.1所示。它由微分器和包络检测器组成。微分器也称为斜坡电路。

接收到的信号由:

![]()

这是通过一个振幅限制器,它给出![]() ;该信号被用作微分器的输入。微分器提供输出:

;该信号被用作微分器的输入。微分器提供输出:

现在,FM信号的相位偏差θ(t)由下式给出:

因此,包络检测器的输入为:

![]()

但这只是一个完整的正弦曲线,有包络线:

![]()

包络检测器输出端的电容器阻断直流电,输出信号与g(t)成正比。

11.1.1 差异化因素

在实践中,为了构建微分器(或斜率电路),我们使用一些具有传递函数H(f)的电路,该函数在f=fc附近近似线性,即H(f)≈ K1*f+K2位于fc附近,如图11.1.2所示。

因此,该电路将频率变化线性转换为振幅变化。在一定频率范围内,任何滤波器电路都具有这种能力。

为了实现良好的FM解调,我们需要良好的线性(避免失真),以及线性区域的陡坡(因为频率变化相对较小)。

11.2锁相环(Phase-Locked Loop, PLL)

锁相环的示意图如图11.2.1所示。

它由压控振荡器(VCO)、相位检测器和环路滤波器(低通滤波器)组成。

当操作正确时,VCO的输出锁定到PLL的输入vi(t);这意味着它们的频率大致相同,即![]() 。这是怎么回事?

。这是怎么回事?

要理解这一点,首先想象一个稳态情况:

11.2.1 稳态

这是输入vi(t)具有固定频率fi赫兹和相位偏移φi的地方。这种说法是,系统锁定在一个点上,此时VCO也在fi处振荡,带有一些固定相位偏移![]() 。对于固定频率的VCO,其控制电压和PLL输出vo(t)是恒定的。

。对于固定频率的VCO,其控制电压和PLL输出vo(t)是恒定的。

由于相位检测器的输出是一个常数,LPF在这个简化的稳态场景中没有功能,因此我们在分析中会忽略它:

• 当![]() 时,相位误差,

时,相位误差,![]() 是一个常数(但不一定为零)

是一个常数(但不一定为零)

•如果![]() (由于噪音)少量增加

(由于噪音)少量增加![]() ,则相位检测器的极性使得相位误差∆φ会小幅降低(即负反馈)=⇒ VCO控制电压降低=⇒

,则相位检测器的极性使得相位误差∆φ会小幅降低(即负反馈)=⇒ VCO控制电压降低=⇒ ![]() 再次向

再次向![]() 下降。

下降。

•另一个方向的频率变化也是如此。

•因此,系统在![]() 赫兹下稳定。

赫兹下稳定。

好吧,但这对解调有什么帮助呢?

VCO的振荡频率![]() 为:(根据方程式10.2.2)

为:(根据方程式10.2.2)

注意:输出电压与VCO的输入频率和自然振荡频率成正比——这是关键!

11.2.2 缓慢变化的频率

现在我们认为,如果输入频率fi变化缓慢(与标称频率相比),那么PLL环路将保持锁定在这个缓慢变化的频率,即关系:

这仍然适用。

在FM中,频率fi由以下公式给出:

因此,输出电压是调制函数的线性函数,并且该函数的参数是已知的,因此实现了解调。

11.2.3 低通滤波器(Low Pass Filter)

图11.2.1中低通滤波器(LPF)的用途是什么?

到目前为止,我们还没有考虑噪音。

如果在PLL的输出端存在任何噪声(并且将会存在),那么在没有LPF的情况下,该噪声将直接传播到vo(t),从而产生两种影响

1.解调后的输出会有噪声。

2.VCO控制信号会产生噪音,导致PLL无法正常锁定

-在极端情况下,这可能会导致系统无法跟踪模块。

如图11.2.1所示,这两个问题都可以通过在环路中包含LPF来解决。LPF的带宽应为:

1.大于W,调制信号的带宽g(t)。这是为了确保输出vo(t)=线性函数(g(t)),以及

2.尽可能小,以限制反馈路径中的噪声量。

理想情况下,它将是一个截止频率为W的砖墙滤波器,然而这些电路通常使用带宽>W的简单RC滤波器实现。

11.2.4 相位检测器(Phase detector)

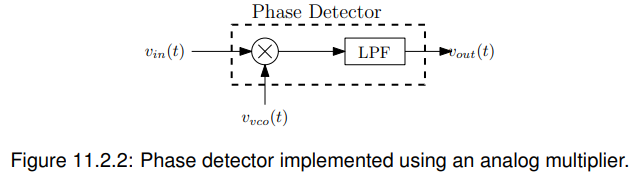

实际上,相位检测器通常由模拟乘法器实现——如图11.2.2所示。

当PLL锁定时,相位检测器的两个输入的频率相同,但相位不同,即:

乘法器的输出为:

LPF的加入消除了输出的高倍频:

其中Kd是比例常数,我们称之为检测器的增益。请参阅图11.2.3,查看vout的图表∆φ.

后记:

以上为期中考试全部内容,一天更新两章节,生产队的驴都没我勤快。相关练习题即解答将在今后几天总结出来。需要的请微信联系阳老板。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?