接着第(1)部分写,之前已经写完了时序优化相关的操作,包括流水线,扇出等操作,这里主要针对跨时钟域相关问题进行总结。

首先明确亚稳态的概念,即在建立时间与保持时间不满足的情况下采集了数据导致出现数据不稳定的现象。

对于同步电路,直接采用STA静态时序分析来减小亚稳态;

对于异步电路,分两种情况讨论:

控制信号传输:所谓控制信号,即只需要有脉冲便可以触发条件,这种可直接采用打两拍的方式进行处理;

数据信号传输:所谓数据信号,不能采用打两拍,因为打两拍涉及到信号展宽等工作,而数据信号每个时钟周期的值都代表着具体数值,故只能采用握手或fifo的方式进行传输。

以下分析之前,首先有一点很重要,即Tco >> Tsu;

这里主要针对控制信号进行分析,分为两个主要任务:1、消除亚稳态;2、不漏数据,且信号输出正确;

首先来看第一点,分析一下打两拍是如何消除掉亚稳态的。

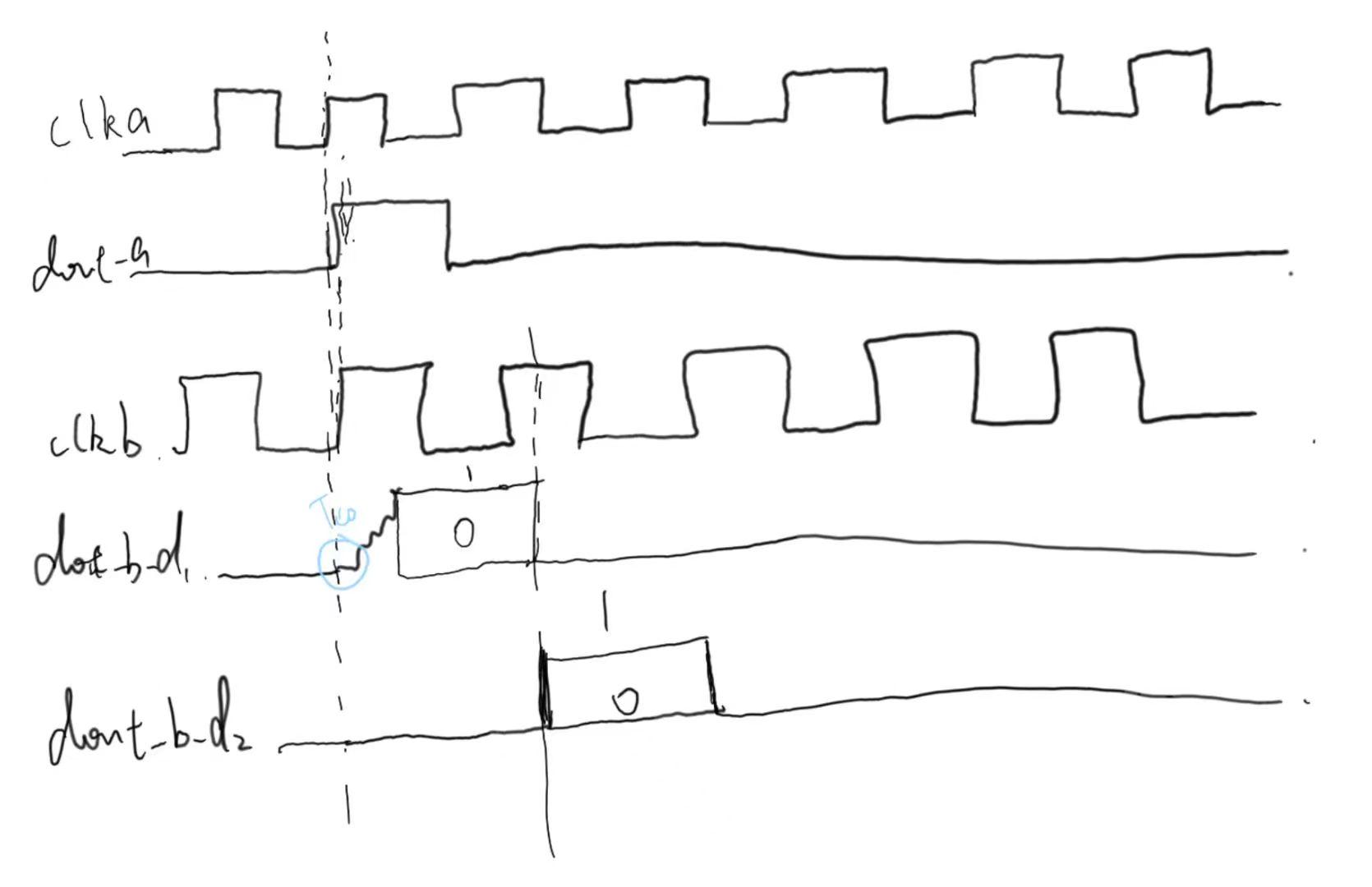

第二次采集时由于已经稳定下来,故可以得到稳定信号,但这样仍然有问题,douta如很很短,是有可能被clkb采不到的,而且就算采到了,从图上也可以看出不一定就能稳定在需要的状态,所以接下来介绍如何通过信号展宽解决这两个问题。

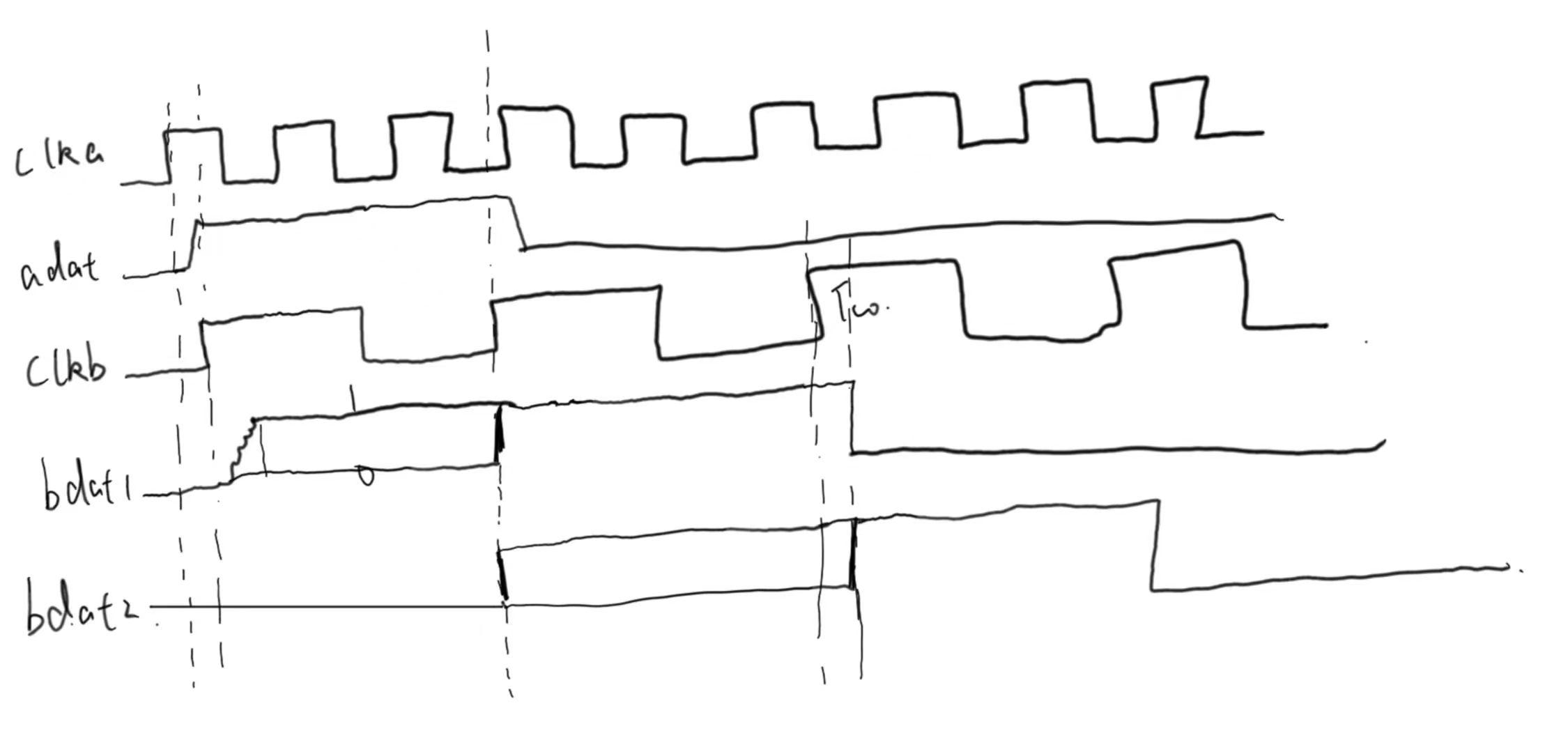

这个图看起来就相当明显,无论亚稳态定在了几,由于信号宽度是大于clkb的,所以总能采集到正确的信号,并且由于Tco远大于建立时间与保持时间,故总能将正确的信号打拍输出。

那么,如何将信号展宽呢?

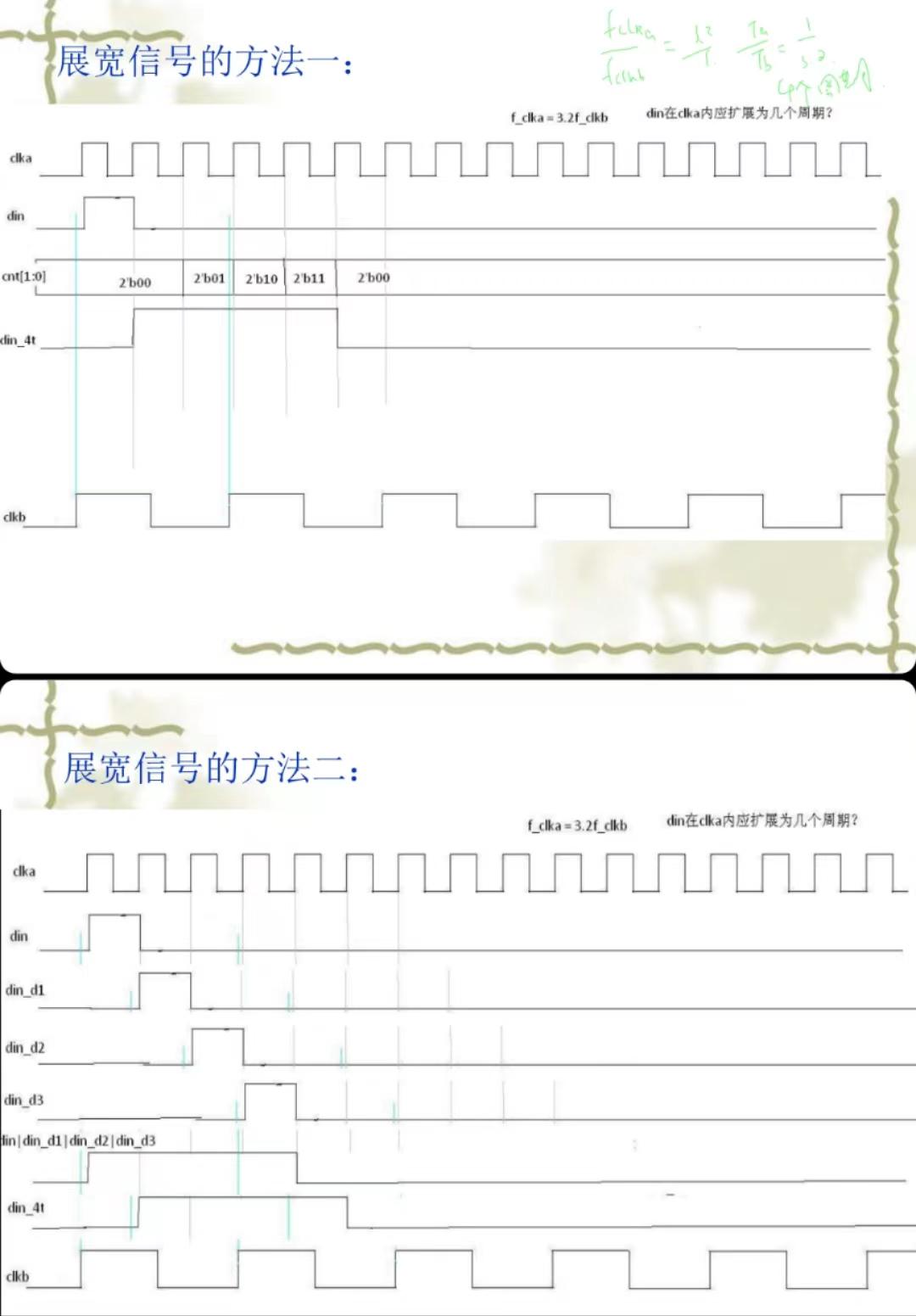

方法1、采用计数器;

方法2、将信号不断打拍然后相或;

尤其要注意,a时钟域的信号传递给b时钟域,必须要经过触发器,这是由于组合逻辑的设计可能导致毛刺的出现,如果b时钟域刚好采集到毛刺,就会导致信号出错,而如果加入触发器,就可以消除毛刺。

当时这里老师提问为什么加入触发器可以消除毛刺,而不是说加入的触发器也刚好采集到了毛刺信号,想了很久,其实答案很简单,同一个时钟下触发器根本不可能采集到毛刺,因为只要采集到了毛刺,那一定代表建立时间或者保持时间出现了违例,故做好STA的电路可以避免这个问题(当时课堂上这么简单都没想出来也很奇怪,可能还是对时序理解不够熟悉吧)。

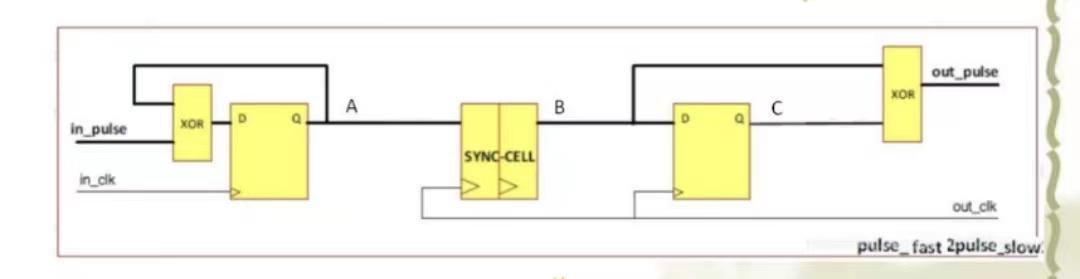

试想一下,如果在设计电路时,每次clkb的时钟频率变了,我们展宽的信号计数器和寄存次数是不是也要跟着修改?这样就很麻烦,为了解决这个问题,这里有个很经典的电路,只要将控制信号输入给这个电路处理,就可以将其转换到clkb时钟域的控制信号,电路如下图所示,这里a时钟比b时钟更快,B是打两拍过后的信号。

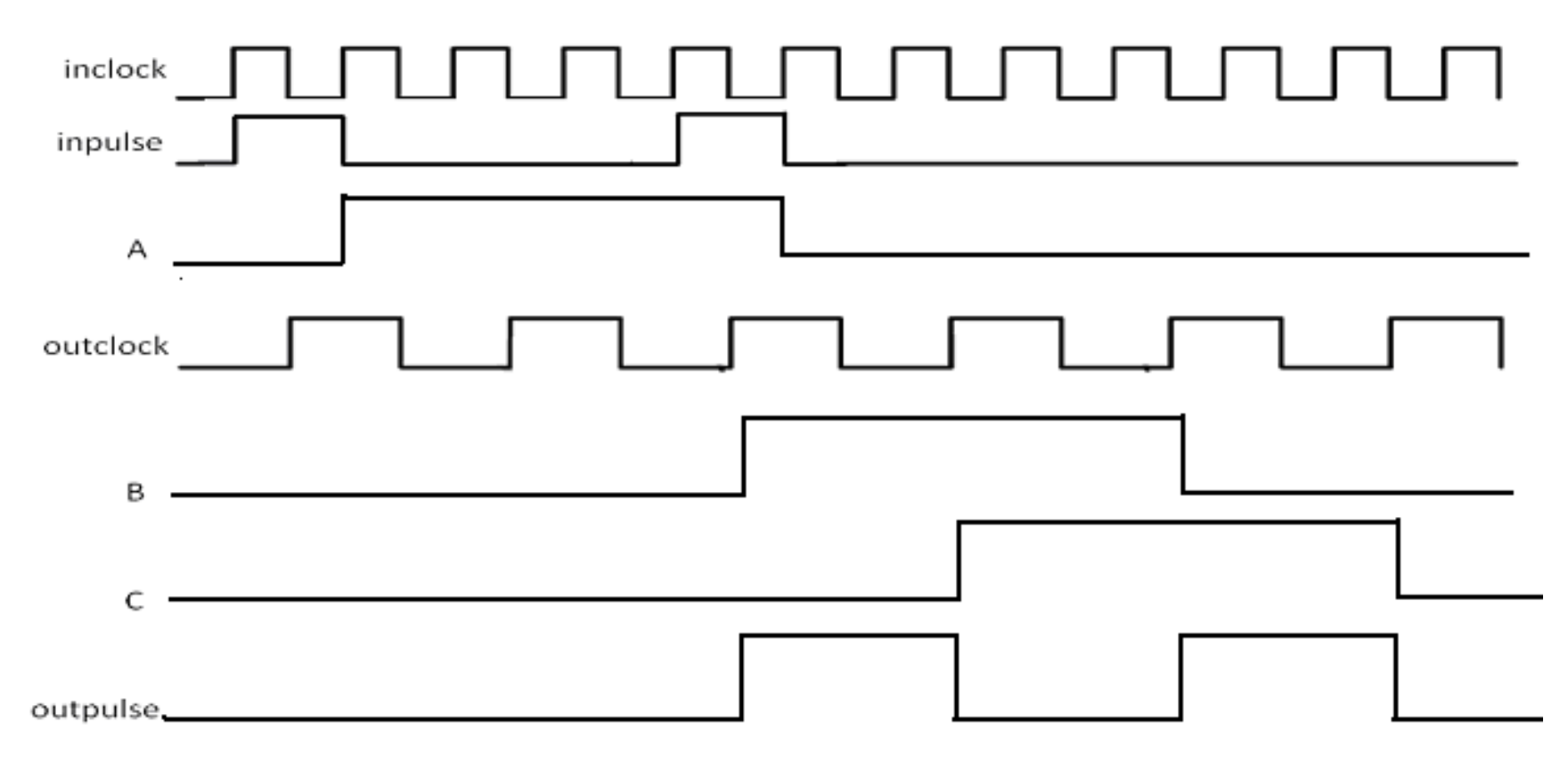

下面来分析下这个电路时序:

上图可以看出,a时钟域的控制信号被成功转移到了b时钟域。但有个条件,即inpulse必须大于outlock两个时钟周期。为什么?因为若小于两个周期,则B信号就只会出现一拍,最终无法输出两个脉冲。(这是我根据图示得到的理解,BC之间肯定要有一个周期用来做脉冲分隔的空间,所以应该是要大于两个周期的,也许有不对,留作以后思考,暂时只做记忆)。

至此,跨时钟域就回顾完了,接下来补充点异步复位同步复位的知识,这个就轻松多了。

直接总结特点:

异步复位:

无时钟依赖性

抗干扰性差

复位信号沿在时钟沿附近容易产生亚稳态

同步复位:

抗干扰性好

复位脉冲宽度大于时钟周期(这样才能被时钟采集到)

复位也可能产生亚稳态

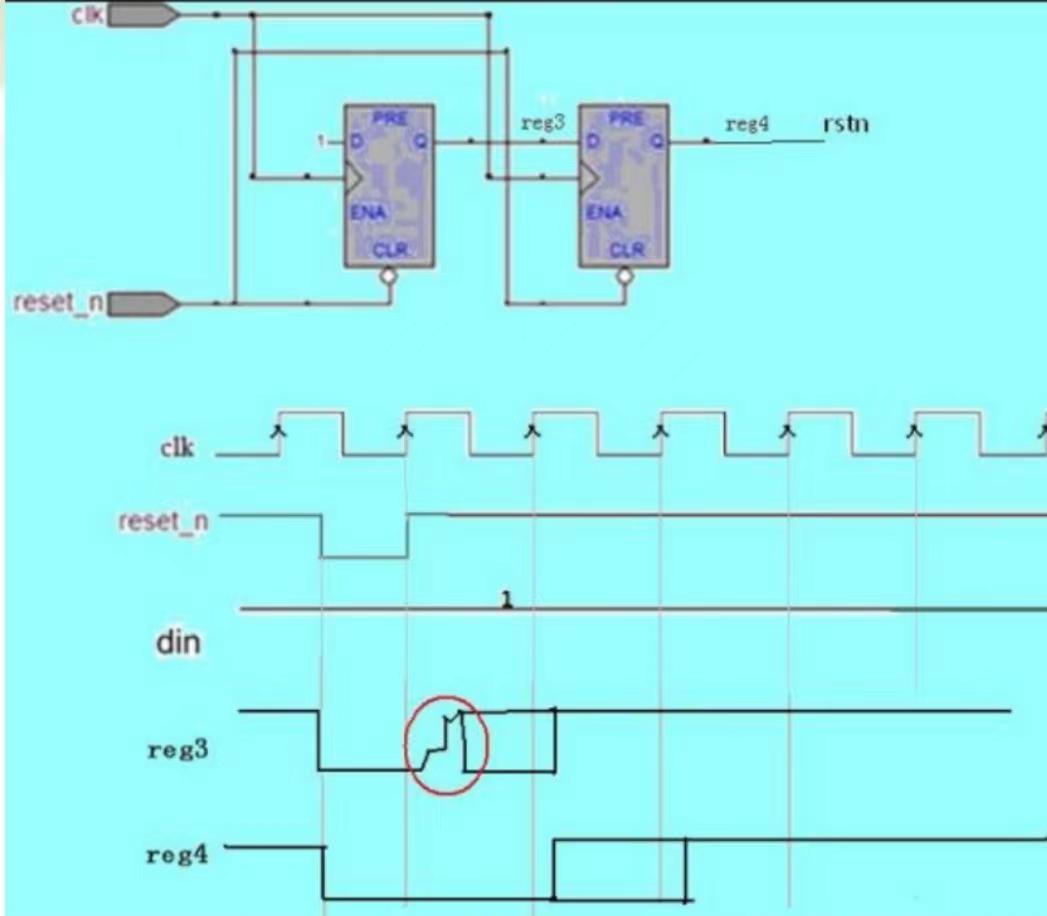

推荐使用异步复位同步释放的方式

异步复位同步释放:

抗干扰性好

不容易产生亚稳态

不依赖时钟周期

至此,关于时序优化与跨时钟域完整内容就总结完了,后面继续更新其它知识。

2383

2383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?