1)逻辑条件判断“A==B”和“A!=B”全部换成“!(A^B)”和“A^B”

2)复杂的逻辑条件判断全部单独用一个时钟去判断,如:

if(A>1000 && A<=1000000 && B>1000 && B<=10000)

改为如下:

reg Flag;

Flag <= A>1000 && A<=1000000 && B>1000 && B<=10000;

if(Flag)

这种大小判断略微还好一些,对于减法等运算一定不能在if条件中直接计算,否则会导致很差的逻辑时序;

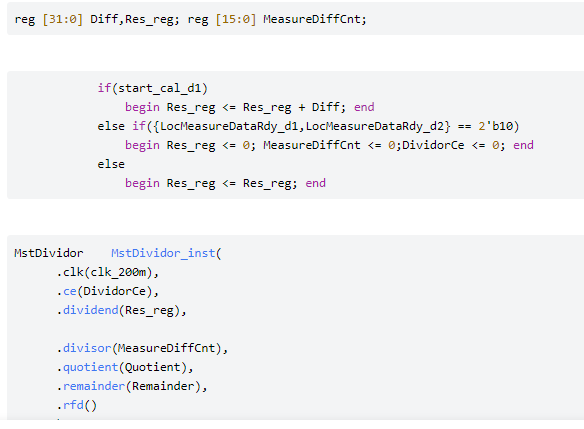

3)如果给IP核的数是经过较为复杂的运算得到的,尽量经过一级缓存后再传给IP核,如:

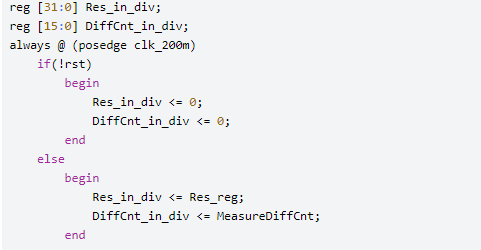

如上所示,即32bit位宽的Res_reg要经过累加运算后作为除法IP核的输入,当然这也许不算是十分复杂的计算,但对于速度较低和时钟工作较高的场合,也会对逻辑时序造成影响,因些改为如下运算:

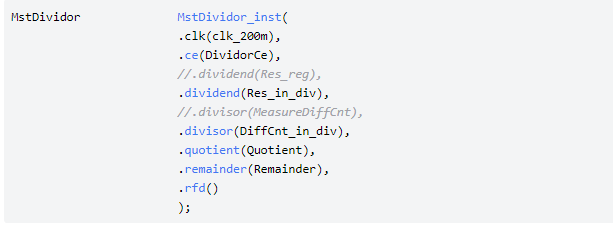

如上所示,即将计算结果进行一级缓存后再给除法IP核,这样时序会好一些……

当然有些IP核会自带缓存,那就另当别论了

4)根据我自己亲自验证,将减法运算改为等效的加法运算并不能优化逻辑时序,如下所示:

以下变量均为32位reg型,即reg [31:0]

将以下运算:

diff1 <= LocDataD2 - SlvDataD2;

diff2 <= LocDataD2 - SlvDataD1;

diff3 <= LocDataD1 - SlvDataD2;

修改为等效的以下运算:

diff1 <= (LocDataD2 + 1) + (~SlvDataD2);

diff2 <= (LocDataD2 + 1) + (~SlvDataD1);

diff3 <= (LocDataD1 + 1) + (~SlvDataD2);

最后的仿真结果会更坏,因此不建议这么做。

5)位宽越多,做运算如加、减、比较大小等耗时越大,这个可以自己用数电里学到的知识将对应的电路画出来,看看要经过多少级逻辑延时才可以得到结果,因此能用较少的位数表示时就用较少的位数吧。

6)对于HDL代码,一般都需要有一个状态机程序,即会用一个case语句控制整个程序的的流程,举个例子来说吧:

假如需要五个状态来表示:

reg [2:0] State

case(State)

3'b000:

3'b001:

3'b010:

3'b011:

3'b100:

default:

endcase

这样的判断个人认为逻辑时序会比较差,因为基本闲置了最高位,只有最后一个状态才用到了最高位,我认为按如下方式写比较好:

reg [2:0] State

case(State)

3'b111:

3'b110:

3'b101:

3'b100:

3'b011:

default:

endcase

这个我没有太多的理论依据,同样可以画出实现电路图去论证一下,反正我在仿真的时候使用后者得到了较好的逻辑时序,大家可以试一下哦。

7)对于运算级数的优化,如:

A<= A1 + A2 + A3 + A3;

优化为:

A<= (A1 + A2) + (A3 +A4);

841

841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?