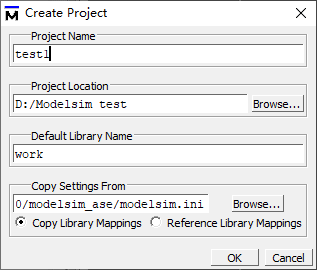

1、打开modelsim,创建新项目,选择项目保存位置,输入项目名称test1,点击OK。注意不要出现中文。

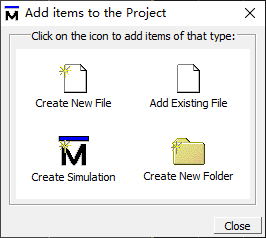

2、弹出对话框,选择新建文件

3、新建源文件,选择文件类型为Verilog,输入文件名half_add,OK。

4、新建测试文件test_bench,以顶层文件名后加_tb命名。

5、双击half_add.v,编辑源文件。

6、双击half_add_tb.v,编辑测试文件。initial中的代码用于初始化信号,只执行一遍,always中的代码则循环执行,用于产生半周期为T的信号b。

7、编译所有文件,并查看错误信息。

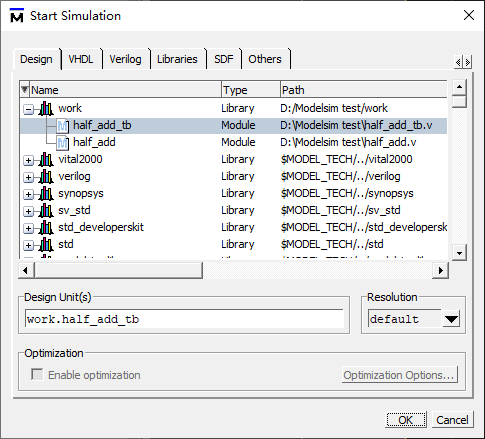

8、点击Simulation,start simulation,启动仿真,选择测试文件half_add_tb,OK。

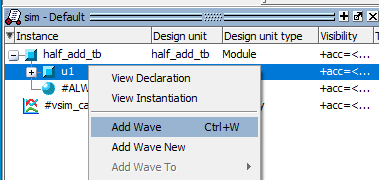

9、右击添加要查看波形的信号。

10、设置仿真时间,默认100ns

11、点击运行按钮

![]()

,查看100ns波形,也可多次点击该按钮,查看更长时间的波形,按照_tb代码对照波形。

6646

6646

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?