实验 4:半加器(⽂本输⼊设计)

⼀ 实验⽬的

1. 掌握组合逻辑电路的设计⽅法

2. 掌握Quartus II软件⽂本输⼊设计的流程

⼆ 实验内容

2.1 设计输⼊

1. 模块名称:Hadder

2. 输⼊输出:A,B,Sum,C

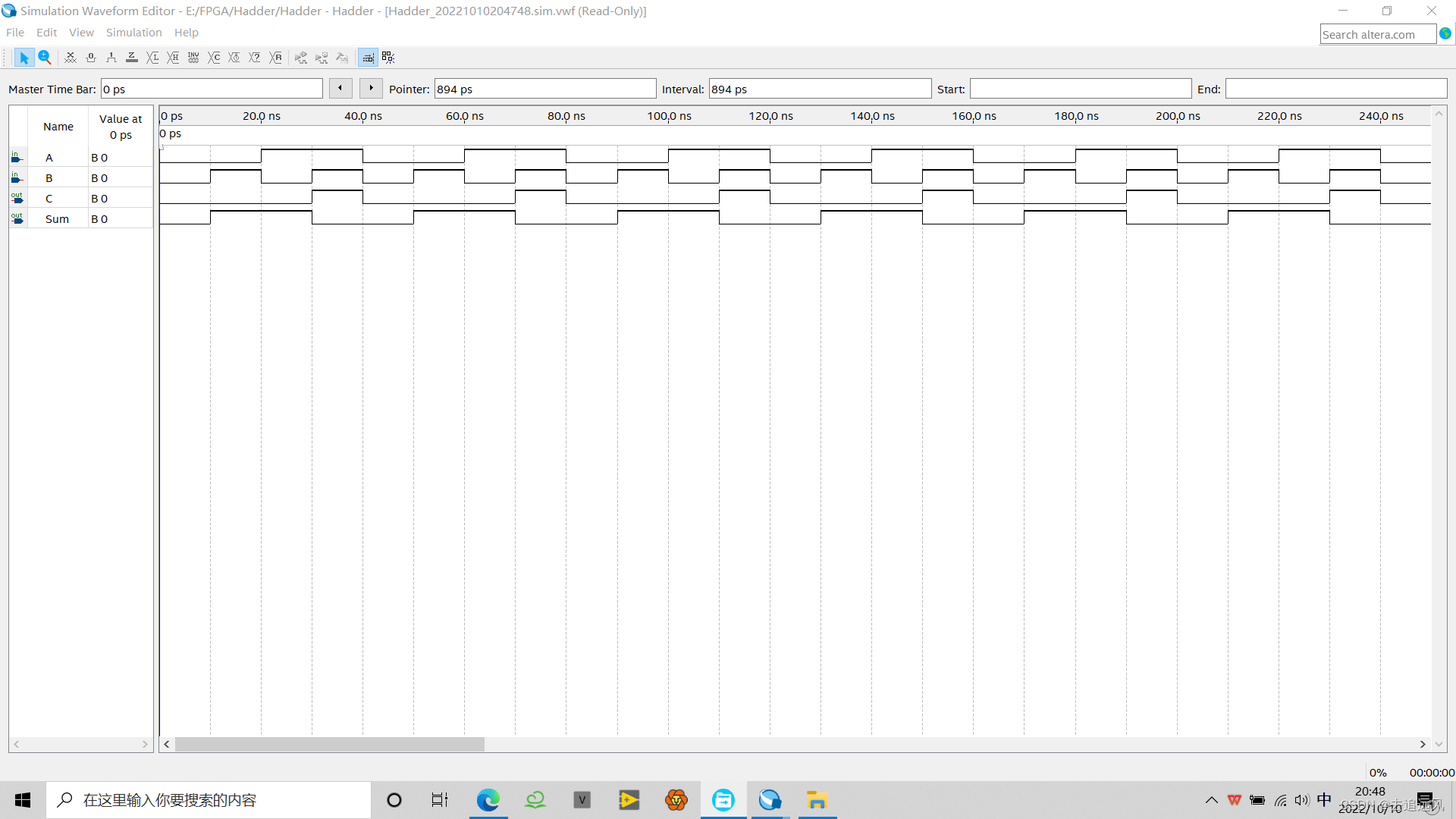

2.2 电路仿真1. 激励⽂件的输⼊为00~11

2. 功能仿真

三 实验报告

1. 设计代码

2. 仿真结果

3. 报告中附代码和仿真结果截图

实验注意事项:模块名称、实体名称、⽂件名称必须⼀致

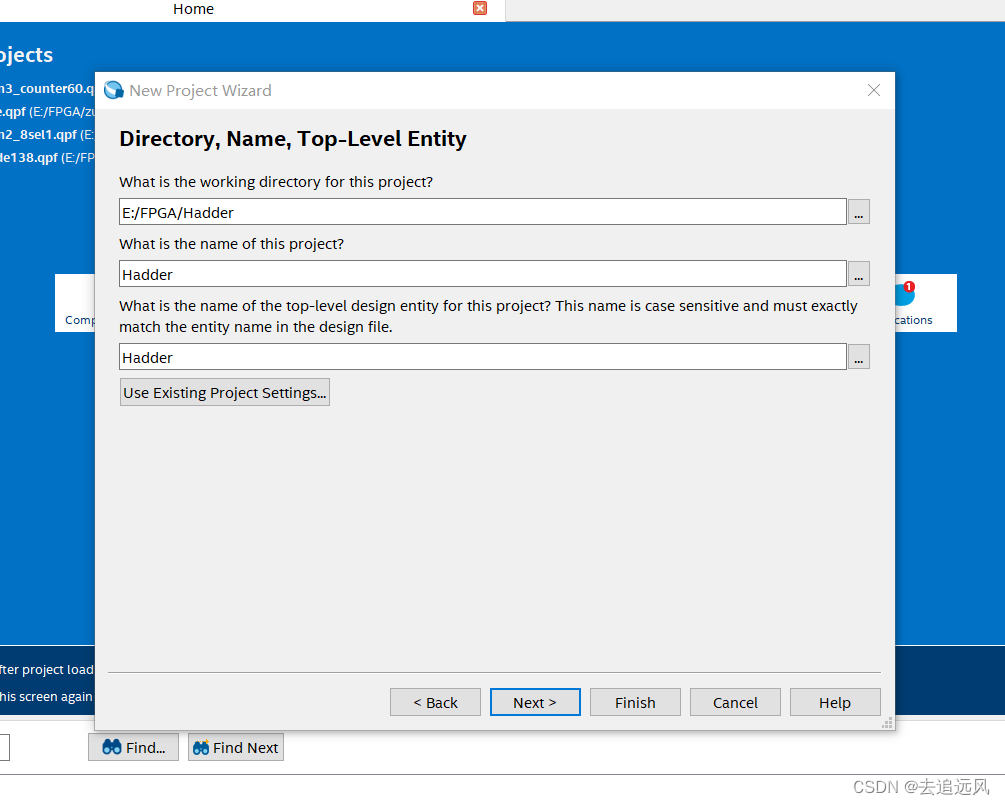

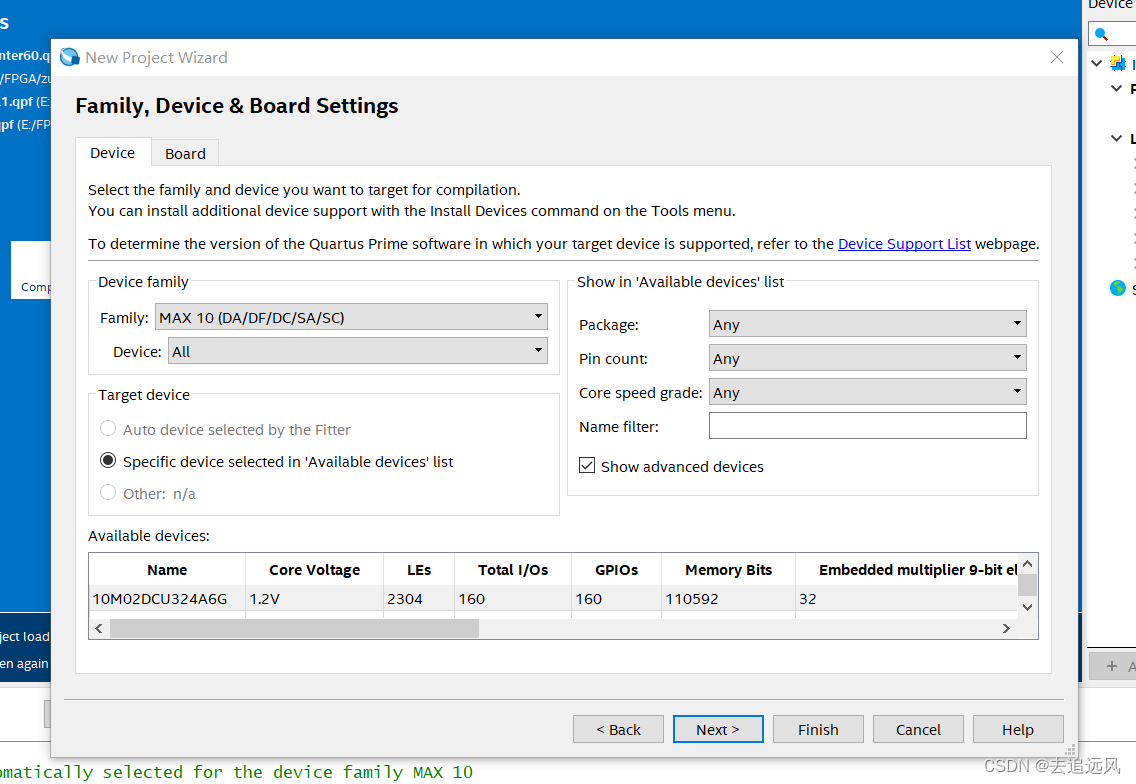

1.路径设置&器件选择

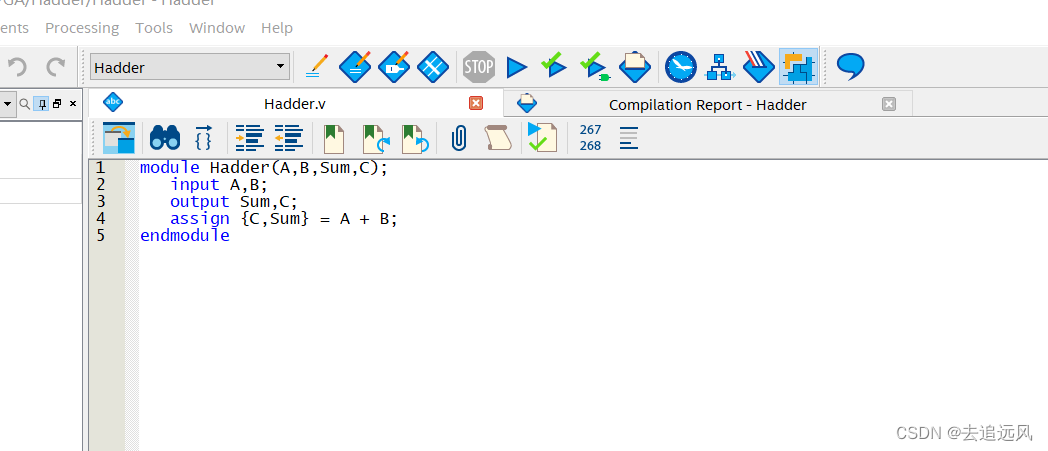

2.创建Verilog程序&编译

module Hadder(A,B,Sum,C);

input A,B;

output Sum,C;

assign {C,Sum} = A + B;

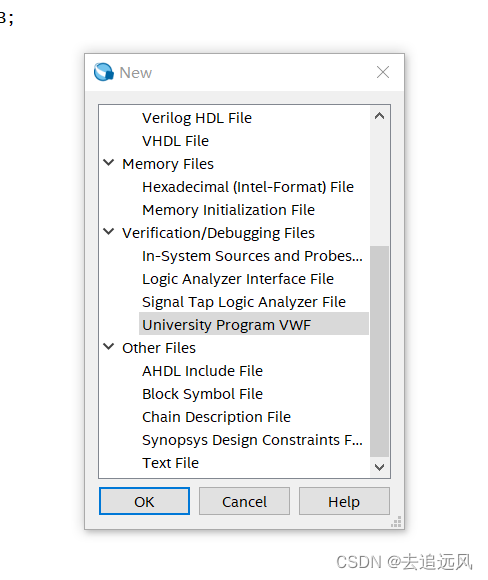

endmodule 3.创建VWF文件&功能仿真

半加器的输入是A和B,分别从00~11进行相加,得出C和Sum的值

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?