verilog实现半加器、全加器、多位全加器

1、简介

好的,半加器、全加器和多位全加器的实现方法如下:

半加器(Half Adder):

- 输入:A、B两个1位二进制输入

- 输出:Sum(和)、Cout(进位)

- 实现:Sum = A XOR B; Cout = A AND B

- 即通过异或门和与门组合实现加法

全加器(Full Adder):

- 输入:A、B两个1位二进制输入,Cin(进位输入)

- 输出:Sum、Cout

- 实现:Sum = A XOR B XOR Cin; Cout = (A AND B) OR (Cin AND A) OR (Cin AND B)

- 在半加器基础上增加进位输入,通过组合逻辑生成和值和进位

多位全加器:

- 将多个全加器级联,每个全加器代表一个位的加法

- 每个后续全加器的Cin连接前一级全加器的Cout

- 最后一个全加器的Cout作为多位加法的最终进位输出

- 通过这种级联方式可以实现任意位宽的二进制加法运算

多位全加器的连接方法可以扩展位宽,是构建多位加法器和ALU的基础。这些加法器的组合逻辑设计展示了如何用基本逻辑门实现简单功能。

2、代码:

半加器:

module halfadder(

input wire a,

input wire b,

output wire cout,

output wire sum

);

assign cout = a&b;

assign sum = a^b;

endmodule

一位全加器

module adder(

input wire a,

input wire b,

input wire cin,

output wire cout,

output wire sum

);

assign cout = (a&b)|(a&cin)|(b&cin);

assign sum = a^b^cin;

endmodule

多位全加器,我这里是十位,多位都可以,把10改成你要的位数就行了

module adder100(

input wire[9:0] a,

input wire[9:0] b,

output reg[9:0] cout,

output reg[9:0] sum

);

integer i;

always @(*) begin

for(i = 0;i<10;i=i+1'b1)begin

if(i == 0)begin

{cout[0],sum[0]} = a[0]+b[0];

end

else begin

{cout[i],sum[i]} = a[i] + b[i] + cout[i-1];

end

end

end

endmodule

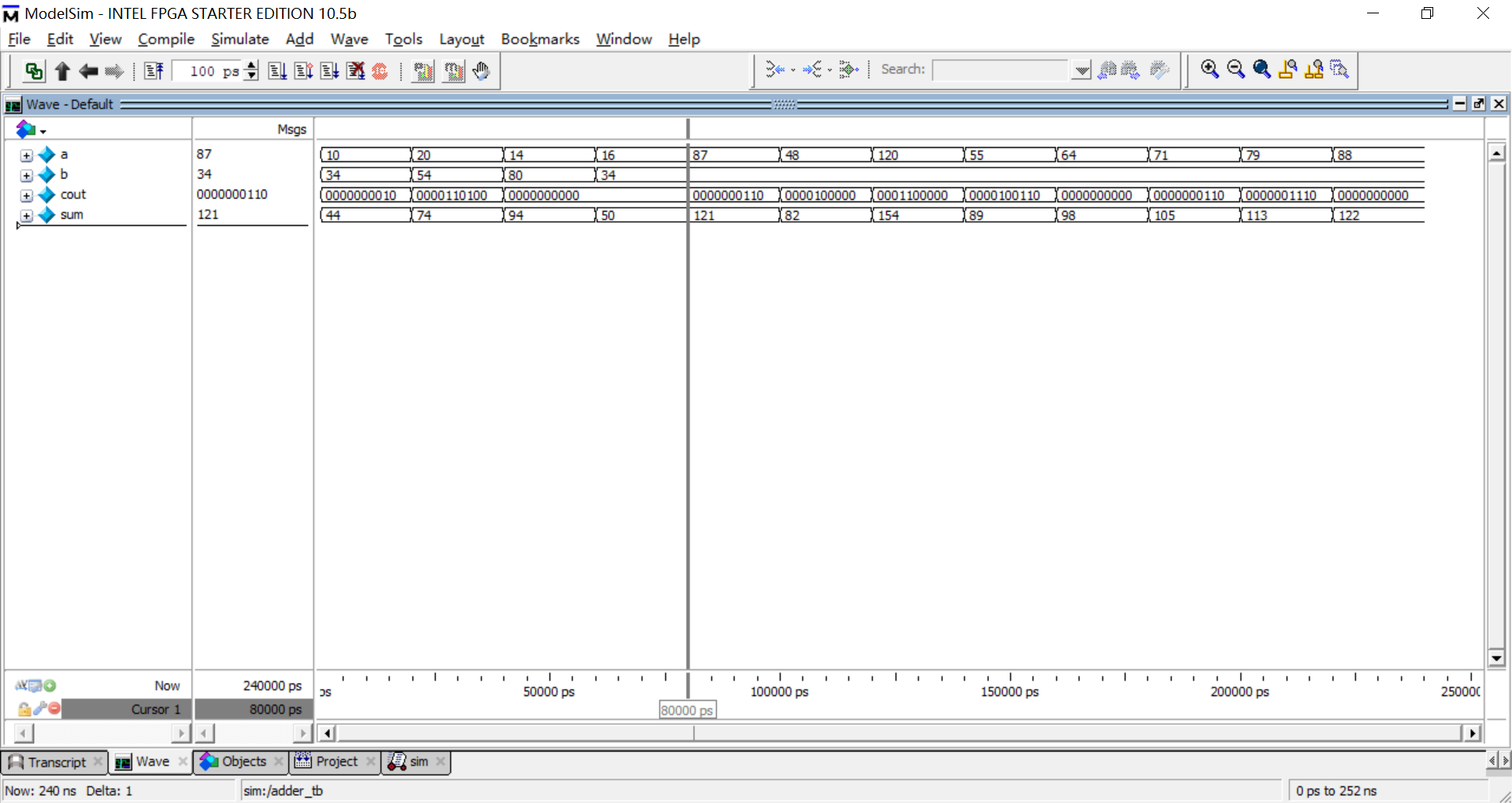

3、仿真程序

我这里比较懒,就放出来多位全加器的了

`timescale 1ns/1ns

module adder_tb();

reg[9:0] a;

reg[9:0] b;

wire[9:0] cout;

wire[9:0] sum;

initial begin

a = 10'd10;

b = 10'd34;

#20;

a = 10'd20;

b = 10'd54;

#20;

a = 10'd14;

b = 10'd80;

#20;

a = 10'd16;

b = 10'd34;

#20;

a = 10'd87;

b = 10'd34;

#20;

a = 10'd48;

b = 10'd34;

#20;

a = 10'd120;

b = 10'd34;

#20;

a = 10'd55;

b = 10'd34;

#20;

a = 10'd64;

b = 10'd34;

#20;

a = 10'd71;

b = 10'd34;

#20;

a = 10'd79;

b = 10'd34;

#20;

a = 10'd88;

b = 10'd34;

#20;

end

adder100 inst_adder100 (.a(a),

.b(b),

.cout(cout),

.sum(sum));

endmodule

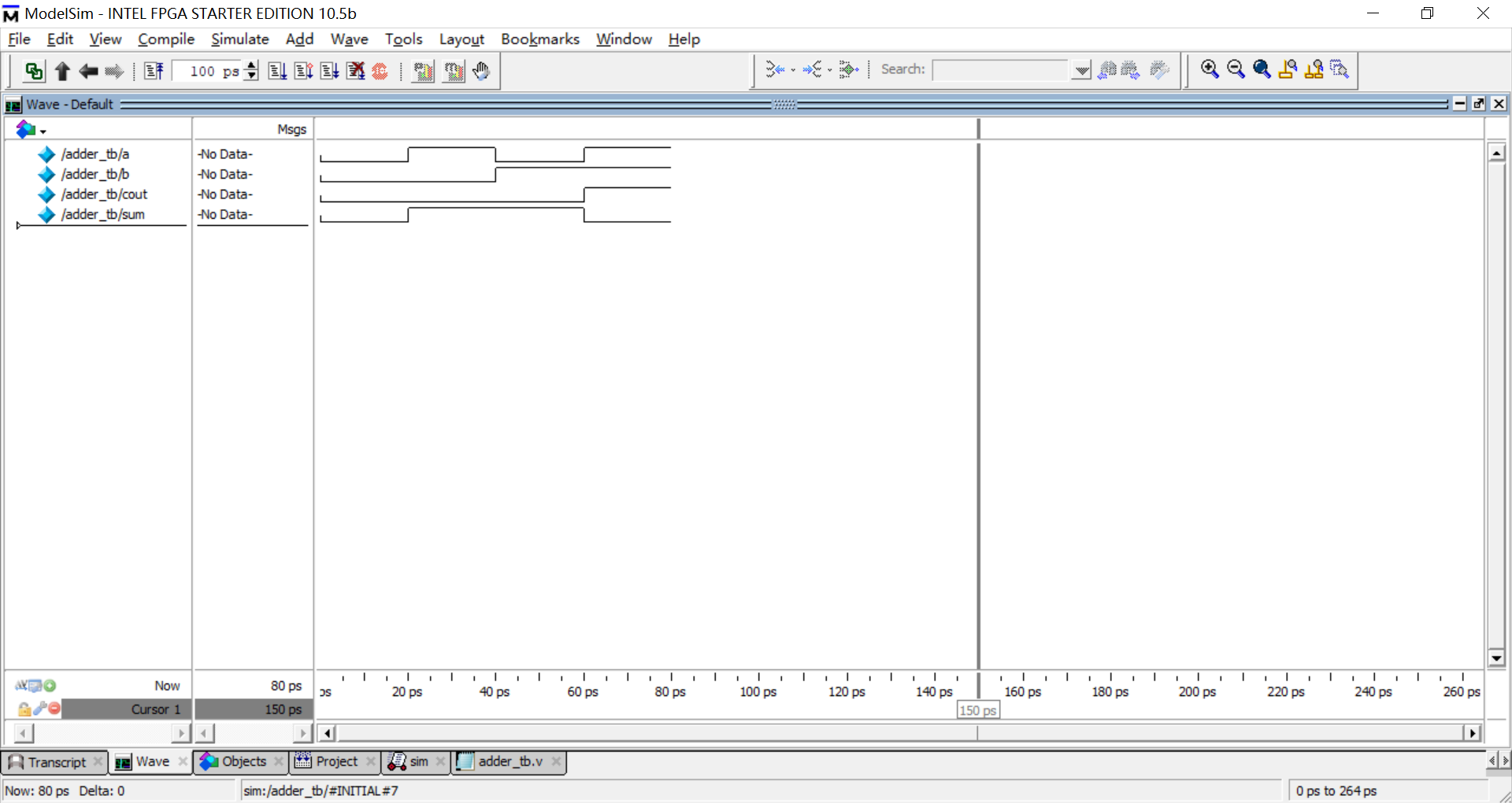

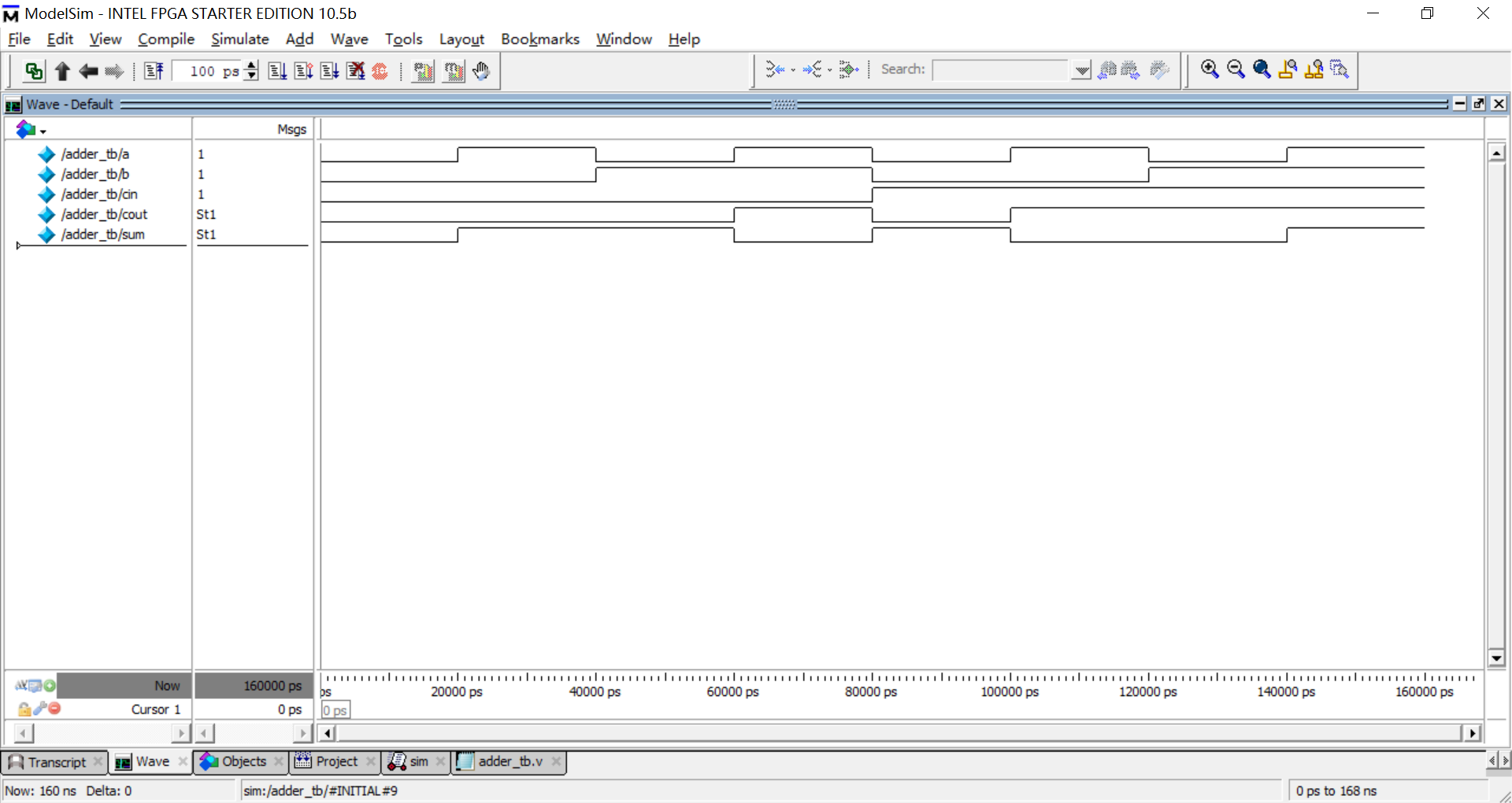

4、仿真结果

课后练习

半加器:

一位全加器:

多位全加器:

2420

2420

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?