1.概念

对于几乎所有的微控制器,中断都是一种常见的特性。中断一般是由硬件(如外设和外部输入引脚)产生的事件,它会引起程序流偏离正常的流程(如给外设提供服务),转去执行其他的流程。

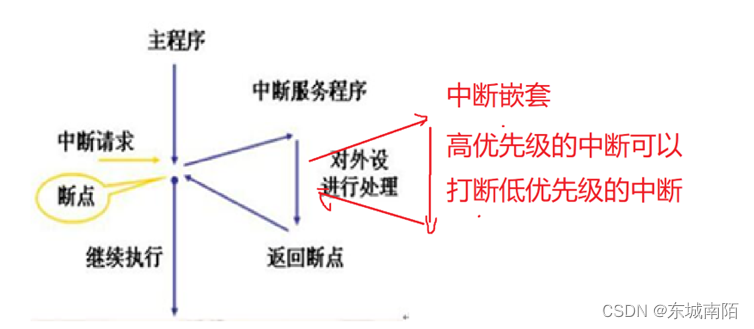

CPU在正常执行程序的过程中,由于内部/外部事件的触发或程序的预先安排引起CPU暂停当前正在运行的程序,而转去执行中断服务子程序,待中断服务子程序执行完毕后,CPU继续执行原来的程序,这一过程称为中断;

2.中断执行过程

图1 中断执行过程说明

1、外设发出中断请求

2、处理器暂停当前执行的任务,保护现场(拓展:CPU内部有R0-R15寄存器,中断发生时会保存里边的值),将当前位置的PC地址压栈;

3、程序跳转到中断服务程序,执行中断服务程序;

4、恢复现场,将栈顶的值回送给PC;

5、跳转到被中断的位置开始执行下一个指令

中断服务函数:相对于正常子函数,中断服务函数有以下需要注意的地方:

1、中断服务函数不能传入参数;

2、中断服务函数不能有返回值;

3、中断服务函数应该做到短小精悍,快入快出,禁止延时性的过程。

4、不要在中断函数中使用printf函数,会带来重入和性能问题,不要出现浮点运算。

printf是一个无法重入的函数:

中断重入:就是在一个中断程序执行过程中又被另一个中断打断,转而又去执行另一个中断程序。

3.中断的部分专业术语

中断源:引起中断的原因,或者能够发出中断请求信号的来源统称为中断源

中断优先级:中断同时到来,谁先执行。数字越小,优先级越高。

中断响应:中断事件发生,Cortex-M3内核准备执行该事件,即为中断响应。

中断嵌套:可嵌套的内核 -- 中断可以被其他中断打断。(Cortex-M)

不可嵌套的内核 -- 不可以打断。

中断挂起:中断事件发生了,但是Cortex-M内核还没准备去执行。

中断服务函数: 中断发生后,要执行的程序。(固定格式

文章详细阐述了微控制器中的中断概念,包括中断的执行过程、中断服务函数的注意事项、中断的相关专业术语如中断源、中断优先级等。特别讨论了STM32中的中断分类和优先级管理,强调了中断的使能和EXTI中断配置。此外,还介绍了中断优先级的抢占和响应优先级机制。

文章详细阐述了微控制器中的中断概念,包括中断的执行过程、中断服务函数的注意事项、中断的相关专业术语如中断源、中断优先级等。特别讨论了STM32中的中断分类和优先级管理,强调了中断的使能和EXTI中断配置。此外,还介绍了中断优先级的抢占和响应优先级机制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7904

7904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?