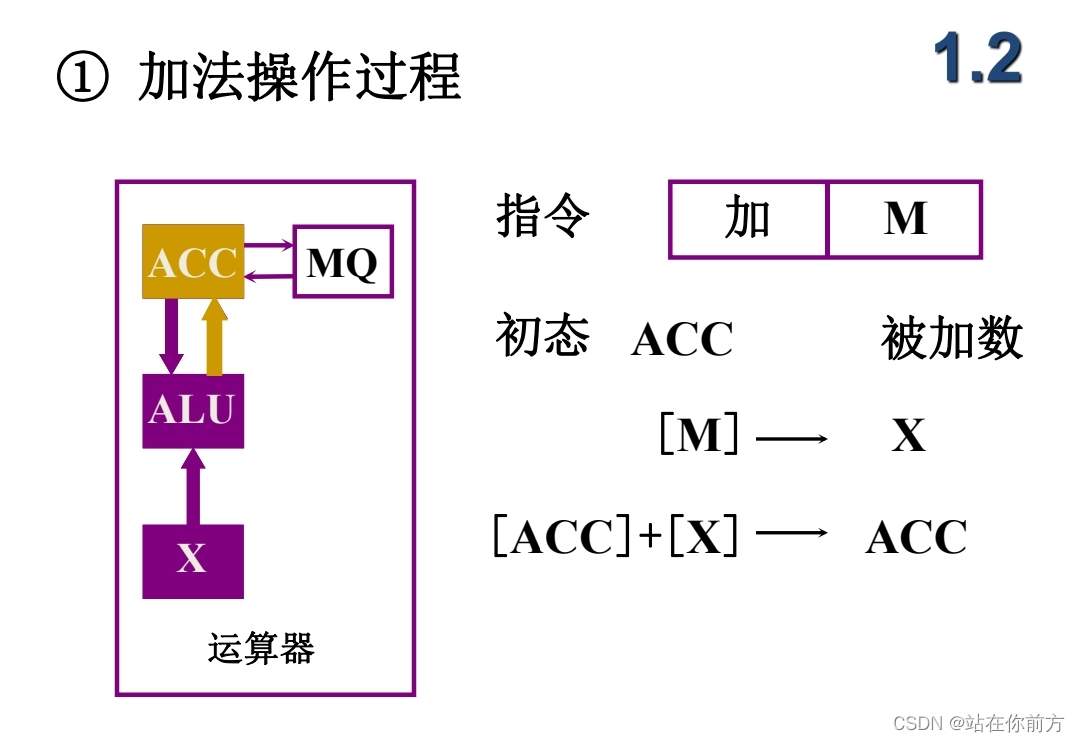

- 加法操作过程

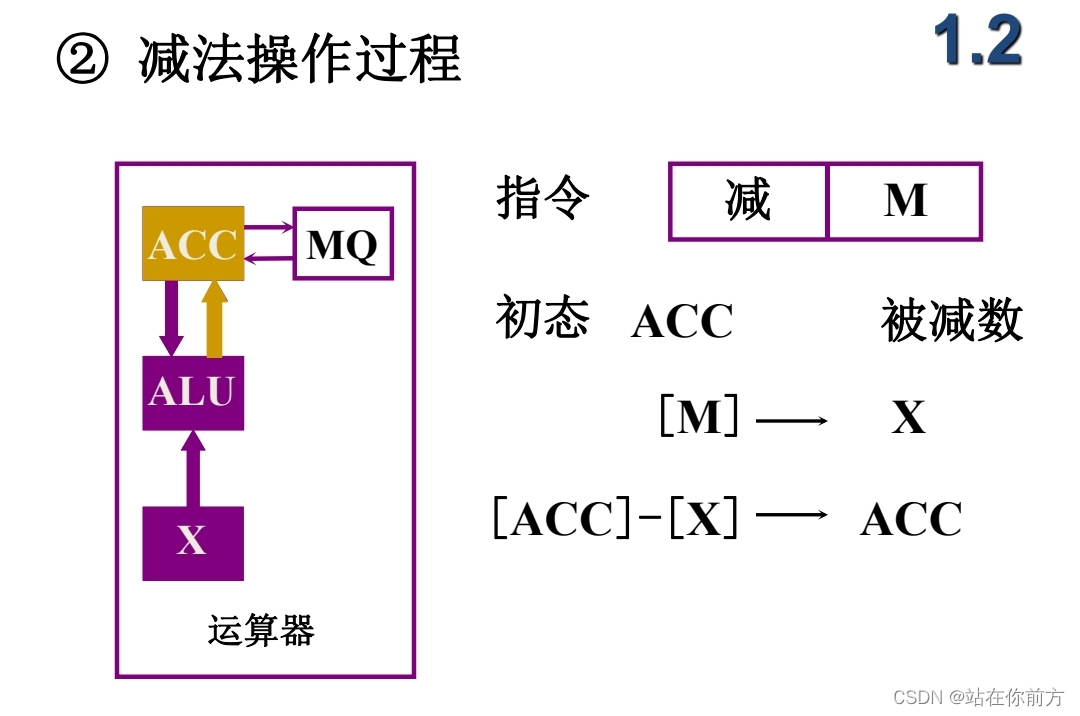

- 减法操作过程

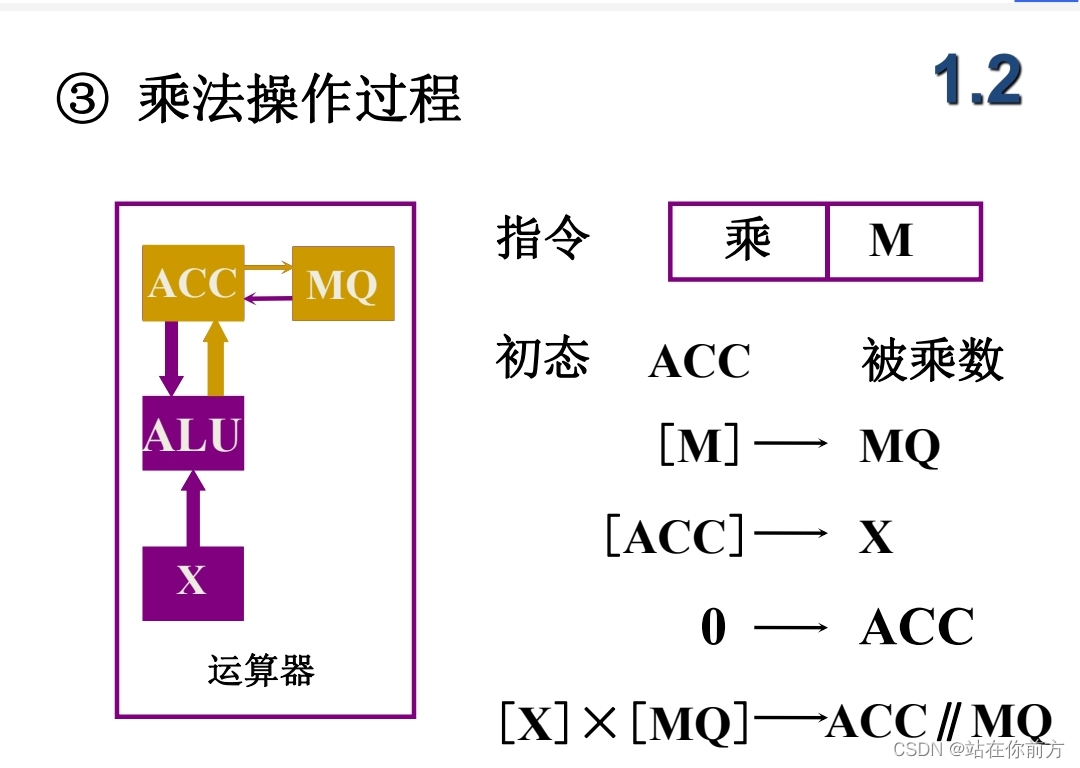

- 乘法操作过程

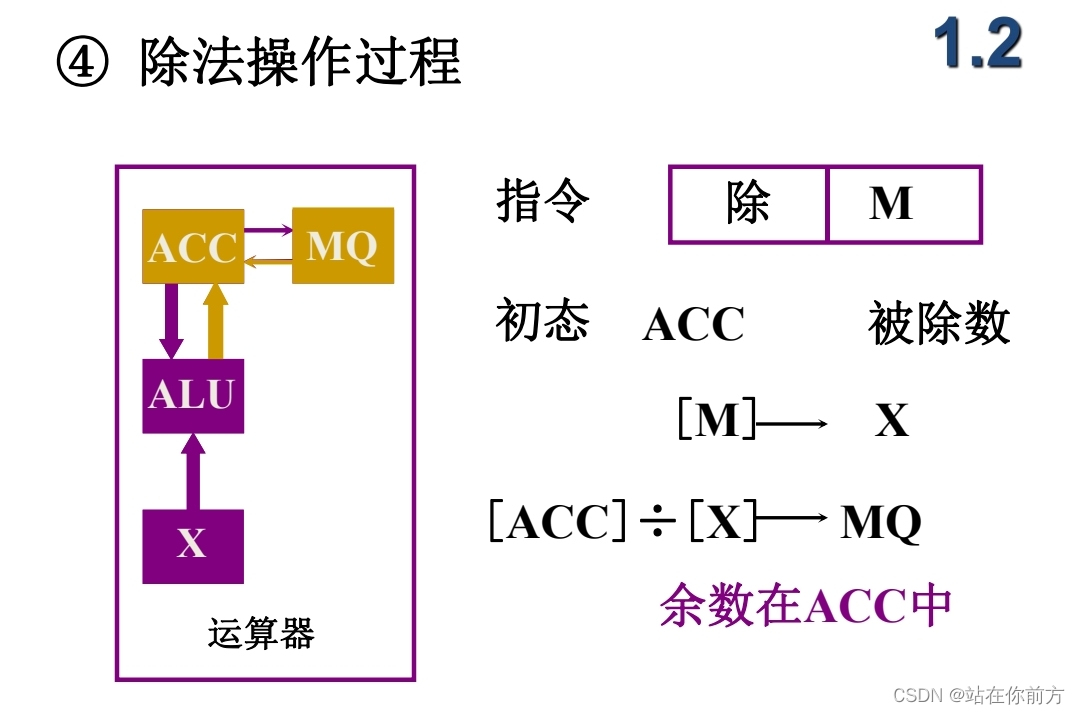

- 除法操作过程

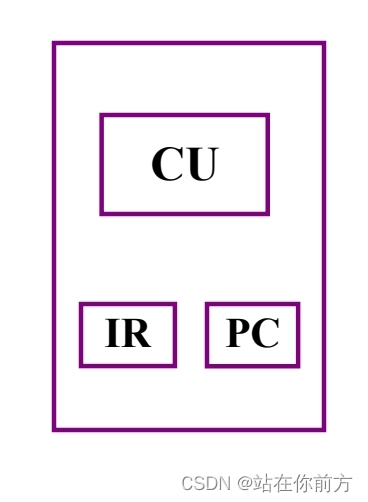

(3) 控制器主要基本组成

完成一条指令

- 取指令PC

- 分析指令IR

- 执行指令CU

PC:存放当前欲执行指令的地址,具有计数功能(PC)+1->PC

IR:存放当前欲执行的指令

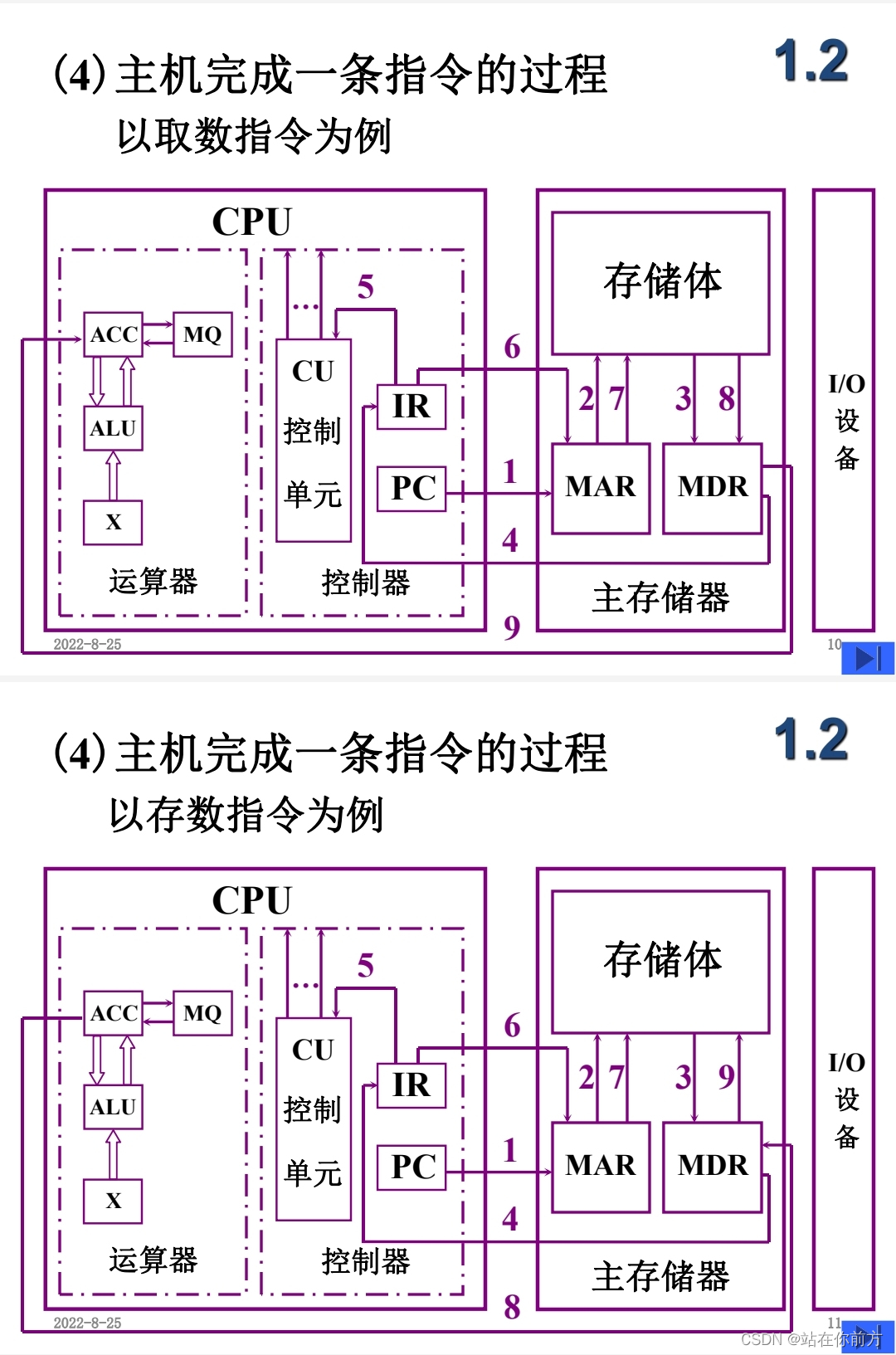

(4)主机完成一条指令的过程

(5)ax^2+bx+c程序的运行过程

- 将程序通过输入设备送至计算机

- 程序首地址->PC

- 启动程序运行

- 取指令PC->MAR->M->MDR->IR,(PC)+1->PC

- 分析指令OP(IR)->CU

- 执行指令AD(IR)->MAR->M->MDR->ACC

- 打印结果

- 停机

计算机硬件的主要技术指标

- 机器字长:CPU一次能够处理数据的位数,与CPU中的寄存器位数有关

- 运算速度

- 主频

- 吉普森法

- MIPS:每秒执行百万条指令

- FLOPS:每秒执行浮点运算次数

- CPI:执行一条指令所需时钟周期数

- 存储容量:存放二进制信息的总位数

- 主存容量

- 存储单元个数×存储字长

- 字节数 1KB

- 辅存容量

- 字节数 80GB

- 主存容量

| MAR | MDR | 容量 |

|---|---|---|

| 10 | 8 | 1K×8位 |

| 16 | 32 | 64K×32位 |

计算机系统的设计和分析

- 成本和价格

- 基准测试程序

- 量化设计的基本准则

- 成本和价格

- 商品的标价(价格)由这样一些因素构成

- 原料成本

- 直接成本

- 毛利

- 折扣

- PC的成本和价格

成本-时间因素:学习曲线

- 产品价格随时间变化的特征,就是价格随时间下降的趋势

- 基准测试程序

- 性能与测试程序的执行时间有关,那么用什么做测试程序呢

- 五类测试程序

- 真实程序

- 修正(或脚本化)应用程序

- 核心程序

- 小测试程序

- 合成测试程序

- 测试程序包(组件)

- 选择一组各个方面由代表性的测试程序组成

- 尽可能全面的测试了一个计算机系统的性能

测试程序包www.SPEC.org

- 基于NUIX,诞生于20世纪80年代

- 由真实程序和核心程序组成

- 采用C和Fortran语言,后增加C++

- 包括整数部分SPECint和浮点部分SPECfp

- 量化设计的基本原则

- 大概率事件优先原则

- 追求全局的最优结果

- Amdahi定律

- 系统性能加速化,受限于该部件在系统中在系统中所占的重要性

- 可以定量计算

- 程序的局部性原理

- 程序执行时所访问存储器在时-空上是相对的簇聚

- 这种簇聚包括指令和数据两部分

(1)大概率事件优先的原则

- 对于大概率事件(最常见的事件),赋予它优先的处理权和资源使用权,以获得全局的最优结果

- 要能够确定什么是大概率事件,同时要说明针对该事件进行的改进将如何提高机器的性能

- 好钢用在刀刃上,事半功倍

(2)Amdahi定律

- 假设我们对机器(部件)进行某种改进,那么机器系统(部件)的加速比就是

- 系统加速比=改进后性能/改进前性能=改进前总执行时间/改进后总执行时间

- 核心概念:时间

- 系统加速比告诉我们改进后的机器比改进前快多少

- 系统加速比依赖于两个因素

- 可改进比例:可改进部分在源系统计算时间中所占的比例,它总是小于等于1的

- T0/T1

- 部件加速比:可改进部分改进以后的性能提高,一般情况它是大于1的

- T1/T2

- 可改进比例:可改进部分在源系统计算时间中所占的比例,它总是小于等于1的

- 部件改进后,系统的总执行时间等于不可改进部分的执行时间加上可改进部分改进后的执行时间

- 总执行时间

- =(1-可改进比例)×改进前总执行时间+[可改进比例×改进前总执行时间/部件加速比]

- =改进前总执行时间×[(1-可改进比例)+可改进比例/部件加速比]

- 系统加速比为改进前与改进后总执行时间之比

- 系统加速比

- =改进前总执行时间/改进后总执行时间

- 1/[(1-可改进比例)+可改进比例/部件加速比]

- 性能增加的递减规则

- 仅仅对计算机中的一部分做性能改进,则改进越多,系统获得的效果越小

- 针对整个任务的一部分进行优化,则最大加速比不大于

- 1/(1-可改进比例)

- Amdahi定律衡量一个好的计算机系统

- 具有高性能价格比的计算机系统是一个带宽平衡的系统,而不是看它使用某些部件的性能

(3)程序局部性

- 程序访问地址的分布不是随机的,而是相对的簇聚

- 包括时间局部性和程序的空间局部性

- 程序的时间局部性

- 程序即将用到的信息很可能就是目前正在使用的信息

- 程序的空间局部性

- 程序即将用到的信息很可能与目前正在使用的信息在空间上相邻或者临近

- 其他局部性

- 生产-消费局部性

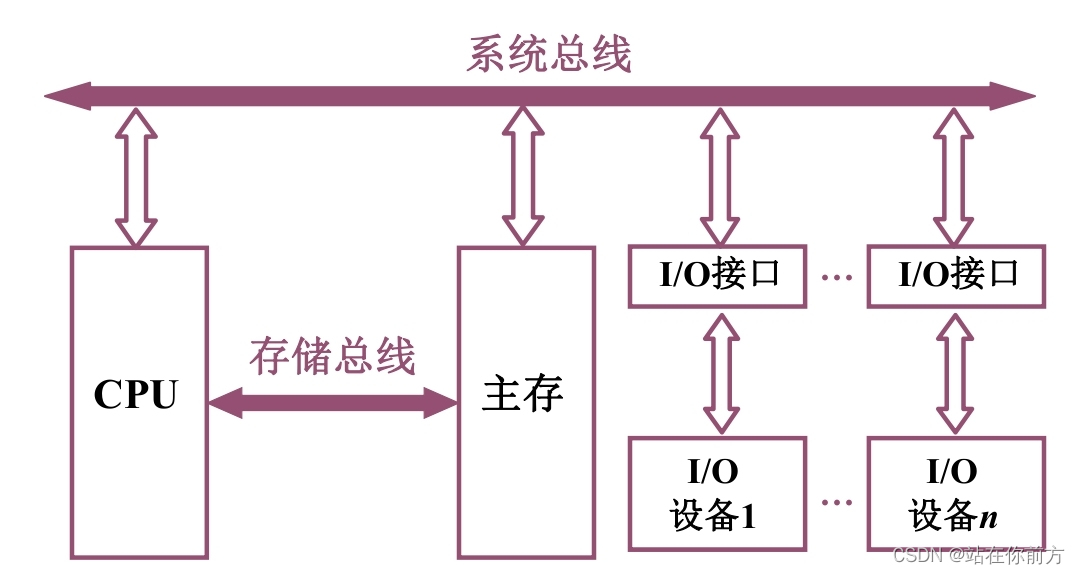

系统总线

总线的基本概念

(一)为什么用总线

(二)什么是总线

- 总线是连接各个部件的信息传输线

- 是各个部件共享的传输介质

(三)总线上信息的传输

- 串行

- 并行

(四)总线结构的计算机举例

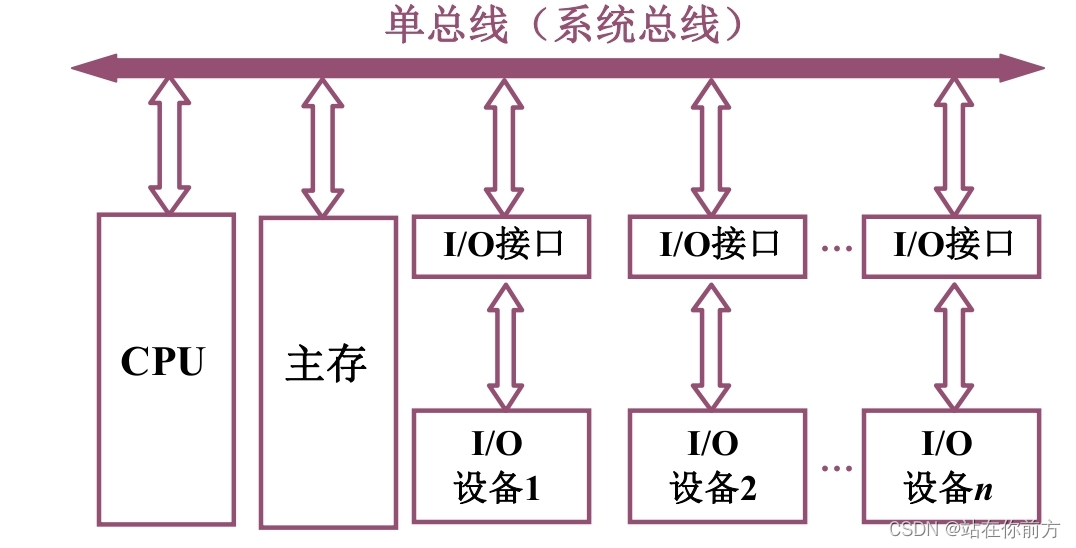

- 单总线结构框图

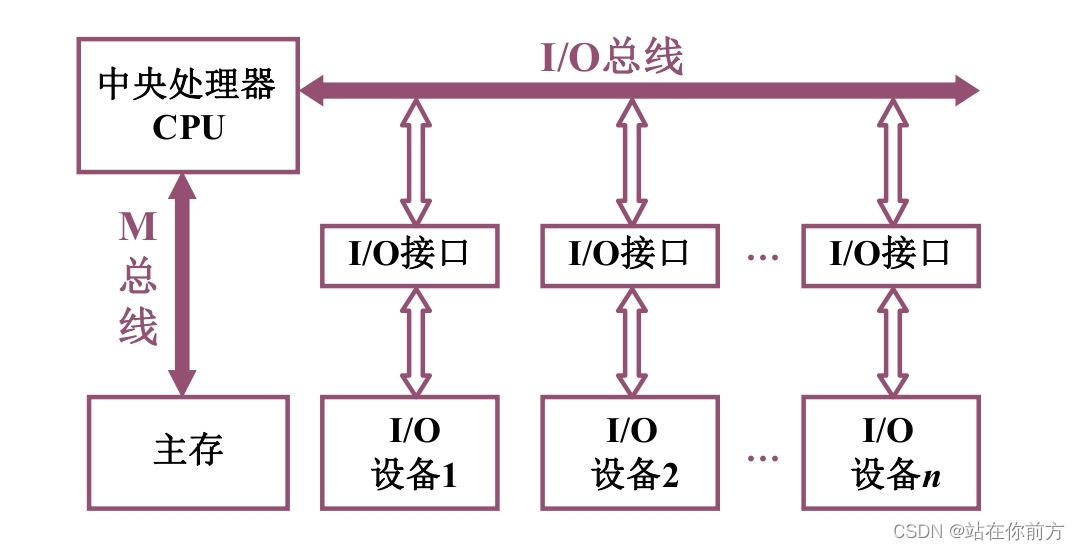

- 面向CPU的双总线结构框图

- 以存储器为中心的双总线结构框图

总线的分类

- 片内总线:芯片内部的总线

- 系统总线:计算机各部件直接的信息传输线

- 数据总线:双向,与机器字长存储字长有关

- 地址总线:单向,与存储地址,I/O地址有关

- 控制总线:有出有入

- 入:中断请求,总线请求

- 出:存储器读,存储器写,总线允许,中断确认

- 通信总线

- 用于计算机系统之间或计算机系统和其他系统(如控制仪表,移动通信)之间的通信

- 传输方式

- 串行通信总线

- 并行通信总线

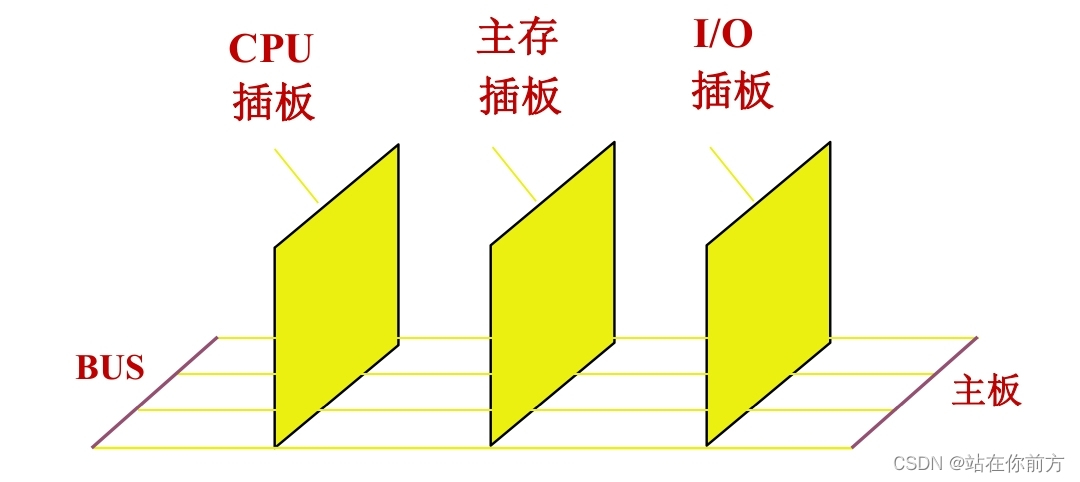

总线特性和性能指标

(一)总线物理实现

(二)总线特性

- 机械特性

- 尺寸,形状,管脚数,排列顺序

- 电气特性

- 传输方向和有效的电平范围

- 功能特性

- 每根传输线的功能

- 地址

- 数据

- 控制

- 时间特性

- 信号的时序关系

(三)总线的性能指标

- 总线宽度

- 数据线的根数

- 标准传输率

- 每秒传输的最大字节数

- 时钟同步/异步

- 同步,不同步

- 总线复用

- 数据线与地址线复用

- 信号线数

- 地址线,数据线和控制线的总和

- 总线控制方式

- 突发,自动,仲裁,逻辑,计数

- 其他指标

- 负载能力

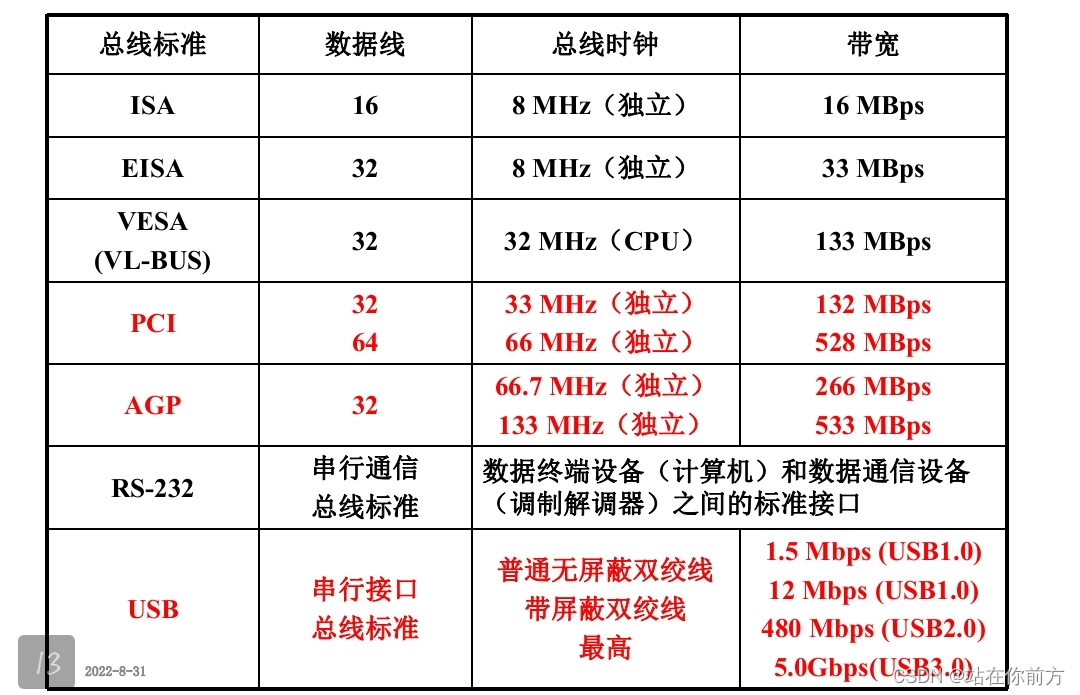

(四)总线标准

常见的总线标准

- ISA(Industry Standard Architecture)总线

- 支持24位地址线

- 支持8位PC/16位(PC/AT)数据线

- 总线时钟频率8MHz

- 用于80286计算机

- EISA(Extended ISA)总线

- 支持32位地址线和数据线

- 总线时钟频率8MHz

- DMA方式下可达33MB/s传输速率

- 用于80386/80486计算机

- VL-BUS(VESA Local Bus)总线

- 与EISA兼容,外加主存总线以实现高速传输总线时钟频率与CPU外频同步,主存总线驱动能力有限,最多接3个扩展卡 用于80486计算机

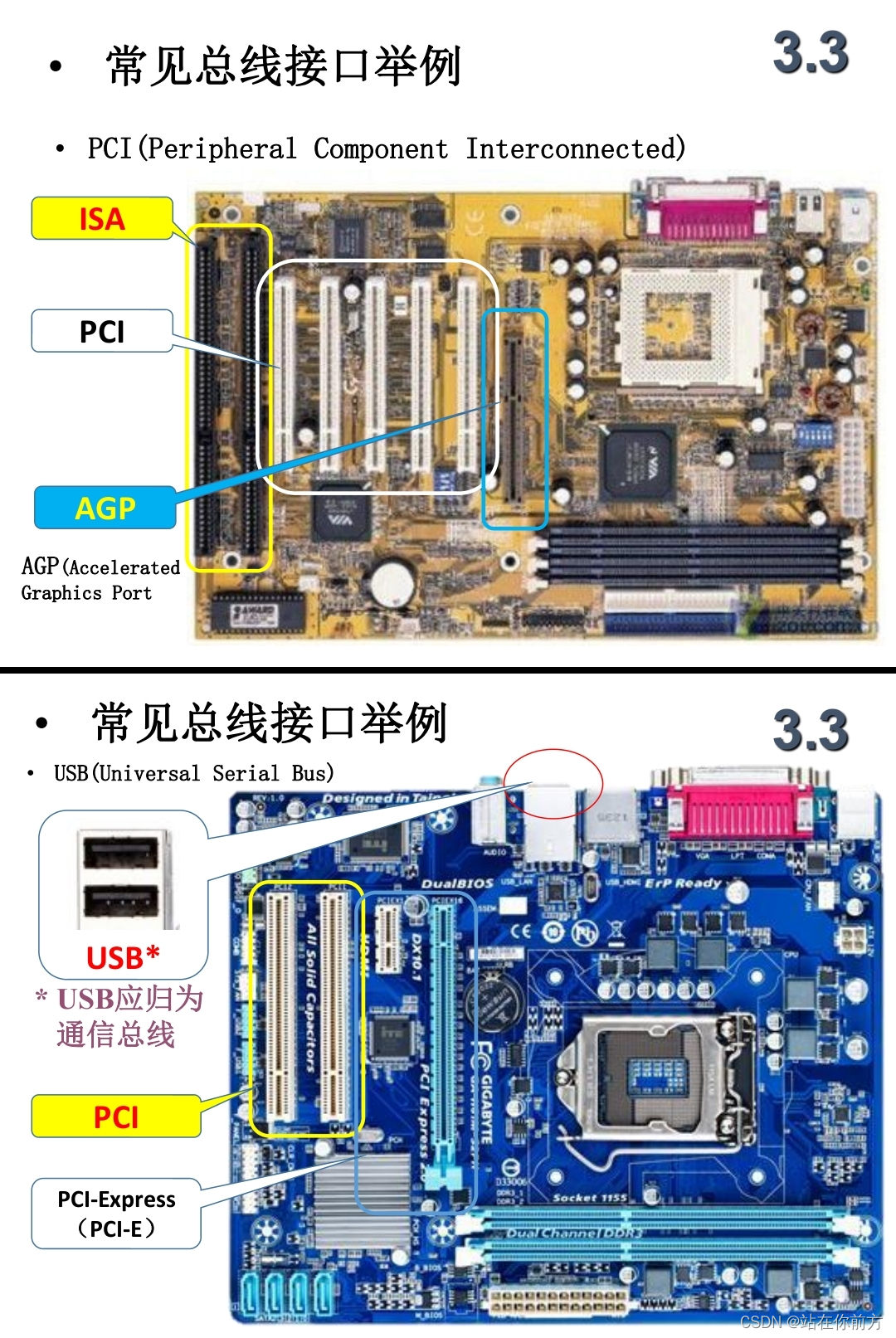

- PCI(Peripheral Component Interconnect)总线

- 总线时钟频率33/66MHz,并与CPU独立 总线宽度32位/64位 数据传输率132MB/s起,所有设备共享 即插即用(自动分配地址空间、中断号等)

- 变种:AGP(Accelerated Graphics Port)

- PCI-X(PCI extended)总线

- 与PCI总线物理兼容

- 总线时钟频率支持66/100/133MHz

- 支持DDR和QDR技术,最高传输率533MB/s

- 多用于服务器和高端PC用户

- PCI-E(PCI Express)总线

- 高速串行总线

- 可包含多个数据通道x1/x2/x4/x8/x16

- 数据传输率250MB/s起

- 软件与传统PCI兼容

- 变种:NVMe(用于高速SSD,提高传输率)

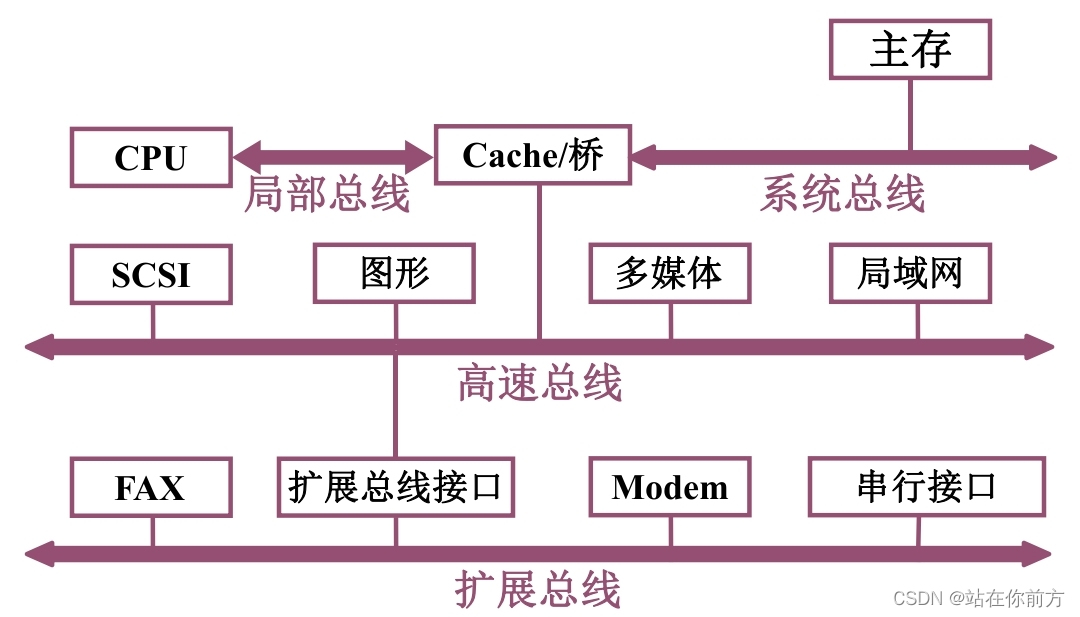

总线结构

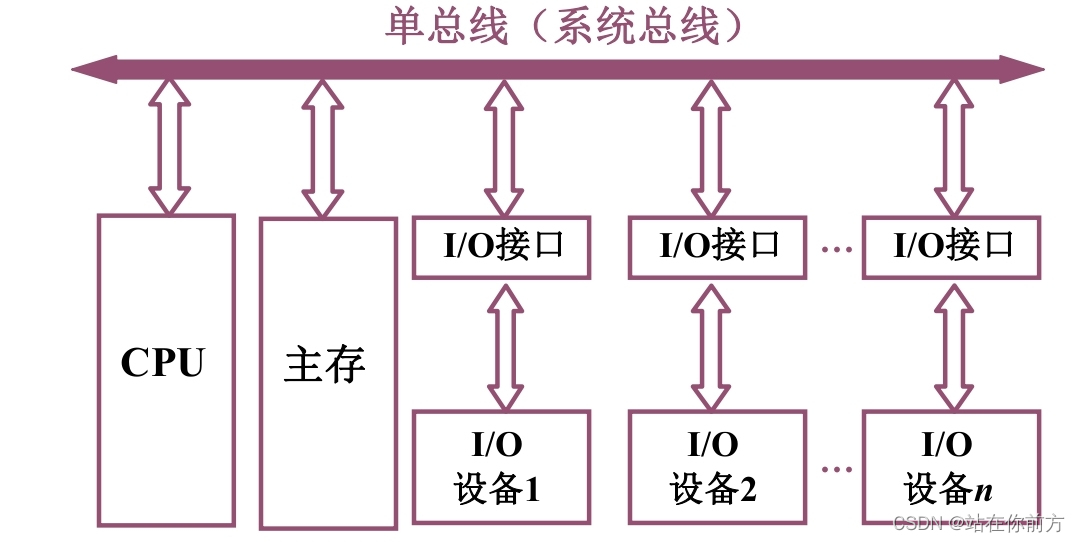

(一)单总线结构

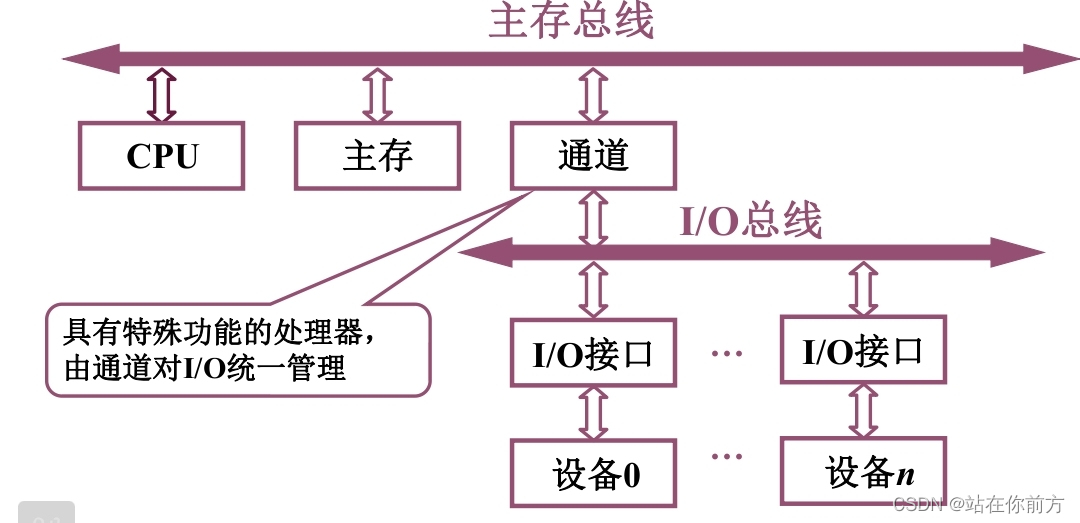

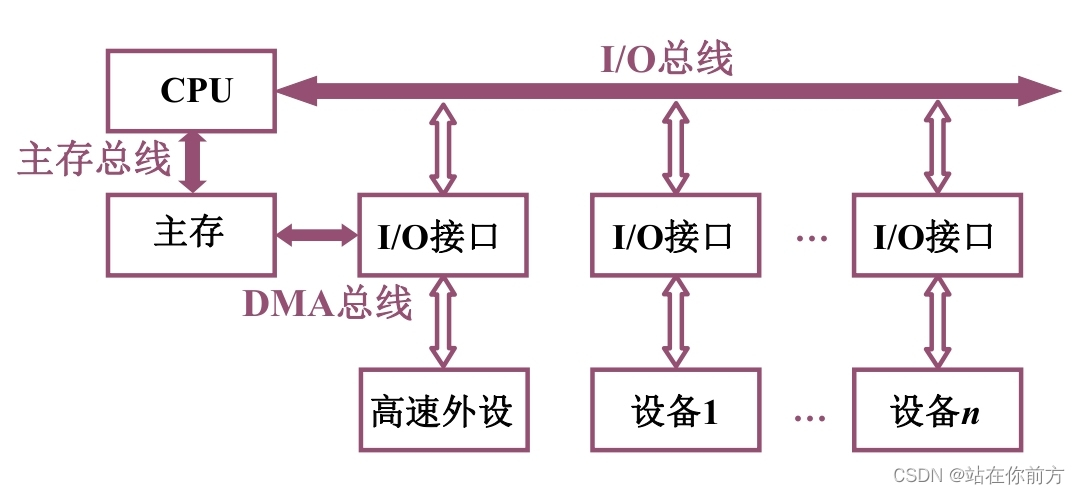

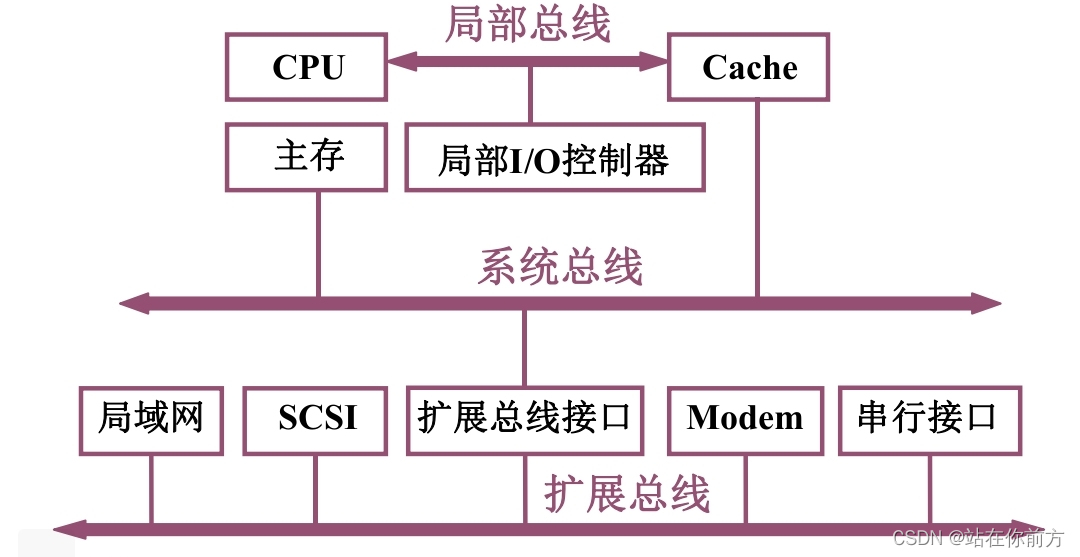

(二)多总线结构

- 双总线结构

- 三总线结构

- 三总线结构的又一形式

- 四总线结构

2134

2134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?