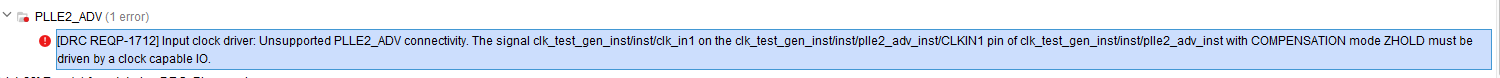

编译报错:

[DRC REQP-1712] Input clock driver: Unsupported PLLE2_ADV connectivity. The signal clk_test_gen_inst/inst/clk_in1 on the clk_test_gen_inst/inst/plle2_adv_inst/CLKIN1 pin of clk_test_gen_inst/inst/plle2_adv_inst with COMPENSATION mode ZHOLD must be driven by a clock capable IO.

报错显示应该是PLL的问题

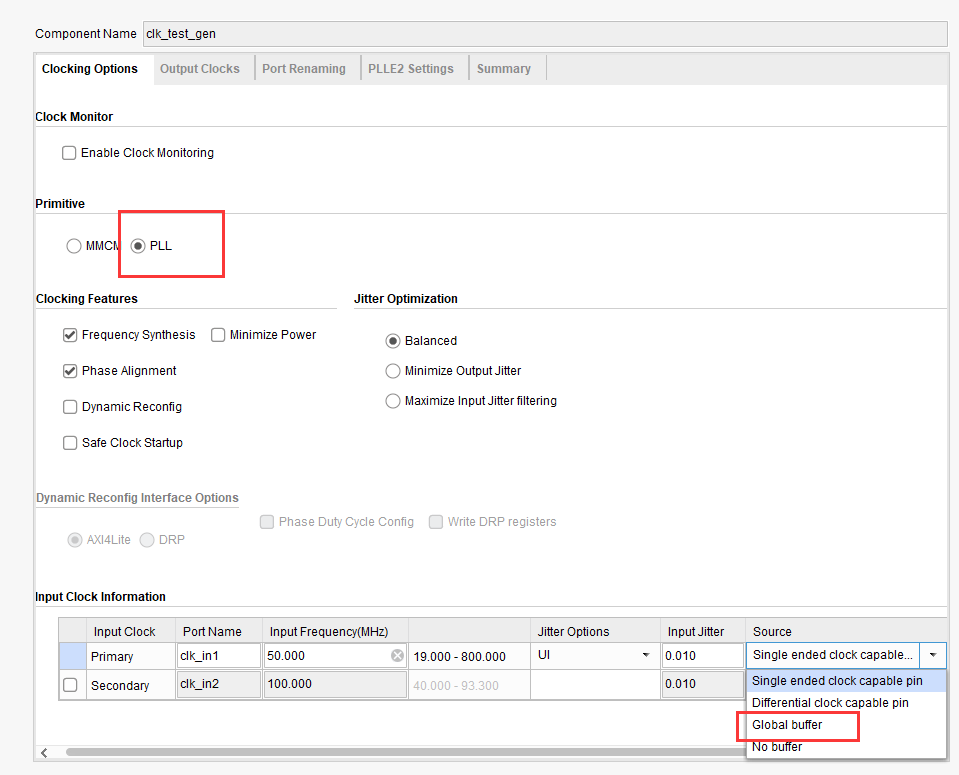

解决办法:

将CLKIN1的source由“single ended clock capable pin”调为“global buffer”就可以了。

报错提醒:

[Project 1-19] Could not find the file 'C:/Users/Admin/Desktop/demo/top_ad_da_fft_lcd/doc/xfir5.coe'.

以及编译报错

- [Vivado 12-172] File or Directory 'C:/Users/Admin/Desktop/demo/top_ad_da_fft_lcd/doc/xfir5.coe' does not exist

- 原因:更换了ip的coe或者删除了coe文件,但是编译列表没有移除ip的coe文件

322

322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?