基于SMIC NP1P 0.75/1.8V design rules

简单注释:EN类型为via没有包住,拉宽一下shape的长度,一般要求0.315um;A类型为area面积不够,一般要求0.0039um2;S类型为spacing间距不够;L类型为length长度不够,多出现在多边形shape上。

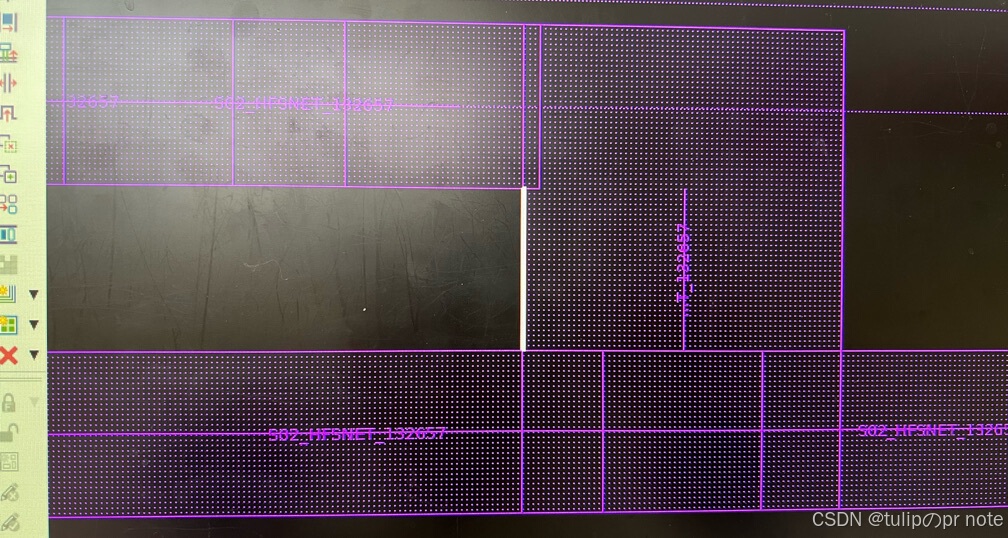

M2BB M3BB s类型的drc与cut metal存在距离问题

大多数情况下,类型+数字即表示某一层出现了某种类型的DRC错误。

AA_L_1

s01 tapfiller插入不完整,tapfiller 可以通过orientation R0和MX来区分,只要将报错距离中间插入相同orientation的tapfiller即可修复

在确定floorplan之后(主要是阵列位置),在s01的block上尽早修复并写出fp_def,即可在后续的综合中避免此类drc

MXYCA3_S_7

box M3 shape和standard cell内部的M3 shape间距不够,一般修改box 的shape

MXYCA4_R_1

mask_constraint没有设置,gui打开属性添加即可

derive_mask_constraint [get_shapes -of_objects [get_nets xxx]]

derive_mask_constraint [get_vias -of_objects [get_nets xxx]]

derive_mask_constraint [get_vias -of_objects [get_nets xxx]] -derive_cut_mask

VX2_ORCS_1_conflict_mask

可能会与VX2_OR_1_2以及VX2_OR_1_2_others一起出现,都是同一个地方出错了,尽量兼顾修复

原因是M2 V2三个孔间距太小,改走线

TV_R_V0V1V3V4_DFM1

多孔叠放,解决方法是删掉其中一个孔,不改变连接关系

MD_R_1

pin摆的太近了,出来的shape没在track上

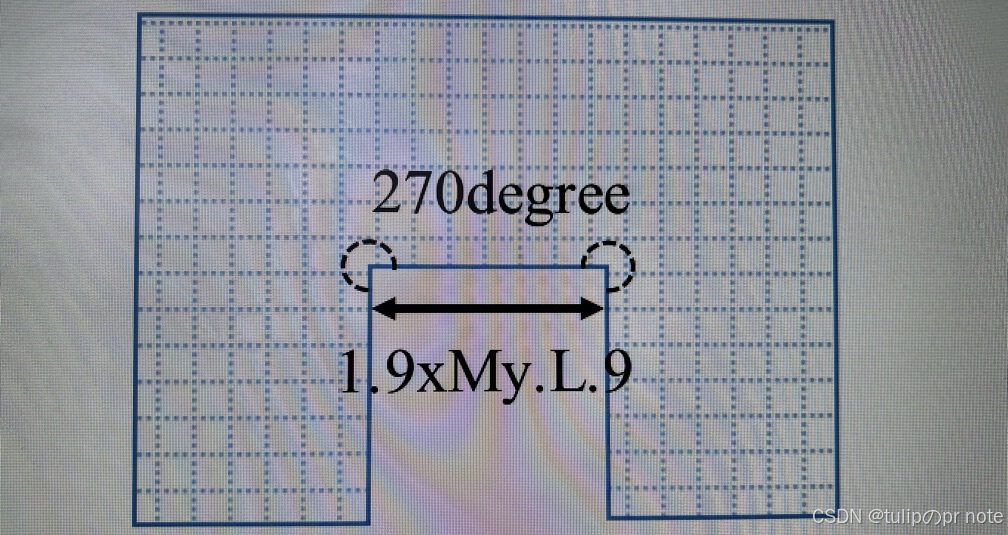

1D9XMY5_L_9

多边形 length不够,现场图如下

尽量避免这种多边形,解决方法也是想办法改线

疑难drc

1.井字型的连线,删掉孔保证连接关系不变是最好的方式

2.port buff cell内部的M2层线不在track上会导致超级复杂的drc问题,通过改变cell的方向和位置将M2摆放到track上,并确保连接关系不变,确保周围filler正确

3.cell内部M2的的长度不够而且没有special router extension,找到设计内其他相同ref name的cell拷贝相同位置的extension(大写C进入拷贝模式)到出现drc的M2上,保证连接关系不变,借助cut metal避免其他drc

2200

2200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?