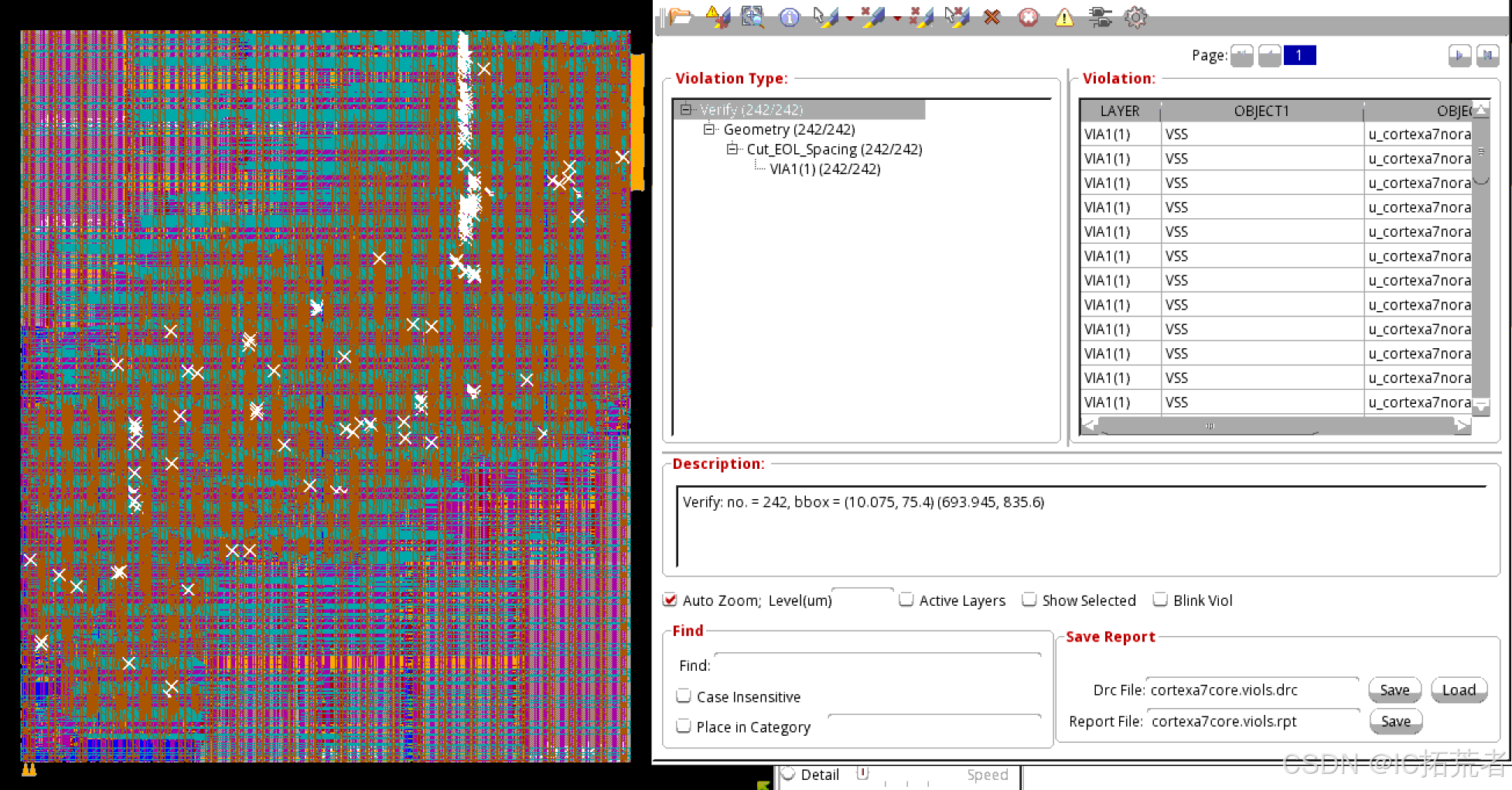

最近不少学员在做数字IC后端a7core项目时发现存在很多VIA1的Cut_EOL_Spacing DRC Violation,而且基本上都是报在VSS net上。具体DRC Violation数量及分布如下图所示。

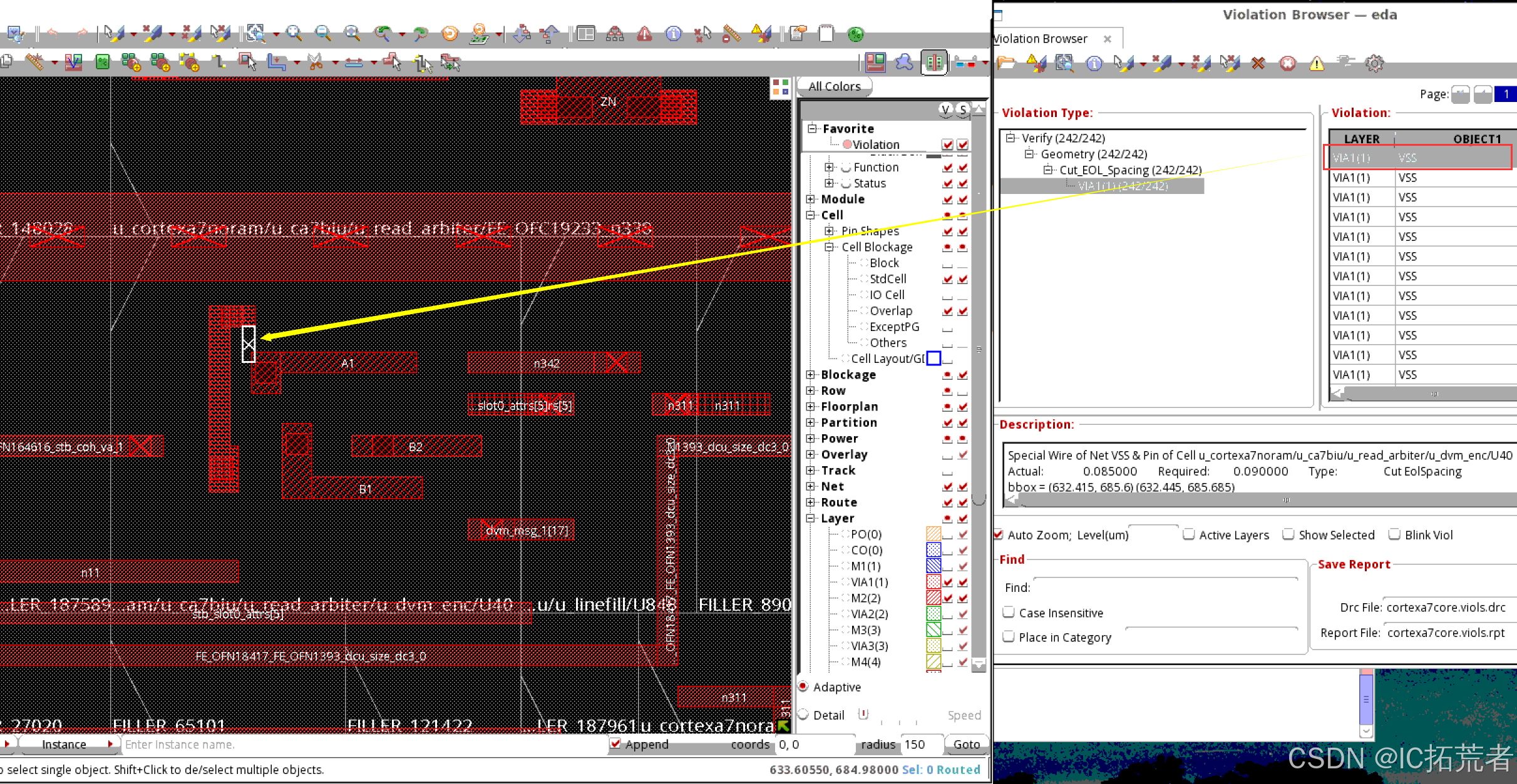

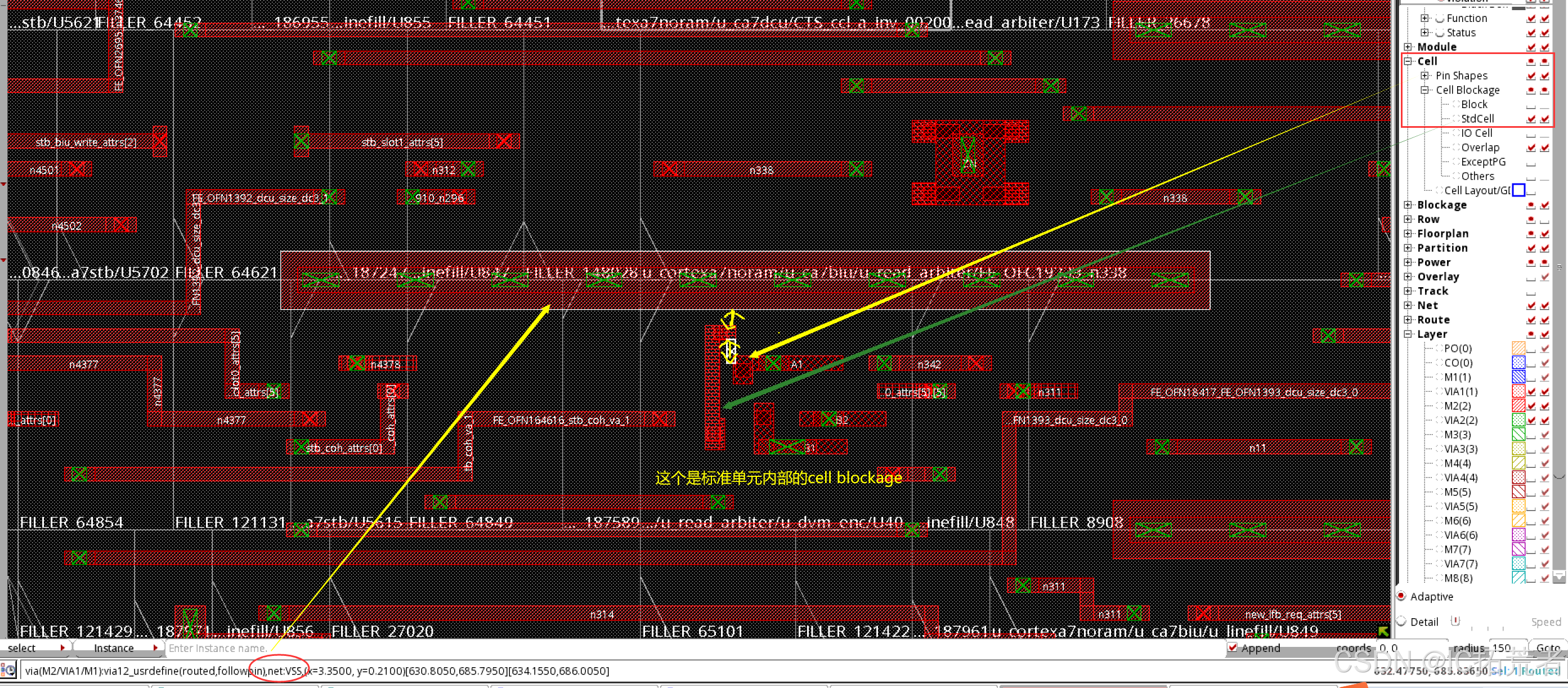

通过Violation Browser,我们可以快速定位到有DRC Violation所在位置。高亮定位位置后,我们很容易发现这里是报两个VIA1间距不够。而且正常大家不打开innovus右侧控制面板中的pin shape和cell blockage选项,都是看不到任何VIA1的。因为这里涉及的两个via1,一个是pin shape的via1,另外一个是标准单元内部走线的VIA1。也就是说这两个VIA1都是标准单元内部的,即我们无法更改这两个VIA1。

大部分学员看到这里非常蒙圈,既然都是标准单元内部的,那岂不是foundary提供的标准单元库存在问题?

我们一直强调DRC Violation的出现需要一定的触发条件。同样的一个VIA1在不同场景或不同的周边环境下,有的时候会有DRC Violation,有的时候则不会有DRC Violation。

如果细心的同学多高亮几个这类DRC Violatio

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

225

225

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?