一、三种计算e的x次方的方法

1.查表法:提前将所有计算结果保存在一个ROM中。此方法计算量小,速度快。但随着函数计算区间的增大,查找的ROM表会十分巨大,十分浪费资源。

2.CORDIC算法:即坐标旋转数字计算法。通过多次迭代将一些复杂的运算转化为简单的运算。但随着精度的提高,其算法迭代次数会大幅增加,计算速度会降低。

3.Talyor级数展开法:将e的x次方转化为多项式,将系数保存在ROM中,这种方法结合了前两种方法,但在精度要求高的情况下,乘法器和ROM将会消耗大量资源。

二、Talyor级数展开法verilog代码(输入数据格式FP16)

module exponent (x,clk,enable,output_exp,ack);

parameter DATA_WIDTH=16;

localparam taylor_iter=7;

input [DATA_WIDTH-1:0] x;

input clk;

input enable;

output reg ack;

output reg [DATA_WIDTH-1:0] output_exp;

reg [DATA_WIDTH*taylor_iter-1:0] divisors; // 1/6 1/5 1/4 1/3 1/2 1 1

reg [DATA_WIDTH-1:0] mult1; //is 1 in the first cycle and then the output of the second multiplication in the rest

reg [DATA_WIDTH-1:0] one_or_x; //one in the first cycle and then x for the rest

wire [DATA_WIDTH-1:0] out_m1; //output of the first multiplication which is either with 1 or x

wire [DATA_WIDTH-1:0] out_m2; //the output of the second muliplication and the input of the first

wire [DATA_WIDTH-1:0] output_add1;

reg [DATA_WIDTH-1:0] out_reg; //the output of the Addition each cycle

floatMult FM1 (mult1,one_or_x,out_m1);

floatMult FM2 (out_m1,divisors[15:0],out_m2);

floatAdd FADD1 (out_m2,out_reg,output_add1);

always @ (posedge clk) begin

if(enable==1'b0) begin

one_or_x=16'b0011_1100_0000_0000; //initially 1

mult1=16'b0011_1100_0000_0000; //initially 1

out_reg=16'b0000000000000000; //initially 0

output_exp=16'b0000000000000000; //output zero until ack is 1

divisors=112'b0011000101010101_0011001001100110_0011010000000000_0011010101010101_0011100000000000_0011110000000000_0011110000000000;

ack=1'b0; // acknowledge is 0 at the beginning

end

else begin

one_or_x=x;

mult1=out_m2; //get the output of the second multiplication to multiply with x

divisors=divisors>>16; //shift 16 bit to divide the out_m1 with the new number to compute the factorial

out_reg=output_add1;

if(divisors==112'b0000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000)

begin

output_exp=output_add1;

ack=1'b1;

end

end

end

endmodule

如代码所示,采用了两个乘法器和一个加法器,divisors用于存储多项式的系数(每16位为一个系数)。

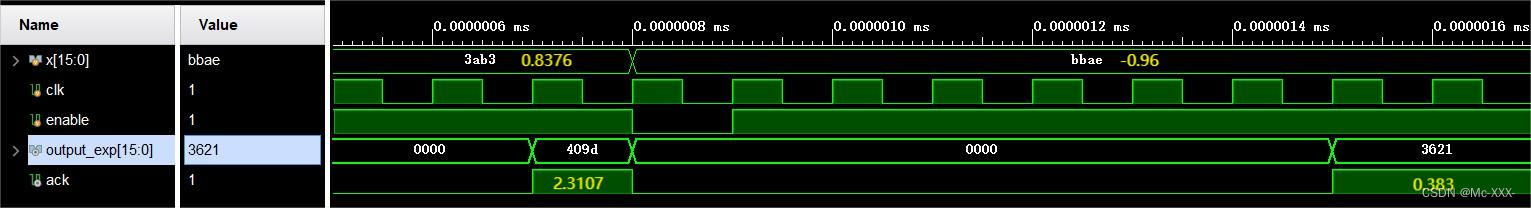

三、波形验证

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?