此内容仅为个人学习笔记,如有不足之处,欢迎指正~

开发环境:Quartus Prime Standard 18.0

开发板型号:野火征途Pro

FPGA型号:EP4CE10F17C8

参考视频链接:正点原子手把手教你学FPGA之Nios II篇-基于开拓者V1_哔哩哔哩_bilibili

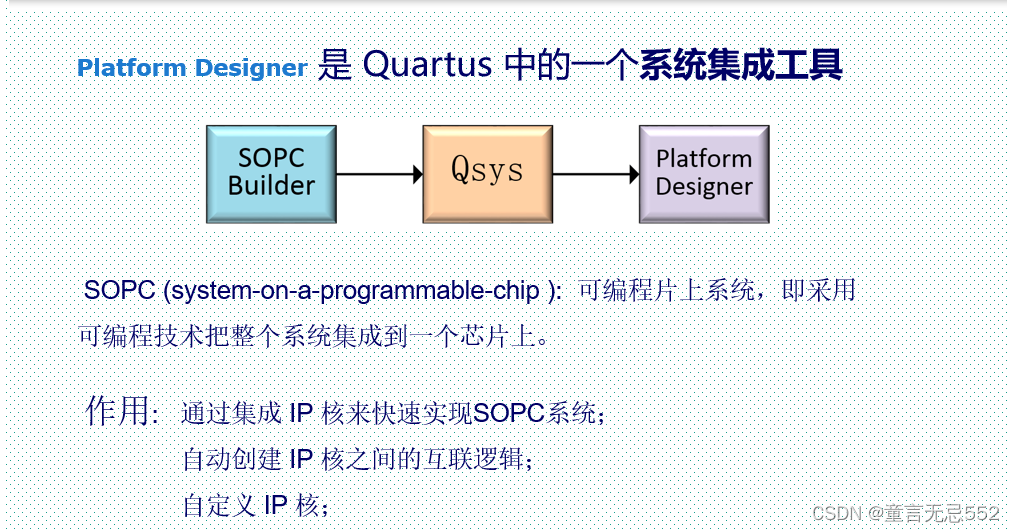

1. Platform Designer简介

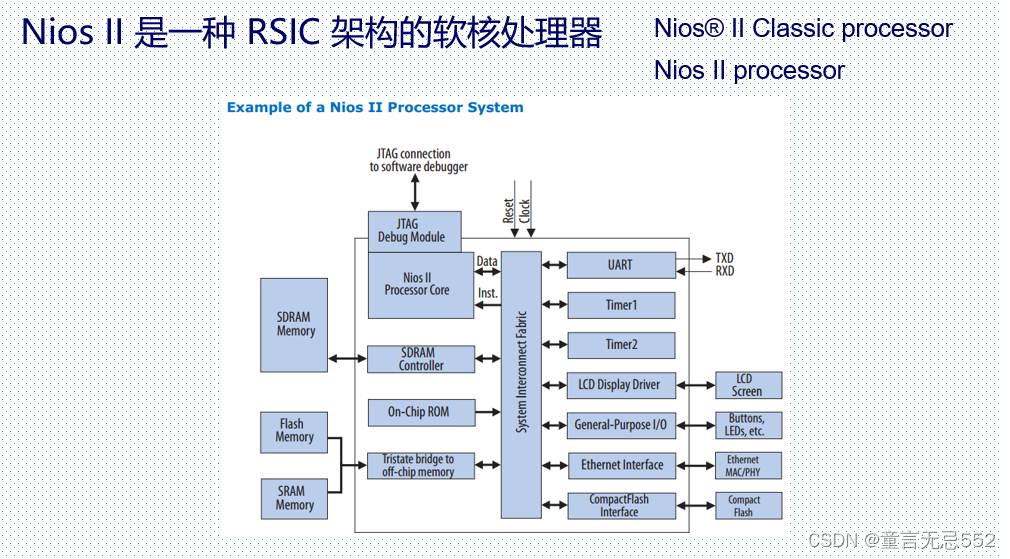

2. Nios II 简介

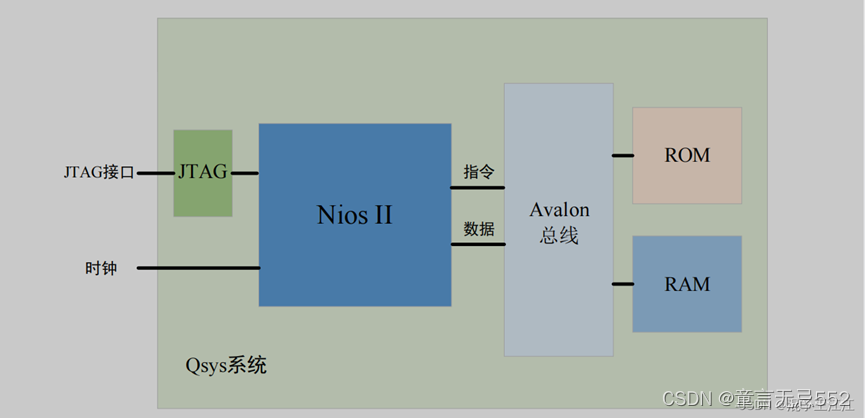

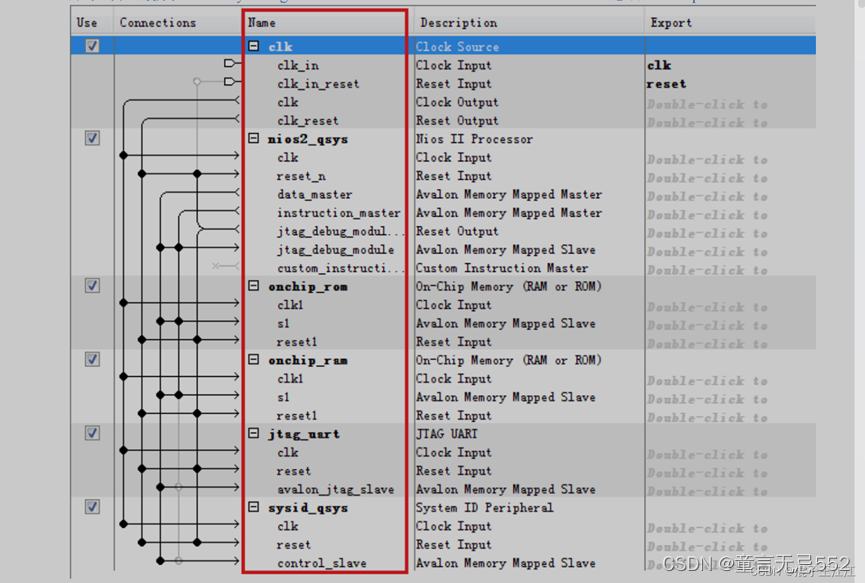

Nios II 处理器通过 Avalon 总线与 ROM 和RAM 连接,其中 Avalon 总线用来传输指令与数据。除此之外,Qsys 系统还提供了一个 JTAG 接口,供用户下载和调试程序。

3. 创建Hello_world工程

流程:新建工程——硬件设计——软件设计

系统涉及到的模块:

1、时钟(Clock Source)

clk IP 核的全称是 Clock Source,在这里设定我们整个系统的工作时钟频率。

2、nios2_qsys(Nios II(Classic) Processer)

这是我们之前对Qsys介绍时了解到,这是整个Qsys的控制中心,起着分配中断、管理地址、调度内存等主要的控制作用,相当于大脑的低位吧,通过Avalon与外界进行通信。

3、片内存储(On-Chip-Memory)

这里我们创建了两个片内存储器,ROM和RAM。这两个片内存储器都是利用FPGA的片上存储资源进行实现,除了用于存储指令和数据外,还是程序的运行空间。需要注意的是ROM的实现,在FPGA内部并没有专用的ROM资源,我们通过对 RAM 赋初值,并始终保持该值,使其变得只读,从而实现片内 ROM(只读存储器)。

4、串行通信(JTAG UART Intel FPGA IP

JTAG UART IP 核使用 JTAG 接口来实现上位机与 Qsys 系统之间的串行通信。JTAG UART IP 核为用户提供了 Avalon-MM 接口映射,屏蔽了复杂的 JTAG 接口协议。

5、System ID(Systerm ID Periheral)

System ID IP核是一个具有Avalon接口的只读设备,它给每个Nios II系统生成一个唯一的标识符(ID),并将其写入 System ID 核的寄存器中。编译器和用户可以利用该 IP 核来验证编译后的可执行程序与配置到FPGA 中的硬件环境是否匹配。如果可执行程序中的 ID 与 FPGA 中 System ID 核所存储的 ID 不一致,那么程序在运行时可能会出错

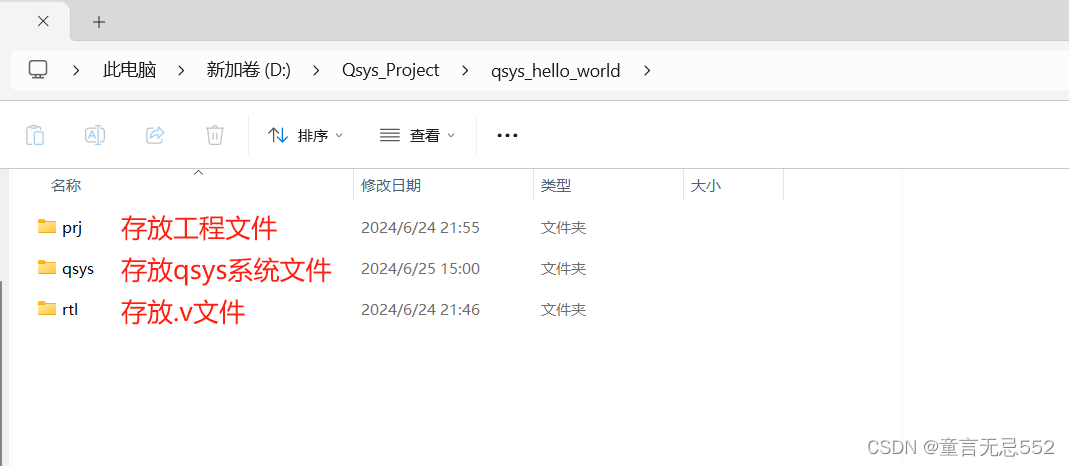

3.1 新建工程

和新建FPGA工程步骤一样,起好工程名字(qsys_hello_world),确认好工程路径(将工程文件放在prj文件夹下),规划好工程文件夹组成。

3.2 搭建SOPC (system-on-a-programmable-chip )系统(硬件部分)

流程:搭建系统——配置系统——生成系统

最简单的Qsys系统,包含五个IP核:

1. Clock Source(默认就有)

2. Nios II(Classic) Processer

3. On-Chip-Memory

4. JTAG UART

5. Systerm ID Periheral

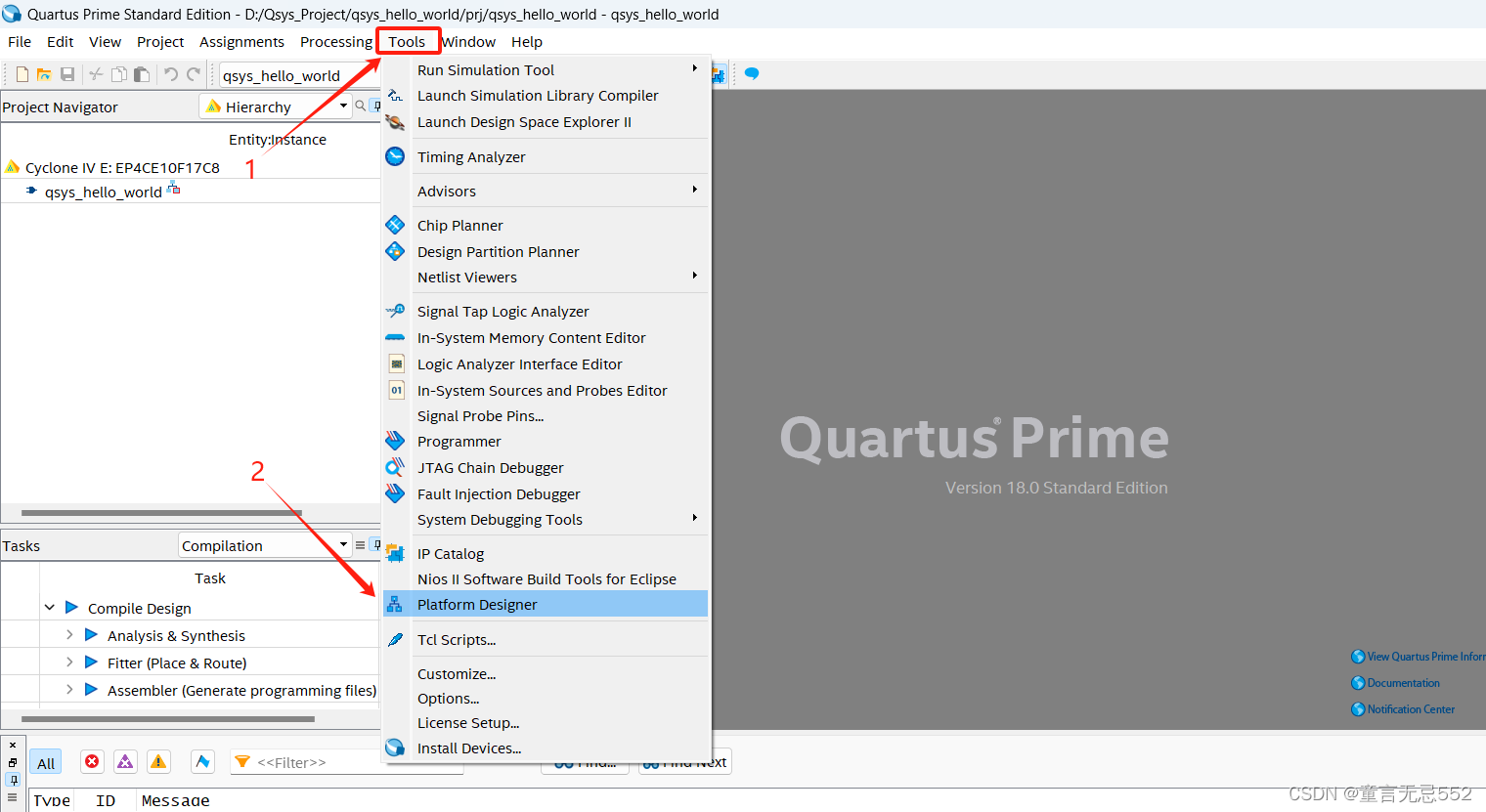

第一步:打开Platform Designer

法一:点击Tools-Platform Designer 法二:直接点击红框处

法二:直接点击红框处

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?