VHDL的模块设计目录

前言

本套代码是基于VHDL在quartus的环境下编写的代码,只作为学习积累,如有bug请多多包含

一、边沿同步检测器是什么?

检测到输入信号的跳变沿时,需要与系统时钟的跳变沿对齐

二、代码分析与仿真效果

1.代码分析

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

entity edge_detect is

port( clk : in std_logic;

rst_n : in std_logic;

inf_d : in std_logic;

inf_rise: out std_logic;

inf_fall: out std_logic );

end edge_detect;

architecture bhv of edge_detect is

signal inf_d1,inf_d2 : std_logic;

begin

process(clk,rst_n,inf_d)

begin

if(rst_n = '0') then

inf_d1 <= '0';

inf_d2 <= '0';

elsif(clk'event and clk='1') then

inf_d1 <= inf_d;

inf_d2 <= inf_d1;

end if;

end process;

inf_rise <= not inf_d2 and inf_d1;

inf_fall <= inf_d2 and not inf_d1;

end bhv;

在这段代码中,我们可以看到首先定义了五个接口,分别为:

clk时钟信号输入端;

rst_n复位信号输入端;

inf_d信号输入端;

inf_rise上升沿同步信号;

inf_fall下降沿同步信号。

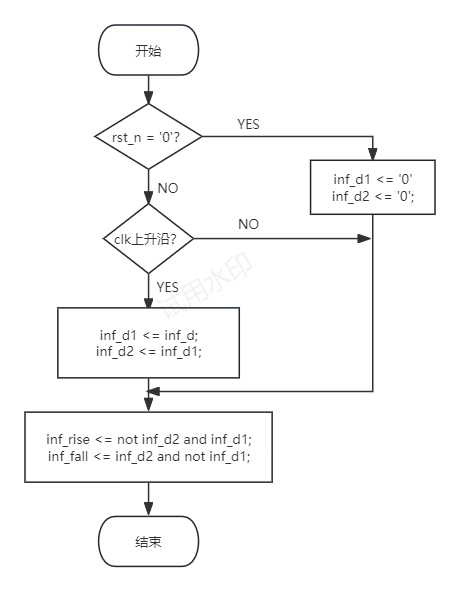

在程序中:

定义一个临时变量inf_d1,inf_d2用来记录电平变化

1.判断复位信号是否使能:

当复位信号被拉低,说明复位信号被使能,inf_d1清零,inf_d2清零,

在复位信号被拉高,说明复位信号没有使能,inf_d1不被清零,inf_d2不被清零,

2.对信号处理

并将这一时刻inf_d状态给到inf_d1状态,同时将前一时刻的inf_d1状态给到inf_d2;

最后先将inf_d2做逻辑非运算,再与inf_d1做逻辑与运算,得到上升沿同步信号nf_rise;

再将inf_d1做逻辑非运算,再与inf_d2做逻辑与运算,得到下降沿同步信号inf_fall。

流程图

————————————————

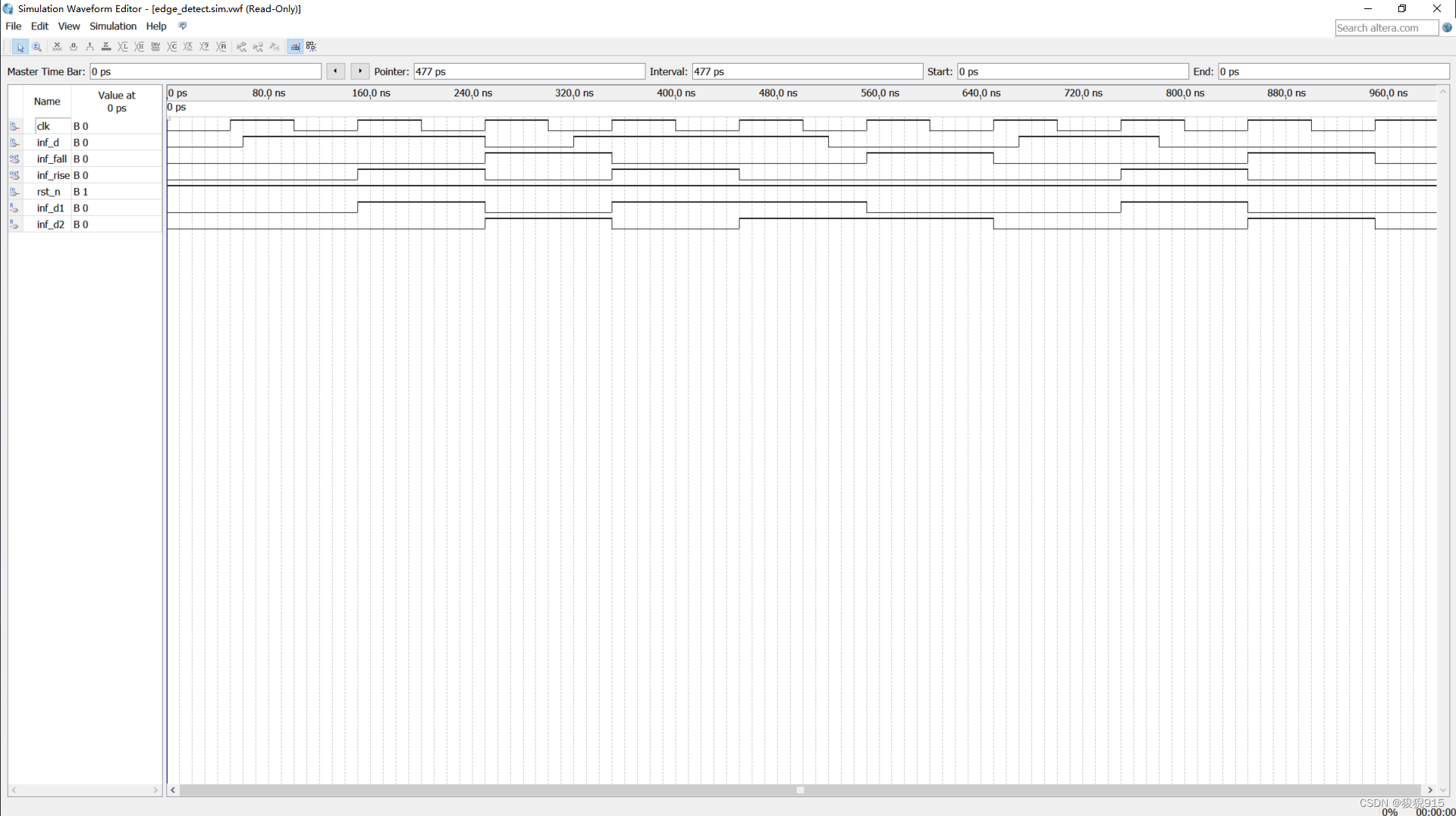

2.仿真效果

仿真参数

仿真波形

得到inf_rise和inf_fall为信号的上升沿和下降沿,并且和系统时钟同步。

inf_rise:信号的上升沿被同步到与时钟上升沿一致,

inf_fall:信号的下降沿被同步到与时钟上升沿一致。

总结

本文主要讲解了边沿同步检测器的代码实现。

60

60

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?