一、引言

本文为个人理解,用于记录学习经验,有任何错误可以指出讨论。

二、AD9528

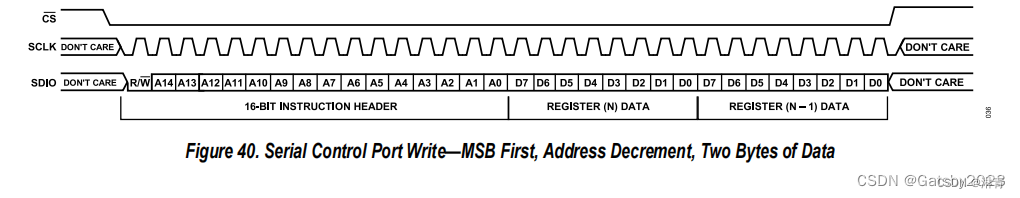

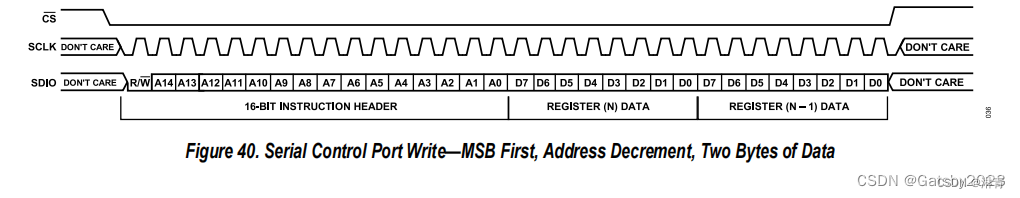

时序图

该字节长度最小为24bit

0-7bit : D0~D7为寄存数据;

8-23bit : A0~A14为地址位,R/W是读写控制位

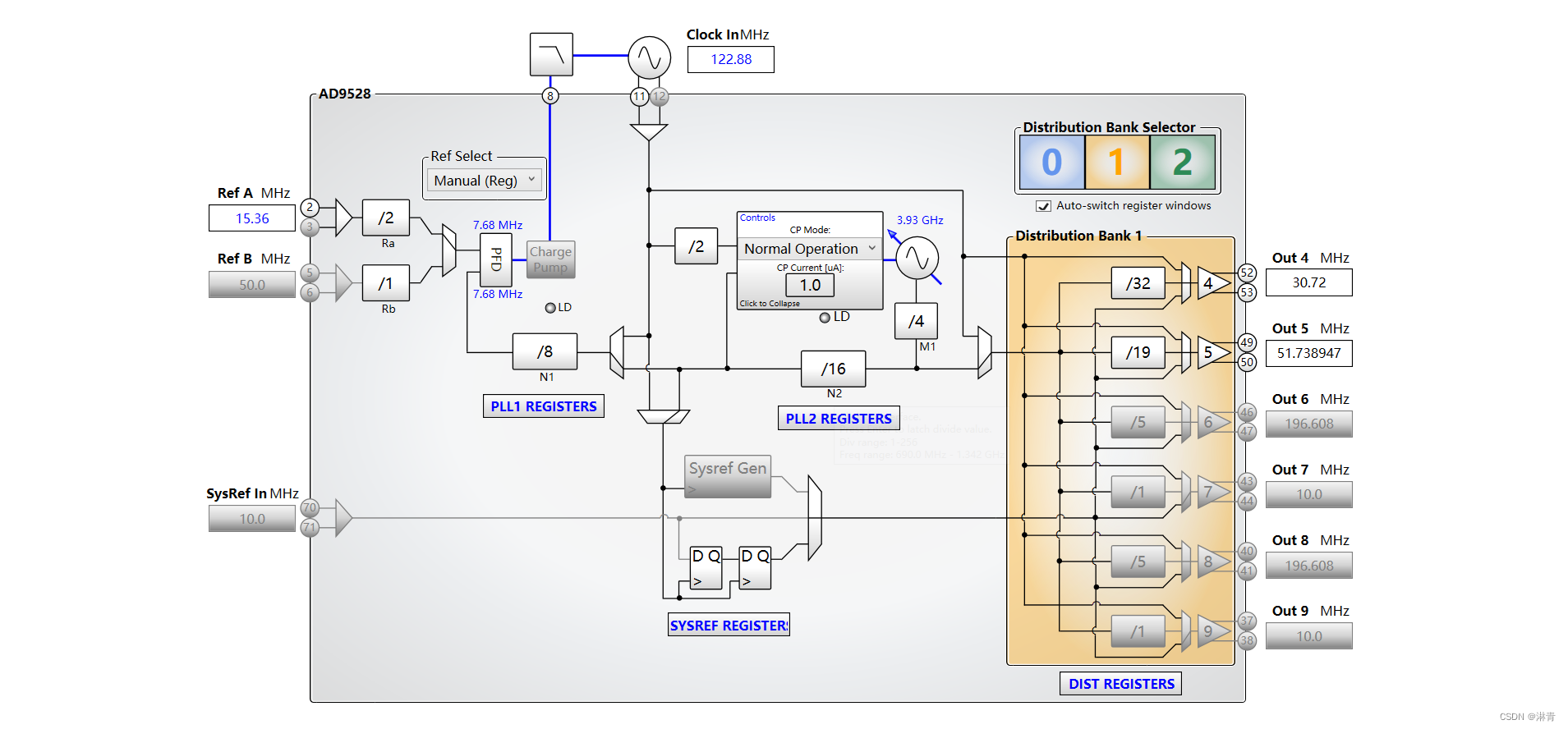

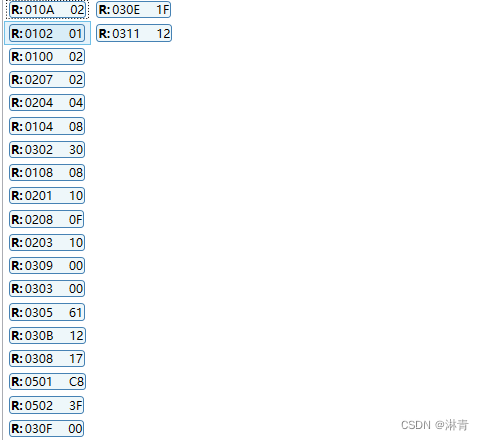

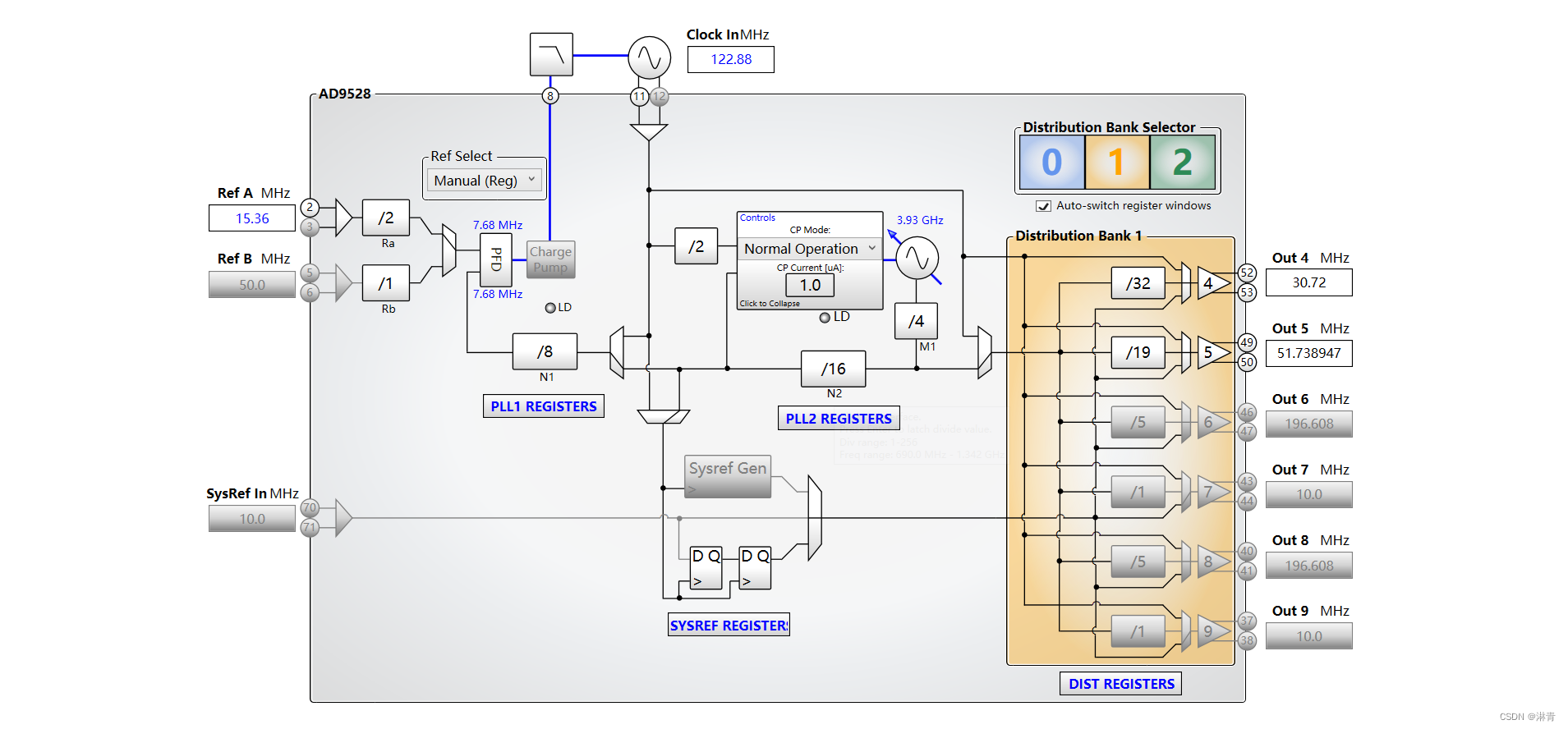

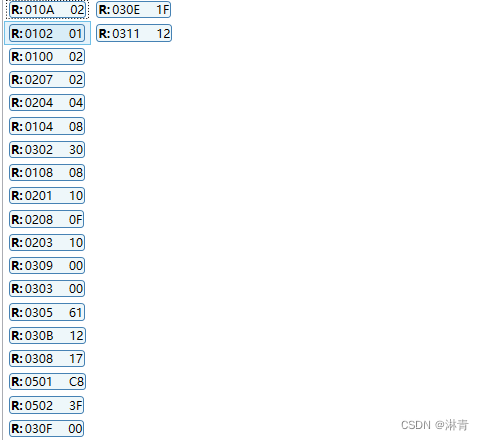

寄存器配置可以通过ADI公司的上位机软件生成

修改添加Clock In(VCXO)、RefA/RefB、SysRef参考时钟,以及修改PLL1和PLL2的分频系数,得到需要的输出时钟频率。

本文介绍了AD9528芯片的时序图,涉及数据寄存、地址配置、读写控制,重点讲解了如何通过上位机软件修改时钟输入、参考时钟和PLL分频系数以实现不同输出时钟频率。作者分享个人学习体验,欢迎提出纠正意见。

本文介绍了AD9528芯片的时序图,涉及数据寄存、地址配置、读写控制,重点讲解了如何通过上位机软件修改时钟输入、参考时钟和PLL分频系数以实现不同输出时钟频率。作者分享个人学习体验,欢迎提出纠正意见。

一、引言

本文为个人理解,用于记录学习经验,有任何错误可以指出讨论。

二、AD9528

时序图

该字节长度最小为24bit

0-7bit : D0~D7为寄存数据;

8-23bit : A0~A14为地址位,R/W是读写控制位

寄存器配置可以通过ADI公司的上位机软件生成

修改添加Clock In(VCXO)、RefA/RefB、SysRef参考时钟,以及修改PLL1和PLL2的分频系数,得到需要的输出时钟频率。

1797

1797

318

318

737

737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?