一.AXI总线类型接口

AXI是一种总线协议,可以挂在多个master和slave:

(1)AXI4:主要面向高性能地址映射通信的需求;(突发数据)(地址映射模式)

(2)AXI4-Lite:是一个轻量级的,适用于吞吐量较小的地址映射通信总线;(无突发)(地址映射模式)

(3)AXI4-stream:面向高速流数据传输(流模式)AXI4、AXI4-LITE总线信号组成:写地址通道、写数据通道、写响应通道、读地址通道、读数据通道。

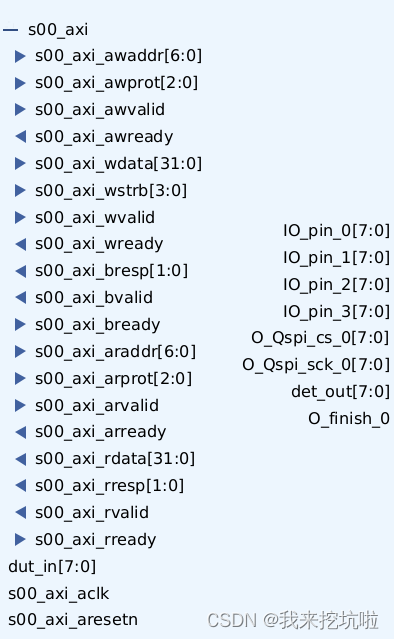

二.下面基于AXI4 IP核的信号介绍

(1)全局信号

(2) 写地址通道

(3) 写数据通道

(4)写响应通道

(5)读地址通道

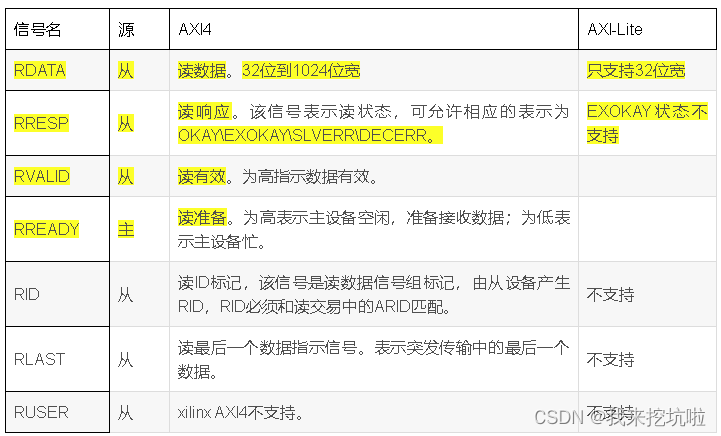

(6)读数据通道

8146

8146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?