在模拟IC设计和仿真中,有时会需要一个电路模型(如运放、D触发器),配合主要电路来进行行为或电路仿真,这个电路模型不是用具体工艺的mos管等搭建,而是用VerilogA代码生成,或者用Cadence中analogLib搭建,本文用全差分放大器和D触发器举例说明搭建过程,并比较二者的不同。

1 运行环境

操作系统运行环境: Linux (RHEL6.x, RHEL7.x)

EDA环境:Cadence IC617, Spectre15.1

2 全差分放大器的比较

2.1 用VerilogA生成

在Cadence/Virtuoso内,用VerilogA代码就可以生成全差分放大器,做成symbol,就可以被其他电路测试使用(Cadence操作过程站内参考文章很多,这里不详述)。

这里参考一下Cadence Virtuoso内ahdlLib库里diffamp的VerilogA代码:

`include "discipline.h"

`include "constants.h"

// differential amplifier (aka opamp)

// sigin_p,sigin_n: (val,flow)

// sigout: (val,flow)

// INSTANCE parameters

// gain = amplifier differential gain (val)

// sigin_offset = input offset (val)

// MODEL parameters

// {none}

// 'sig_out' is 'gain' times the adjusted input differential signal.

// The adjusted input differential signal is the differential input

// minus 'sigin_offset'

module diffamp(sigin_p, sigin_n, sigout);

input sigin_p, sigin_n;

output sigout;

electrical sigin_p, sigin_n, sigout;

parameter real gain = 1;

parameter real sigin_offset = 0;

analog

V(sigout) <+ (V(sigin_p, sigin_n) - sigin_offset) * gain;

endmodule

从代码这里可以看出放大器的省缺自身增益设成了1,offset设成了0,这些参数可以在调用时按照你的需求来重新设定。

2.2 用Cadence/Virtuoso analogLib内器件来生成

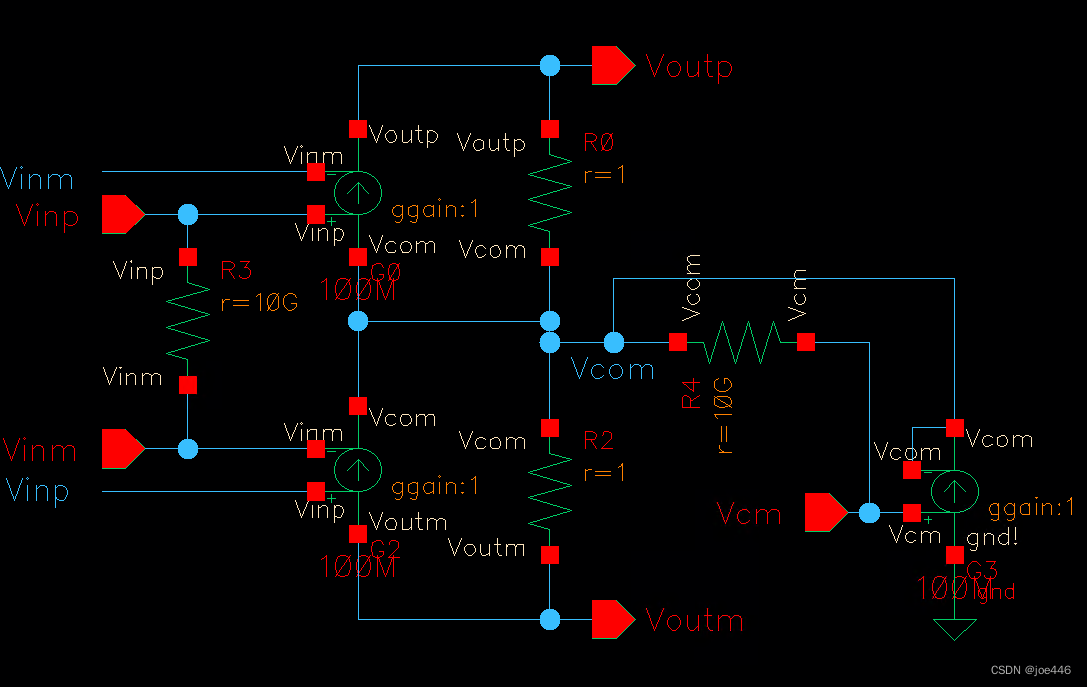

用analogLib里vccs、理想电阻等,可以生成一个全差分放大器电路,如下:

(*来自Baker的CMOS Circuit Design, Layout, and Simulation, 3rd Ed之配套代码)

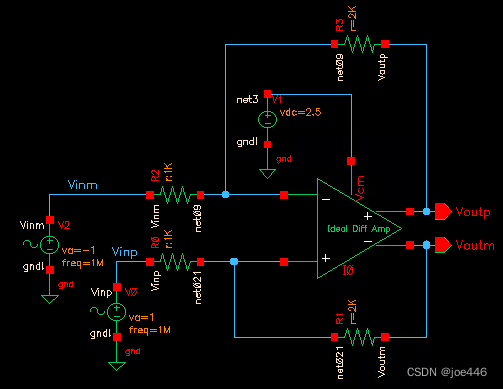

做成symbol,就可以被其他电路仿真测试使用,下面是仿真参考电路:

VerilogA与AnalogLib两种方法比较:

可以看到VerilogA方法可以控制的参数更多,模型可以功能更全;AnalogLib的方法可以更快捷。

3 D触发器的比较

3.1用VerilogA生成

一种VerilogA的D触发器参考代码如下:

//DFF 来源:网络

`include "disciplines.h"

module dff(d,q,clk);

input d,clk;

output q;

electrical d,q,clk;

parameter real td=0.5n from[0:inf];

parameter real tr=0.5n from[0:inf];

parameter integer dir=1 from[-1:1] exclude 0;

parameter real vdd=3.3 from[0:inf];

real state;

analog begin

@(cross(V(clk)-vdd/2,dir)) begin

if (V(d)>vdd/2)

state=vdd;

else

state=0;

end

V(q)<+ transition(state,td,tr);

end

endmodule

3.2用Cadence/Virtuoso analogLib内器件来生成

(*来自Baker的CMOS Circuit Design, Layout, and Simulation, 3rd Ed之配套代码)

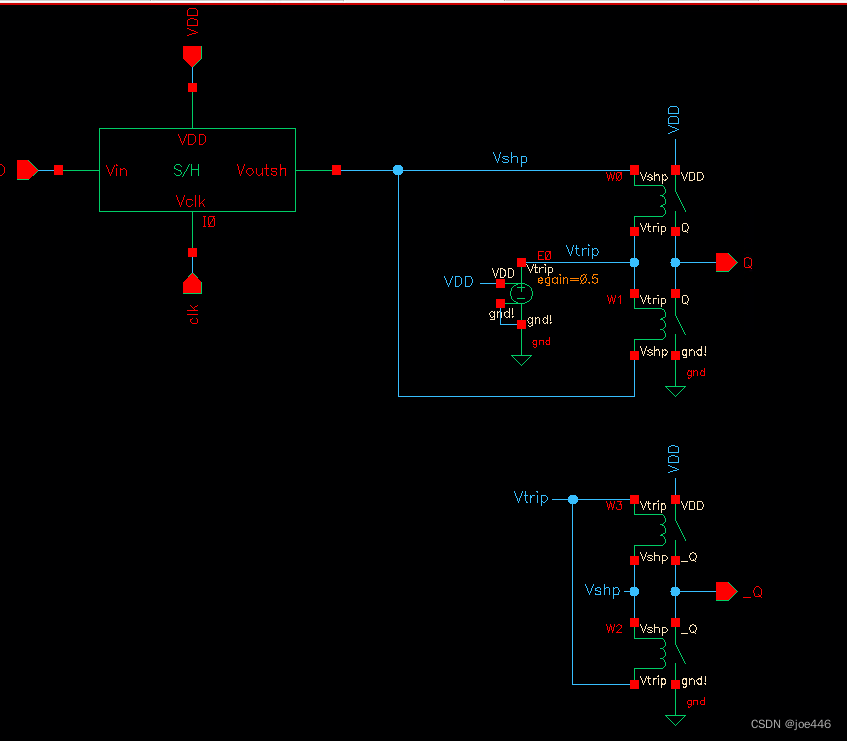

用analogLib库里的relay、vcvs、S/H子电路,生成了一个D触发器:

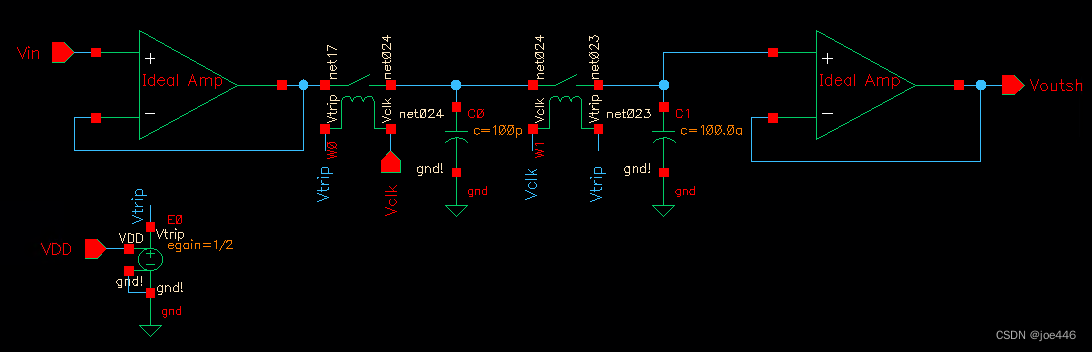

其中子电路S/H(Sample_and_Hold)如下,其内包含的子电路IdealAmp不再展示:

VerilogA与AnalogLib两种方法比较:

可以看到VerilogA方法编程方法简洁高效;AnalogLib的方法比较繁琐。

总之,有些情况下,特别是功能比较简单情况下,用AnalogLib会比较快捷;电路逻辑比较复杂情况下,VerilogA方法会更好。

本文详细介绍了如何在CadenceIC设计环境中,通过VerilogA和Cadence的analogLib库分别构建全差分放大器和D触发器的电路模型,对比了VerilogA的灵活性与AnalogLib的便捷性。

本文详细介绍了如何在CadenceIC设计环境中,通过VerilogA和Cadence的analogLib库分别构建全差分放大器和D触发器的电路模型,对比了VerilogA的灵活性与AnalogLib的便捷性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?