verilog学习——模拟simulation

(一)verilog模拟基础知识

模拟是一种技术,可以在不同的时间对设计施加不同的输入,以检查RTL代码的行为是否符合预期。模拟是一种验证设计鲁棒性的常用技术。

1.模拟波形

模拟可以将设计和测试台信号转储到一个波形中,以分析和调试RTL设计的功能。

变量或net值的每次更改都称为更新事件(update event)。每当更新事件发生时,都会评估这些进程,称为评估事件(evaluation event)。在事件队列(event queue)中跟踪更改的顺序。

在队列中添加新事件称为scheduling。

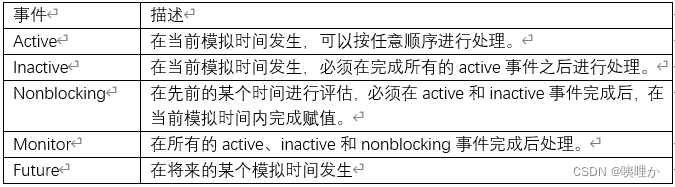

2.事件队列中的区域/regions in event queue

Verilog的事件队列在逻辑上分为五个区域,可以将事件添加到其中任何一个区域。但是只能在活动区域中删除。

一个模拟周期是处理所有active事件的过程。

(二)Verilog testbench/Verilog测试平台

1.verilog测试平台

Verilog测试平台是一个模拟环境,用于验证verilog硬件描述语言(HDL)中描述的数字设计的功能和正确性。

测试平台的目的是提供一种方法,以便在实际制造物理硬件之前模拟设计在各种条件、输入和场景下的行为,能够发现错误、验证功能并优化设计。

2.verilog测试台组件

DUT 或被测设计是要测试的 Verilog 模块或设计。测试平台本身是作为单独的顶级Verilog模块实现的。该模块负责为DUT生成输入信号,捕获其输出,并将其与预期输出进行比较。测试平台可以使用函数(function)和任务(task)进行编码。测试平台信号连接到DUT实例化的端口,并由不同的task进行监控以检查设计功能。

3.编写测试平台代码

(1)声明顶级测试模块

module tb_latch;

// All testbench code goes inside this module

endmodule

(2)声明DUT连接的信号

输入被声明为reg类型,以便可以从过程块驱动。输出被声明为wire类型,以便在测试台模块中可见,且可以对其进行监控以检查设计行为。

reg d; // To drive input "d" of the DUT

reg en; // To drive input "en" of the DUT

reg rstn; // To drive input "rstn" of the DUT

reg prev_q; // To ensure q has not changed when en=0

wire q; // To tap output "q" from DUT

(3)实例化DUT

dut u0 ( .d (d),

.clk (clk),

.rstn (rstn),

.q (q)

);

(4)初始化测试平台变量

所有reg变量的未初始值均为X,可以初始化为initial块内的某个值。

initial begin

d <= 0;

en <= 0;

rstn <= 0;

end

它也可以写在一个函数中,该函数可以在initial块内调用。函数不能用#来模拟延迟。

function void init();

d <= 0;

en <= 0;

rstn <= 0;

endfunction

initial begin

init();

#10; // Wait for 10 time units

end

(5)写测试stimulus

(6)编写检查器代码

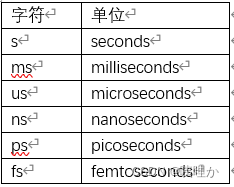

(三)Verilog timescale

‘timescale编译器指令指定其后面的模块的时间单位和精度。

1.语法

`timescale <time_unit>/<time_precision>

// Example

`timescale 1ns/1ps

`timescale 10us/100ns

`timescale 10ns/1ns

Time_unit(时间单位)是延迟和模拟时间的测量,而time_precision(精确度)指定了在模拟中使用延迟值之前如何舍入。

使用以下的timescale 构造在同一设计中使用不同的时间单位。

Ⅰ.‘timescale用于基本测量单位和时间精度。

Ⅱ.$printtimescale系统任务来显示时间单位和精度。

Ⅲ.$time 系统 $realtime 函数返回当前时间,默认报告格式可以通过另一个系统任务 $timeformat 进行更改。

设计中的延迟规范是不可合成的,且无法转换为硬件逻辑。

(四)Verilog scheduling regions

Verilog模型中信号值的每一次变化都被视为一次更新事件(update event)。对这些更新事件敏感的进程(如 always 和 assign 块)将按任意顺序进行评估,称为评估事件(evaluation event)。由于这些事件可能在不同的时间发生,因此通过将它们调度到按模拟时间排列的事件队列(event queue)中,可以更好地管理它们并确保其正确的执行顺序。

1.事件队列(event queue)

一个模拟步骤可以分为四个不同的区域。可以将事件添加到任何区域,但始终从活动区域中删除。

活动事件发生在当前模拟时间,可以按任何顺序进行处理。

非活动事件发生在当前模拟时间,但在处理完所有活动事件后进行处理。

在处理完所有活动和非活动事件后,将分配之前评估的非阻塞分配事件。

在完成所有活动、非活动和非阻塞分配后,将处理监视事件。

2.模拟具有非确定性行为的原因之一是因为可以从队列中删除活动事件并按任何顺序进行处理。

(五)Verilog clock generator/veilog时钟发生器

时钟是构建数字电路的基础,允许不同的模块相互同步。

1.时钟的属性

数字时钟的关键特性是其频率,它决定了时钟周期、工作周期(占空比)以及相对于其他时钟的时钟相位。

(1)时钟周期

频率表示在一定时间段内有多少个周期。时钟周期是完成一个周期所需的时间。

(2)时钟占空比

时钟的高时间量定义了占空比。

(3)时钟相位

如果一个时钟的一个周期可以看作是一个具有 360 度的完整圆,那么另一个时钟可以相对放置在圆中占据不同相位的不同位置。

2.时钟发生器

模拟需要在给定的时间尺度(timescale)上运行,该时间尺度具有时间刻度指令指定的有限精度。时间刻度的精度必须足够好以表示时钟周期.

本文详细介绍了Verilog中的模拟基础,包括模拟波形、事件队列结构、测试平台的构成及其在验证设计中的作用,以及timescale指令对于设定时间和精度的重要性。此外,还讨论了时钟发生器在数字电路设计中的关键角色。

本文详细介绍了Verilog中的模拟基础,包括模拟波形、事件队列结构、测试平台的构成及其在验证设计中的作用,以及timescale指令对于设定时间和精度的重要性。此外,还讨论了时钟发生器在数字电路设计中的关键角色。

1262

1262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?