目录

看这一篇之前可以看一下这篇博客:

http://t.csdnimg.cn/Gc4Cb

1.CPU的功能

CPU由运算器和控制器组成:

运算器用于对数据进行加工;控制器用于协调并控制计算机各部件执行程序的指令序列,基本功能包括取指令、分析指令、执行指令

取指令:自动形成指令地址;自动发出取指令的命令。取完指令后PC(程序计数器会自动+1)

分析指令:操作码译码(分析本条指令要完成什么操作);产生操作数的有效地址,我们执行的指令可能采用直接寻址,间接寻址或寄存器寻址等,那么控制器在分析指令的过程中,就需要根据指令的寻址方式不同,得到操作数的有效地址。

执行指令:根据分析指令得到的“操作命令”和“操作数地址”,形成操作信号控制序列,控制运算器、存储器以及I/O设备完成相应的操作。

中断处理:在现代操作系统中,每执行一条指令,都会检查是否有中断信号需要处理,在这个阶段,控制器会处理管理总线及输入输出;处理异常情况(如掉电或除数为0等)和特殊请求(如打印机请求打印一行字符)。

CPU的主要功能如下:

1.指令控制。完成取指令、分析指令和执行指令的操作,即程序的顺序控制。

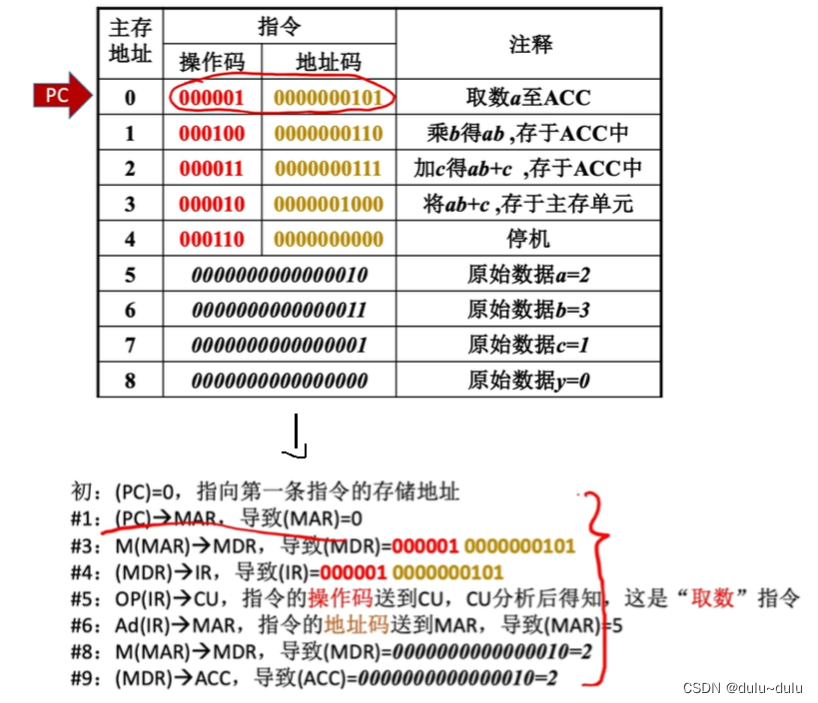

2.操作控制。一条指令的功能往往是由若干操作信号的组合来实现的。CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作。例如下图,主存地址为0的位置的指令可以拆分为9条微操作(微指令)

3.时间控制。对各种操作加以时间上的控制。时间控制要为每条指令按时间顺序提供应有的控制信号。

4.数据加工。对数据进行算术和逻辑运算。

5.中断处理。对计算机运行过程中出现的异常情况和特殊请求进行处理。

2.运算器的基本结构

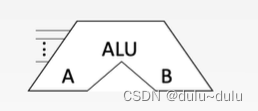

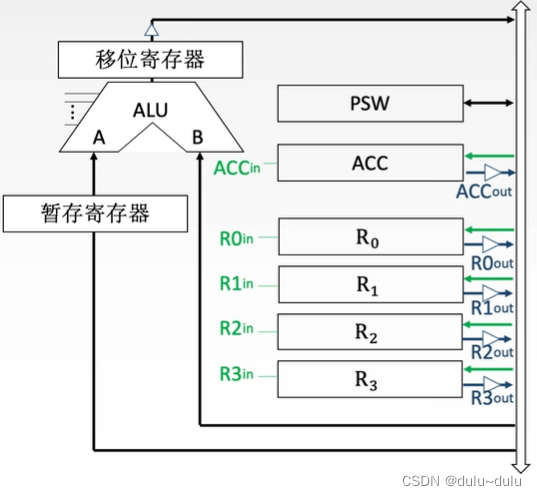

运算器的核心就是ALU(算数逻辑单元),ALU是一个组合逻辑电路,可以实现算术运算和逻辑运算。如下图所示,需要两个操作数A,B,经过ALU电路处理后,可以得到一个输出结果。

参与运算的数据需要提前放到某些通用寄存器中,所以运算器的内部还需要提供通用寄存器组:

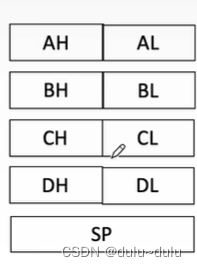

通用寄存器组:如X86架构的CPU中的AX、BX、CX、DX、SP等,用于存放操作数(包括源操作数、目的操作数及中间结果)和各种地址信息等。SP是堆栈指针,用于指示栈顶的地址。程序运行过程中,程序的执行流可能发生改变,为了让程序间的相互调用顺利完成,操作系统会给每一个当前运行的程序管理一个堆栈,这个堆栈中保存的是相应程序中的数据。

如下图所示AX可以分为AH(high),AL(low),即AX的高位和低位,其他类似。

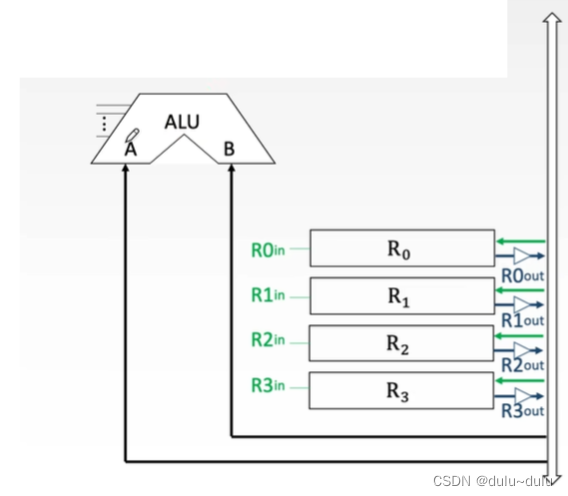

任何通用寄存器都可能作为ALU的输入,若寄存器能够存放16bit数据,那么这16bit数据就会通过16根线并行传送到ALU中。

由于每个寄存器都有到ALU的专门通路,这种连线方式称为专用数据通路方式,即根据指令执行过程中的数据和地址的流动方向安排连接线路。

采用这种方式,性能较高,基本不存在数据冲突现象,但结构复杂,硬件量大,不易实现。

如果直接用导线连接,相当于多个寄存器同时并且一直向ALU传输数据,而我们需要的是,以某一寄存器作为A的输入,以另一个寄存器作为B的输入,如何实现呢?

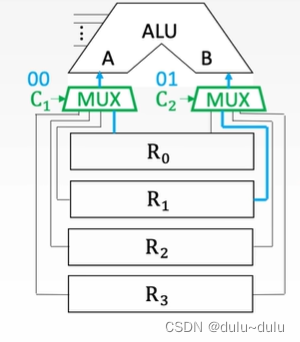

1.使用多路选择器(MUX)

根据控制信号选择一路输出,每个多路选择器都有相应的控制信号,用来选择把哪一个输入信号进行输出,如图所示,以0(00)号寄存器的数据作为A的输入,以1(01)号寄存器的数据作为B的输入。

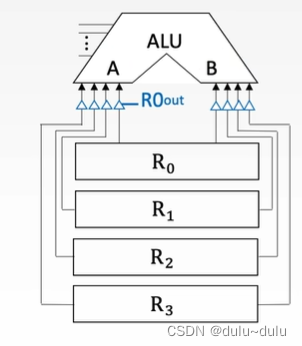

2.使用三态门

可以控制每一路是否输出。每个三态门有三个接口,第一个接口就是输入的接口,第二个接口是输出的接口,正常情况下三态门是不导电的,当第三个接口

(表示R0寄存器数据的输出)接收的输入信号是高电平时,这个三态门就能导电,即这个三态门对应的寄存器的数据可以通过。

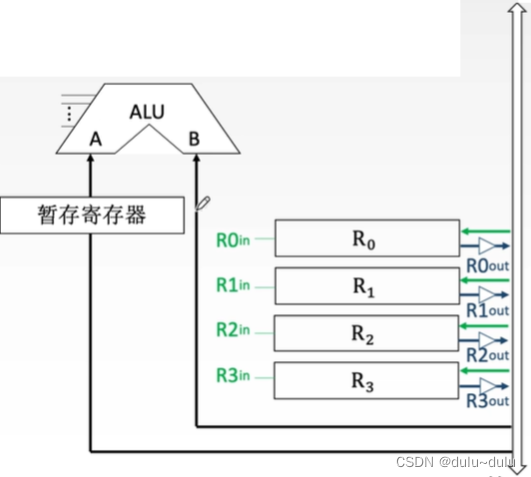

采用专用数据通路方式方式,若部件特别多,连线会越来越复杂,制造成本和工艺难度也会提高,如何解决呢?可以采用另一种数据通路的设计方式---内部单总线方式:

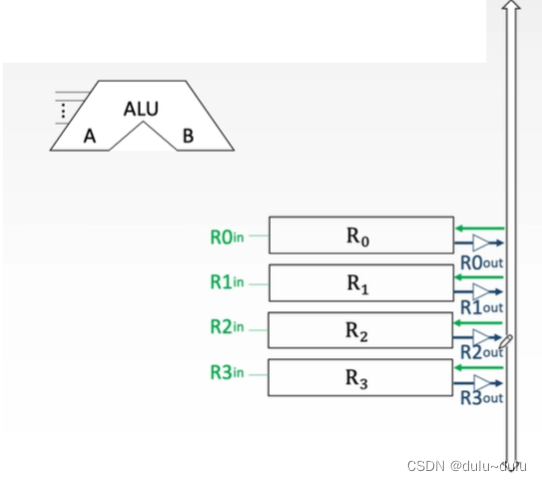

CPU内部会设置总线,将所有寄存器的输入端和输出端都连接到这条公共的通路上。可以将信号输出到这个通路上,也可以从这一通路上接收信号。

如下图所示,若想把R0的数据复制到R2中,就需要将

与

导通,从而完成数据传输。

使用内部单总线方式,结构简单容易实现,但数据传输存在较多冲突的现象,性能较低。例如下图所示,ALU需要完成R0寄存器数据+R1寄存器数据,那么数据同时送到总线上,就会导致总线冲突

如何解决这一问题呢?

可以在某一输入端设置一个暂存寄存器,先将R0的数据通过总线放到暂存寄存器中,接下来撤销R0的输出有效信号,再让R1输出端导通,R1的数据就会通过总线输出到B端

暂存寄存器:用于暂存从主存读来的数据,这个数据不用存放在通用寄存器中,就不会破坏其原有内容。例如完成ADD R0数据,主存地址数据,那么主存地址数据就可以暂存到暂存寄存器中,作为A端输入,而R0数据就可以作为B端输入。

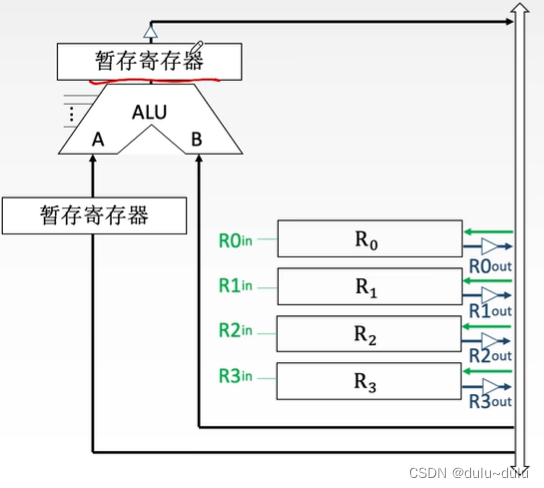

ALU的两个输入端输入的二进制信号稳定,输出端才能输出正确的结果,所以为保证输出端输出的信号稳定,就可以在输出端也放一个暂存寄存器。

如图所示,等输出结果稳定后,暂存寄存器的三态门会导通,数据就会通过通过内部单总线再传回给某一寄存器。例如ADD R0,R2,运算的结果就会传输到R0寄存器中(R0的

要导通)

为了实现某些更复杂的功能,暂存寄存器也可以增加一些功能,例如将其改造成移位寄存器,累加寄存器,状态字寄存器等,不过也可以专门设置某一功能寄存器。

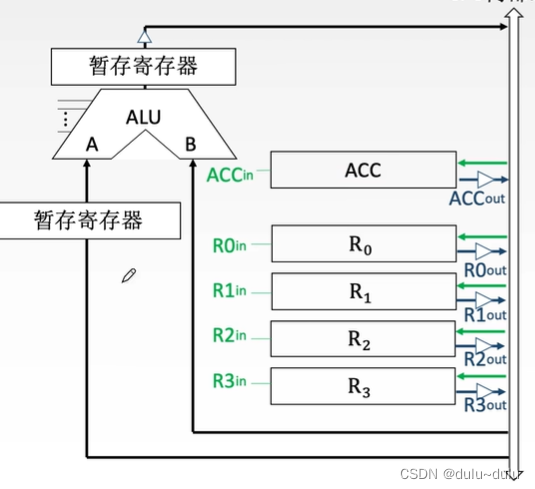

例如下图,专门设置一个累加寄存器,用于存放运算的中间结果。

除了累加寄存器ACC外,运算器还有:

程序状态字寄存器(PSW):保留由算术逻辑运算指令或测试指令的结果而建立的各种状态信息,如溢出标志(OP)、符号标志(SF)、零标志(ZF)、进位标志(CF)等。PSW中的这些位参与并决定微操作的形成。

移位器:对运算结果进行移位运算。

计数器:控制乘除运算的操作步数。

3.控制器的基本结构

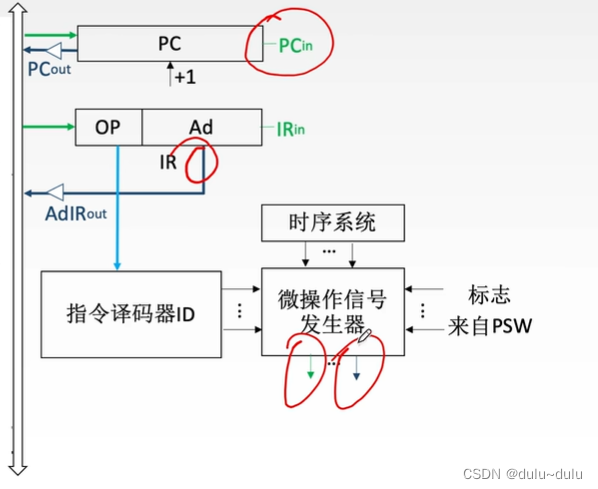

① 程序计数器:用于指出下一条指令在主存中的存放地址。CPU就是根据PC的内容去主存中取指令的。因程序中指令(通常)是顺序执行的,所以PC有自增功能。

注:某些CPU内部,PC自增的功能是交给ALU实现的。

② 指令寄存器:用于保存当前正在执行的那条指令。

一条指令会分为操作码和地址码,地址码可能有多个,其指明了操作数的地址,所以地址码的数据会输出到地址总线上,而操作码会送到指令译码器中:

③ 指令译码器:仅对操作码字段进行译码,向控制器提供特定的操作信号。

译码器的输出信号会作为微操作信号发生器的输入信号:

④ 微操作信号发生器:根据IR的内容(指令)、PSW的内容(状态信息)及时序信号,产生控制整个计算机系统所需的各种控制信号,其结构有组合逻辑型和存储逻辑型两种。

微操作序列的执行需要有先后次序,其通过时序系统控制:

⑤ 时序系统:用于产生各种时序信号,它们都是由统一时钟(CLOCK)分频得到。

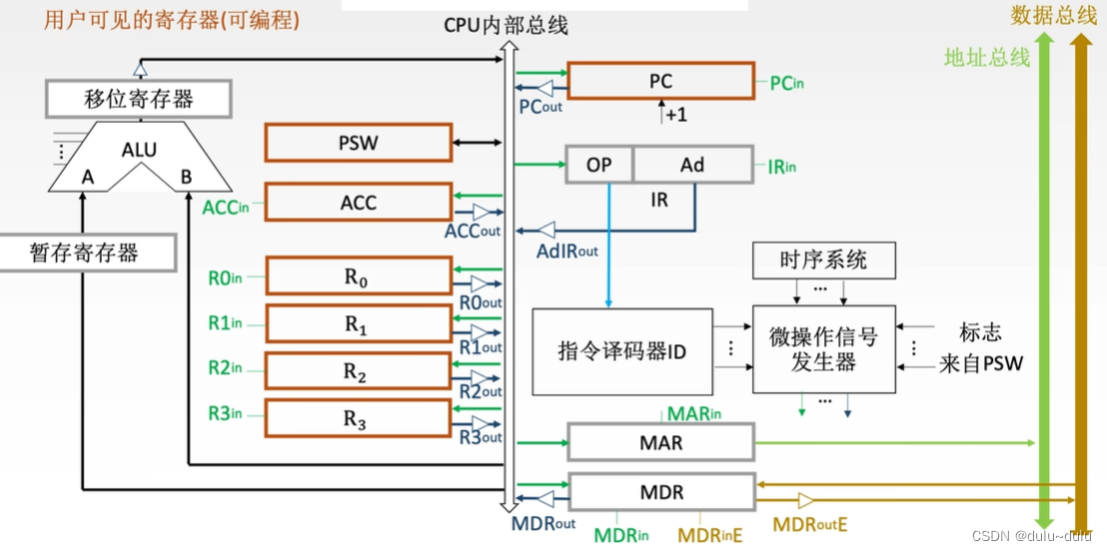

如下图所示,寄存器的输入/输出信号是否有效,都是通过微操作信号发生器决定的,例如

有效,并且

有效,则说明将这条指令的地址码信息通过总线传送到PC中

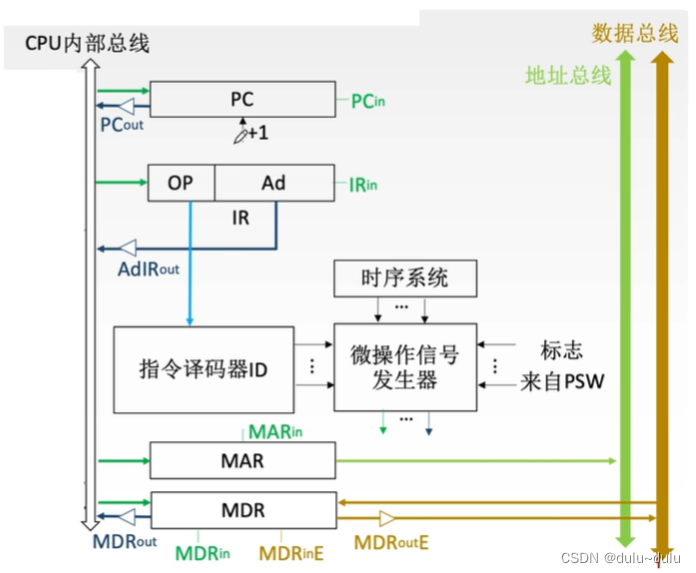

⑥ 存储器地址寄存器(MAR):用于存放所要访问的主存单元的地址。

⑦ 存储器数据寄存器(MDR):用于存放向主存写入的信息或从主存中读出的信息。

注:尽管之前讲的MAR,MDR是集成在主存中的,但是事实上现代计算机中,MAR与MDR就是集成在CPU中的

如下图所示,

有效,并且

有效,则可以将这条指令指向的操作数在内存中的地址存放在MAR中,MAR将地址信息通过外部地址总线传递给主存,主存通过这一地址信息查找相应的主存单元,再将数据通过外部数据总线,传回给CPU中的MDR中。

如上图所示,MDRin表示CPU内部总线输入通路是否有效,而MDRinE则表示CPU外部的数据总线输入通路是否有效,MDRout和MDRoutE同理。

注:CPU的内部总线指的是CPU部件进行数据传输的通路,外部总线(地址总线,控制总线,数据总线)指的是CPU与外部设备(主存,I/O设备)的数据传输的通路。

4.CPU的基本结构

CPU的基本结构如下图所示:

橙色部分表示用户可见的寄存器(就是用户可修改的寄存器),即PC,PSW,ACC,以及通用寄存器,举个例子:

对于PC,用户可通过条件转移指令或无条件转移指令改变PC的值。

对于PSW,某些条件转移指令需要用到PSW的值,例如if...else,需要通过PSW的特殊位判断是否进行条件转移。

对于ACC,用户采用加法,乘法都会改变ACC的值。

对于通用寄存器,用户可以通过指令读/写通用寄存器的数据。

注:对用户可见,不代表用户就可修改。例如,PSW对用户可见,但不允许用户直接修改其值。这是因为PSW中的信息是由操作系统或处理器自动设置的,反映了程序当前的执行状态和CPU的内部状态。如果允许用户随意修改PSW,可能会导致程序状态的不一致或混乱,甚至引发系统错误或崩溃。

灰色部分表示用户不可见寄存器,这些寄存器用于辅助CPU工作。

例如:MAR,MDR,IR和暂存寄存器

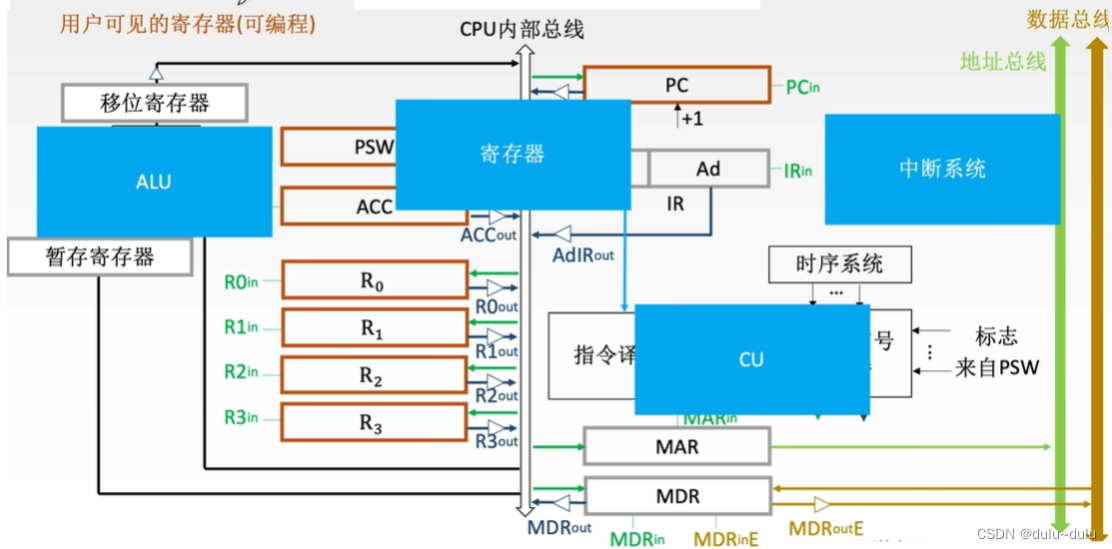

CPU逻辑上可以分为以下四大部分:ALU,寄存器,CU和中断系统

本文详细介绍了CPU的组成部分,包括其功能如指令控制、操作控制、时间控制和中断处理,以及运算器和控制器的内部结构,如ALU、通用寄存器、专用数据通路与内部单总线设计。重点讲解了暂存寄存器的作用以及控制器中的关键组件,如程序计数器和指令寄存器等。

本文详细介绍了CPU的组成部分,包括其功能如指令控制、操作控制、时间控制和中断处理,以及运算器和控制器的内部结构,如ALU、通用寄存器、专用数据通路与内部单总线设计。重点讲解了暂存寄存器的作用以及控制器中的关键组件,如程序计数器和指令寄存器等。

1852

1852

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?