- 实验目的:

本次实验旨在实现一个先行进位加法器。首先实现一位全加器,再实现四位CLU,最后实现四位CLA

2.实验原理:

4位先行进位加法器是一种用于实现4位二进制加法的电路。它通过使用先行进位制(Carry Look Ahead)的原理来实现高速加法。

该加法器将两个4位二进制数相加,包括四个二进制位数相加(A0到A3和B0到B3)。它还有一个输入控制信号(Cin),表示进位输入。

该加法器的设计目标是减少计算进位的延迟时间。传统的加法器需要等待低位的进位信号传递到高位,才能正确计算出最终结果。但是,使用先行进位制的加法器可以通过对每一位进行逻辑操作,同时计算出最终结果和进位信号,从而避免了等待进位信号的延迟。

具体原理如下:

1. 预先计算每一位的进位信号(G)和非进位信号(P)。对于每一位,G = Ai AND Bi,P = Ai OR Bi。

2. 进一步计算每一位的进位传递信号(Pi)和进位产生信号(Gi)。对于每一位,Pi = P0 + G0P1 + G0G1P2 + G0G1G2P3,Gi = G0G1G2G3。

3. 最后,计算每一位的和(Si)。对于每一位,Si = Ai XOR Bi XOR Ci,其中Ci是前一位的进位信号。

通过以上步骤,4位先行进位加法器可以同时输出4位的和(S0到S3)和进位输出Cout。

使用先行进位制的加法器相对于传统加法器的优点是,可以大大减少进位传递的延迟,从而提高运算速度。然而,其缺点是需要更多的逻辑门电路来实现,从而增加了成本和功耗。

3.实验步骤

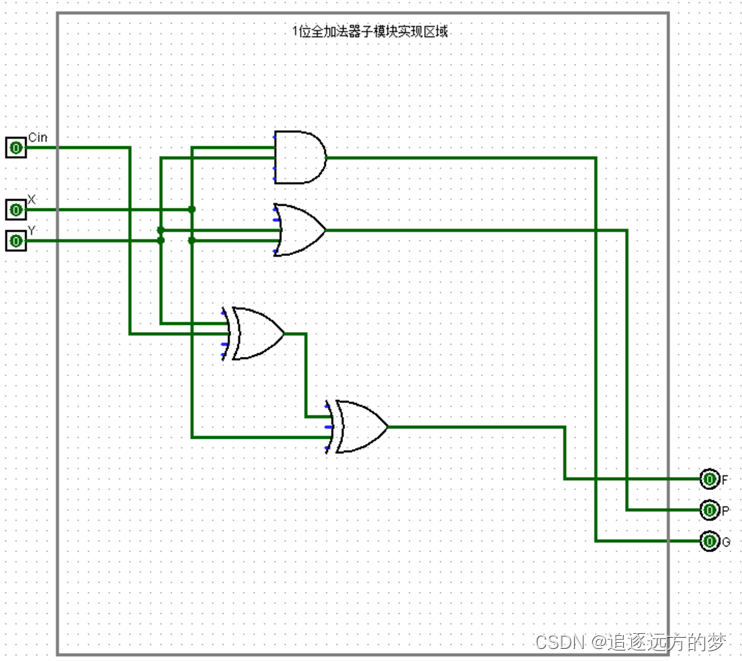

一位全加器实现:

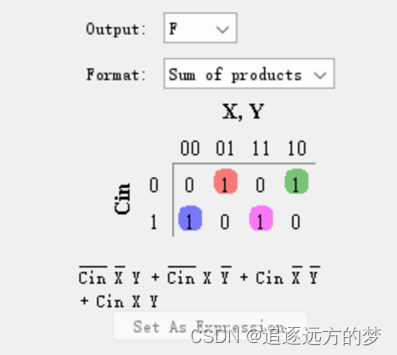

1位全加器,两个位输入X、Y和进位输入Cin,输出加法计算结果F、进位传递位P和进位生成位G。注:如果使用Logisim内置的多位异或门,需要注意异或门输出为1的对应行为。

F=X ^ Y ^ Cin P=X | Y G=X & Y

下面是真值表和卡诺图:

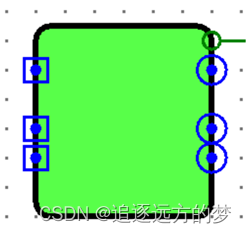

简单封装一下:

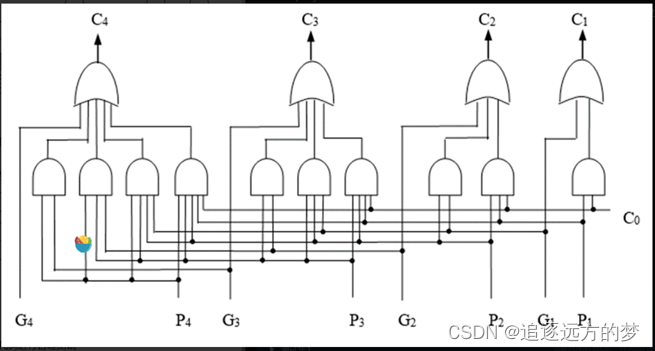

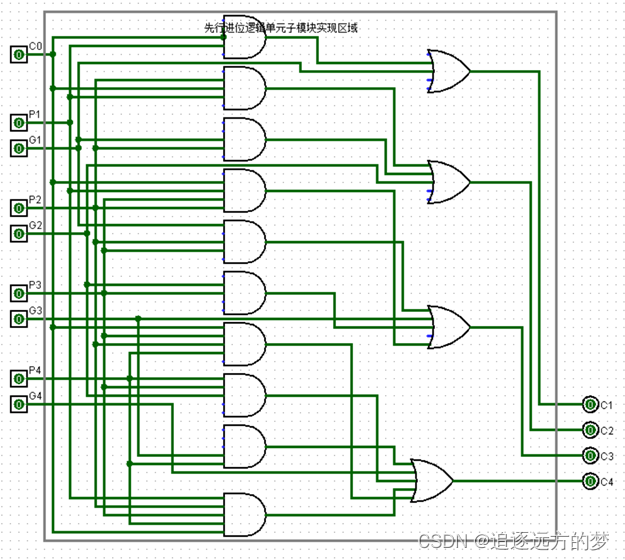

4位CLU实现:4位的组内先行进位部件(CLU),其输入为4位进位传递信号P1、P2、P3、P4,4位进位生成信号G1、G2、G3、G4,和一位进位输入Cin(同C0);其输出为四位进位信号C1、C2、C3、C4。

如上图所示。

下面我们进行电路连接:

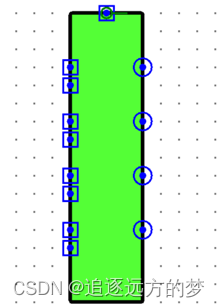

简单封装一下:

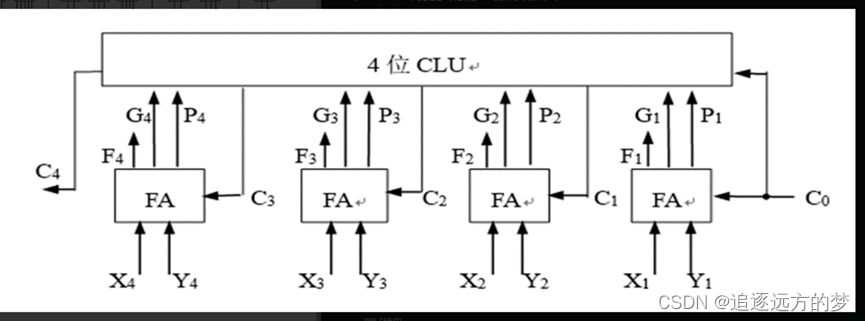

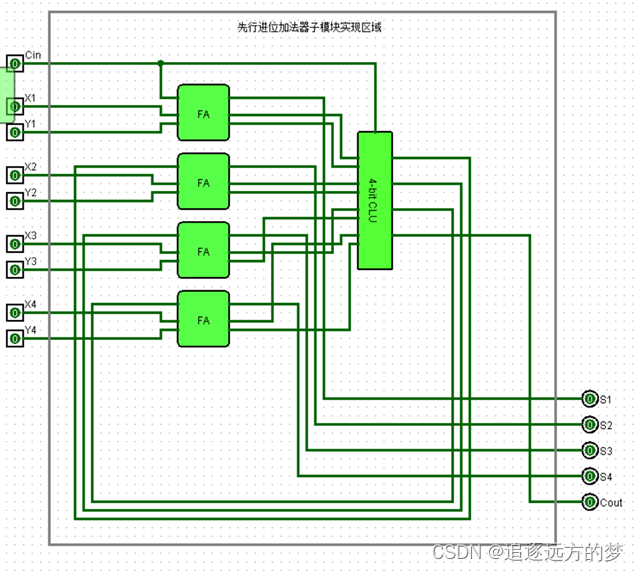

4位CLA实现:其输入为一位Cin、四位操作数X1 ~ X4、四位操作数Y1 ~ Y4,输出为最高位进位Cout、四位计算结果S1 ~ S4。

具体实现如下:

4.结果测试

经测试,结果正确。

5.总结与思考:

4位先行进位加法器的作用是对两个4位二进制数进行加法运算,并输出4位结果和进位信号。它可以用于各种数字逻辑电路中,例如计算机中的算术逻辑单元(ALU)或者数据通路。

利:

1. 高速运算:先行进位加法器通过并行计算每一位的进位信号,避免了等待进位信号传递的延迟,从而提高了运算速度。相对于传统的级级进位加法器,它可以快速地完成加法运算。

2. 适用于并行处理:先行进位加法器的设计使得每一位的计算可以独立进行,并不依赖于前一位的进位信号。这种特性使得它非常适合用于并行处理,可以同时计算多组数据的加法运算。

弊:

1. 复杂性增加:相对于传统的级级进位加法器,先行进位加法器需要更多的逻辑门电路来实现。这样会增加电路的复杂性,增加了电路设计和布局的难度。

2. 成本和功耗增加:由于先行进位加法器需要更多的逻辑门电路,因此它可能会占用更多的芯片面积,增加了生产成本,并且可能会增加功耗。

3. 设计复杂度:先行进位加法器的设计本身相对复杂,需要进行逻辑门的级联、信号传递和计算。这对于电路设计师来说可能需要更高的专业知识和技能。

综上所述,4位先行进位加法器具有高速运算和并行处理的优势,但其复杂性以及成本和功耗的增加可能是其弊端。在实际应用中,根据具体的需求和约束条件,选择适合的加法器结构是一个综合考虑的问题。

文章详细介绍了4位先行进位加法器的工作原理和实现步骤,包括一位全加器、4位CLU和CLA的构建。通过先行进位技术,实现了高速加法,减少了进位延迟,但也带来了电路复杂性和成本增加的问题。该加法器适用于高速运算和并行处理场景。

文章详细介绍了4位先行进位加法器的工作原理和实现步骤,包括一位全加器、4位CLU和CLA的构建。通过先行进位技术,实现了高速加法,减少了进位延迟,但也带来了电路复杂性和成本增加的问题。该加法器适用于高速运算和并行处理场景。

3421

3421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?