在讨论跨时钟域处理之前,必须先了解数字设计中的一个现象,亚稳态。

一.亚稳态

1.亚稳态的定义

数字设计中,信号在一定时间内不能够达到稳定的0或者1的现象。

2.亚稳态产生的原因

(1)建立和保持时间不满足

在数字设计中,触发器的数据建立和保持都需要一定的时间,这是由于电路内部结构一决定的,比如一个CMOS反相器,当输入为低时,输出为高,输出结果时通过输入与界限电压比较产生的,比如高于Voh,输出为高,低于VoL,输出为低。在Vol和Voh之间还有未定义的部分。

(2)采样时钟采集到跳变沿

当两个时钟不一样时,很容易出现采集数据时采集到亚稳态。

多时钟域设计中,经常出现不同时钟模块需要进行通信的过程,容易产生亚稳态。这是跨时钟域处理必须要面对的一个问题。需要及时的解决,降低亚稳态产生的概率。避免亚稳态影响后一级电路。

一.跨时钟域处理

1.含义

在数字设的过程中,多时钟域控制各个模块现象是普遍存在的一个现象,各个模块之间使用的时钟有可能不一样,但是各个模块需要彼此通信,不同时钟很容易产生亚稳态现象。所以跨时钟域处理是必要的。

2.解决方法

常用的解决方法是使用同步化技术,同步化技术主要包括:同步器,保持寄存器和握手,异步FIFO

2.1 同步器

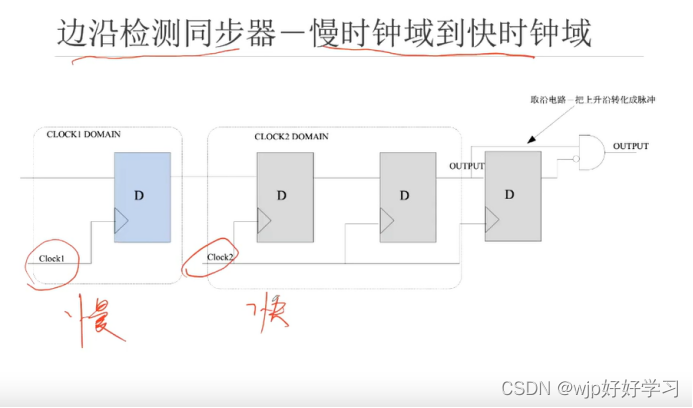

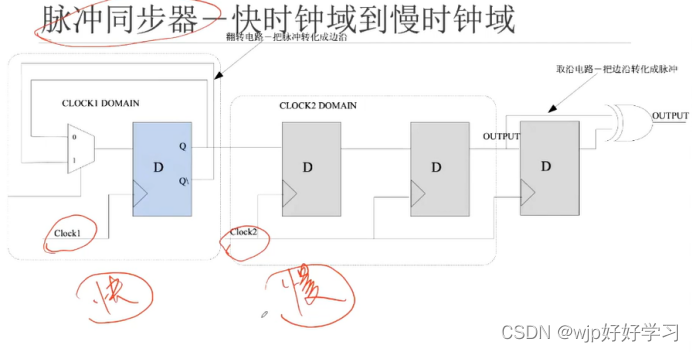

使用两级寄存器(接收时钟域),是一级寄存概率的平方,两级并不能完全消除亚稳态危害,但是提高了可靠性,减少其发生的概率(注意是概率,并不是解决不让他产生亚稳态,只是不让这个亚稳态传播)。一级概率很大,三级改善不大,同步器延时-1或者2个接收时钟。同步器分为电平同步器,边沿检测同步器,脉冲同步器三种。

2.1.1 电平同步

2.1.2 边沿检测同步器

2.1.3 脉冲同步器

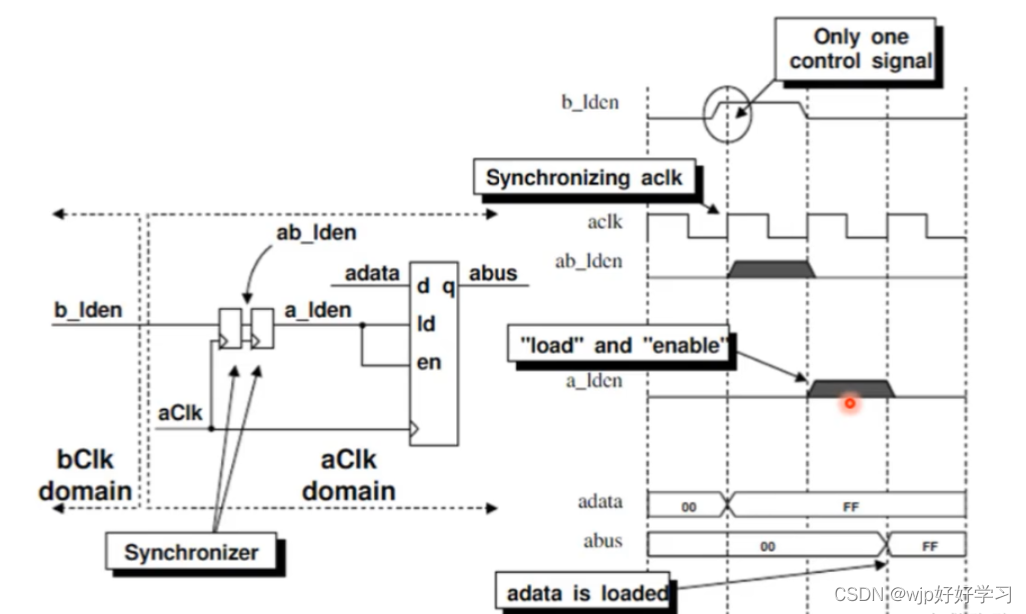

2.2 多路信号的处理

多路信号由于到达输入端的时间不同,这个延时可能被同步器进一步的放大。我们有时候要求两个信号之间有一定的时间差,比如控制信号置位和使能,置位必须在使能信号有效后,置位有效。经过同步器,延时放大,有可能直接错位。比如下图的情况,这是我们不愿意看到的。

2.2.1 多路合成一路

将上述信号合成一路,然后在分开控制。如下图:

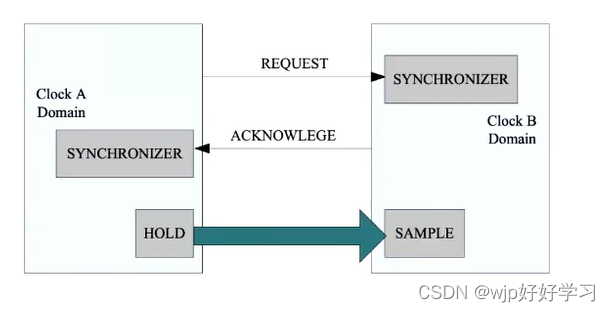

2.2.2 使用保持寄存器和握手

不过这种情况的效率太低,要一个个的接收,多路信号的处理一般用下面一种方法

2.2.3 异步FIFO

同步FIFO:写时钟和读时钟为同一个时钟

异步FIFO:写时钟和读时钟为独立时钟

跨时钟域的数据信号需要用到异步的FIFO,隔离时钟域,匹配读写速度。

异步FIFO核心:读写空满标志的产生,通过读写指针比较,一般使用格雷码和同步器结合。

812

812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?