Snoop Control Unit,窥探控制单元,详情见UG585。SCU主要是解决ARM的L1和L2的缓存协调(因为两个processor的缓存是共用的)和AXI总线的ACP存取的,也就是DMA等高速中断需求的外设。

SCU 块将两个 Cortex-A9 处理器连接到内存子系统,并包含智能管理两个处理器和 L2 缓存之间的数据缓存一致性。这块负责管理互连仲裁、通信、缓存和系统Cortex-A9 处理器的内存传输和缓存一致性。 The APU also exposes the capabilities of the SCU to system accelerators that are implemented in the PL through the accelerator coherency port (ACP) interface。该接口允许 PL 主机共享和访问处理器缓存层次结构。这里提供的系统一致性不仅提高了性能,但也降低了维护所涉及的软件复杂性每个操作系统驱动程序内的软件一致性。

SCU 模块通过高速缓存一致性总线与每个 Cortex-A9 处理器通信(CCB) 并管理 L1 和 L2 缓存之间的一致性。 SCU 支持 MESI通过避免不必要的访问,提供更高的电源效率和性能系统访问。The block implements duplicated 4-way associative tag RAMs acting as a local

directory that lists coherent cache lines held in the CPU L1 data caches。该目录允许 SCU以极快的速度检查数据是否在 L1 数据缓存中,并且不会中断处理器。此外,只能过滤对共享数据的处理器的访问。

SCU 还可以将clean的数据从一个处理器缓存复制到另一个,从而无需主存储器访问以执行此任务。 此外,它可以在处理器,跳过共享状态并避免与回写相关的延迟。

重要提示:需要注意的是,Cortex-A9 不保证 L1 Cache之间的指令一致性,因为处理器无法直接修改 L1 内容。

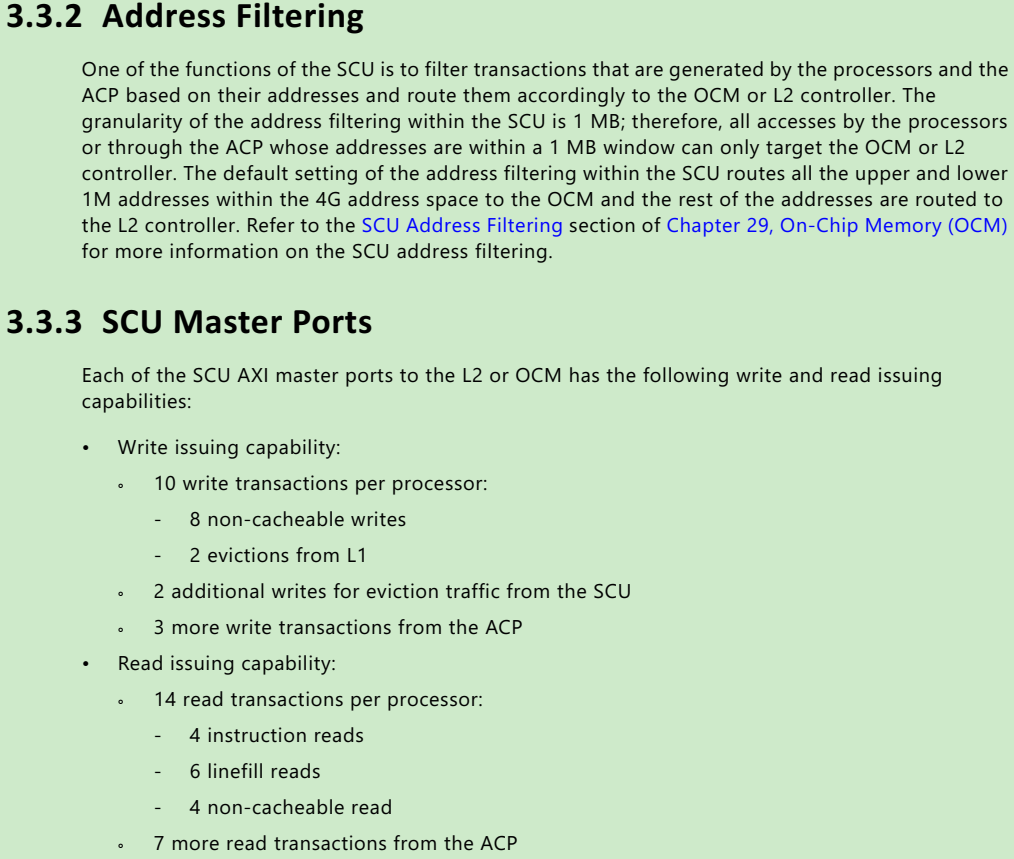

地址过滤:

SCU 的功能之一是过滤由处理器和ACP 基于它们的地址并将它们相应地路由到 OCM 或 L2 控制器。 SCU内地址过滤的粒度为1MB。

总结一下:

SCU通过AXI接口将一至四个Cortex-A9处理器连接到存储器系统。

SCU功能是:

1、在Cortex-A9处理器之间维护数据Cache的一致性

2、初始化L2 AXI存储器访问

3、在请求L2访问的Cortex-A9处理器之间仲裁

4、管理ACP【译者注:加速器一致性端口】访问。

注:Cortex-A9 SCU不支持对指令Cache一致性的硬件管理。

SCU实现了对ARM架构安全扩展的支持。

独立的CPU事件监视器可以被配置用于收集对SCU操作的各类事件统计信息。

SCU控制寄存器:

SCU控制寄存器的特征如下:

目的:

1、允许用PL310【译者注:PrimeCell二级Cache控制器】对L2投机地进行行填充

2、允许迫使所有连到端口0的设备

3、允许IC待机模式

4、允许SCU待机模式

5、允许奇偶校验支持

6、允许地址过滤

7、允许SCU

使用限制:

1、在安全状态下这个寄存器是可写的,如果SAC寄存器中的相关位置1

2、在非安全状态下这个寄存器是可写的,如果SAC以及SNSAC寄存器中的相关位置1

配置:在所有Cortex-A9多处理器配置中都可用

SCU控制寄存器介绍:

[位6] IC待机模式允许:当置1时,如果此时没有中断是未决的,并且没有处理器在执行一次读写请求,那么停止中断控制器时钟。

[位5] SCU待机允许:当置1时,如果此时所有处理器处于WFI模式,在ACP(如果实现的话)上没有未决请求,并且在SCU中没有剩余活动,那么SCU CLK被关闭。

当SCU CLK被关闭时,在ACP上的ARREADYS,AWREADYS以及DWREADYS被迫使为HIGH。当任一处理器离开WFI模式,或在ACP上有一个新的请求时,时钟被打开。

[位4] 迫使所有到端口0的设备允许:当置1时,所有来自ACP或AxCACHE = DV的处理器的请求被迫使在AXI主机端口M0上被发布。

[位3] 投机的行填充允许:当置1时,一致性的行填充请求被投机地并行发送到带有标签查找的PL310中。如果标签查找失败,那么已确认的行填充被发送到PL310,并更早地获得R数据,因为数据请求已经被投机请求所启动。这个特征只有当PL310在设计中存在时才能工作。

[位2] 奇偶校验打开:1=奇偶校验打开;0=奇偶校验关闭,这个是默认设置。

[位1] 地址过滤允许:1=地址过滤打开;0=地址过滤关闭。默认值为从复位退出时所采样到的FILTEREN的值。这个位总是为0,如果SCU在单主机端口配置中实现。

[位0] SCU允许:1=SCU允许;0=SCU禁止。这是默认设置。

SCU配置寄存器:

SCU配置寄存器的特征是:

1、目的:——读总线上所连接的所有Cortex-A9处理器的标签RAM大小

——判定参与一致性的Cortex-A9处理器

——读总线上所连接的Cortex-A9处理器的个数

2、使用限制:此寄存器是只读的

3、配置:在所有Cortex-A9多处理器配置中可用

4、属性:见SCU寄存器中的寄存器概述,在P2-3

SCU配置寄存器功能描述:

标签RAM大小:最多四个CPU(CPU0~3);64KB Cache,每个标签RAM有256个索引;32KB Cache,每个标签RAM有128个索引;16KB Cache,每个标签RAM有64个索引。

CPU SMP:定义Cortex-A9处理器是处于对称多处理器(SMP)还是非对称多处理器(AMP)模式中;

0表示指定的Cortex-A9处理器处于AMP模式,并不参与一致性或是不存在

1表示指定的Cortex-A9处理器处于SMP模式,并参与一致性

参考:

ARM Cortex-A9 MPCore手册——窥探控制单元(Snoop Control Unit) - zenny_chen - 博客园

614

614

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?