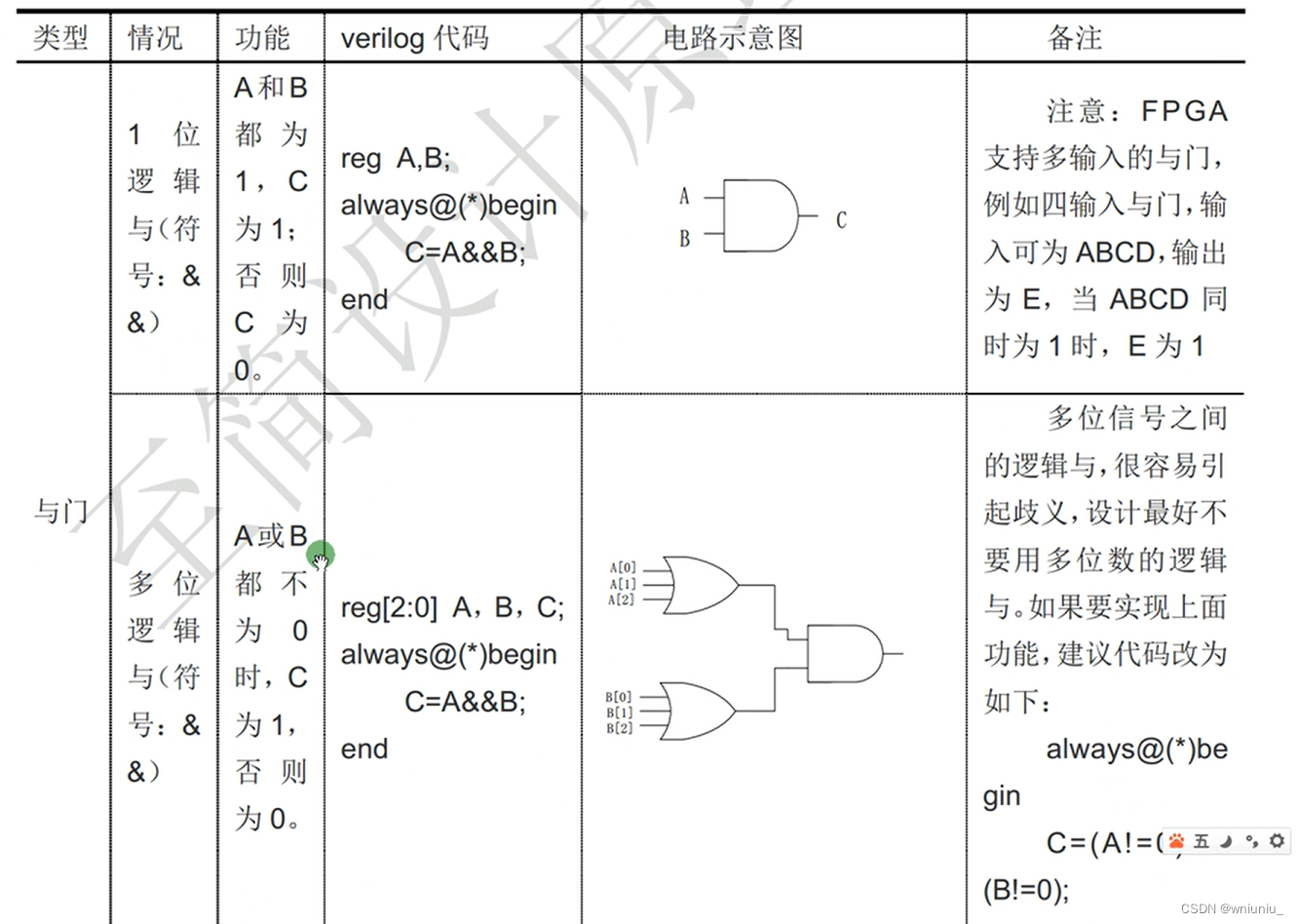

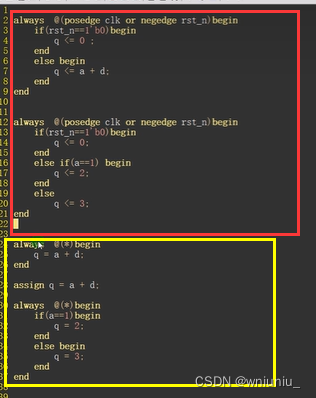

注意多位和一位

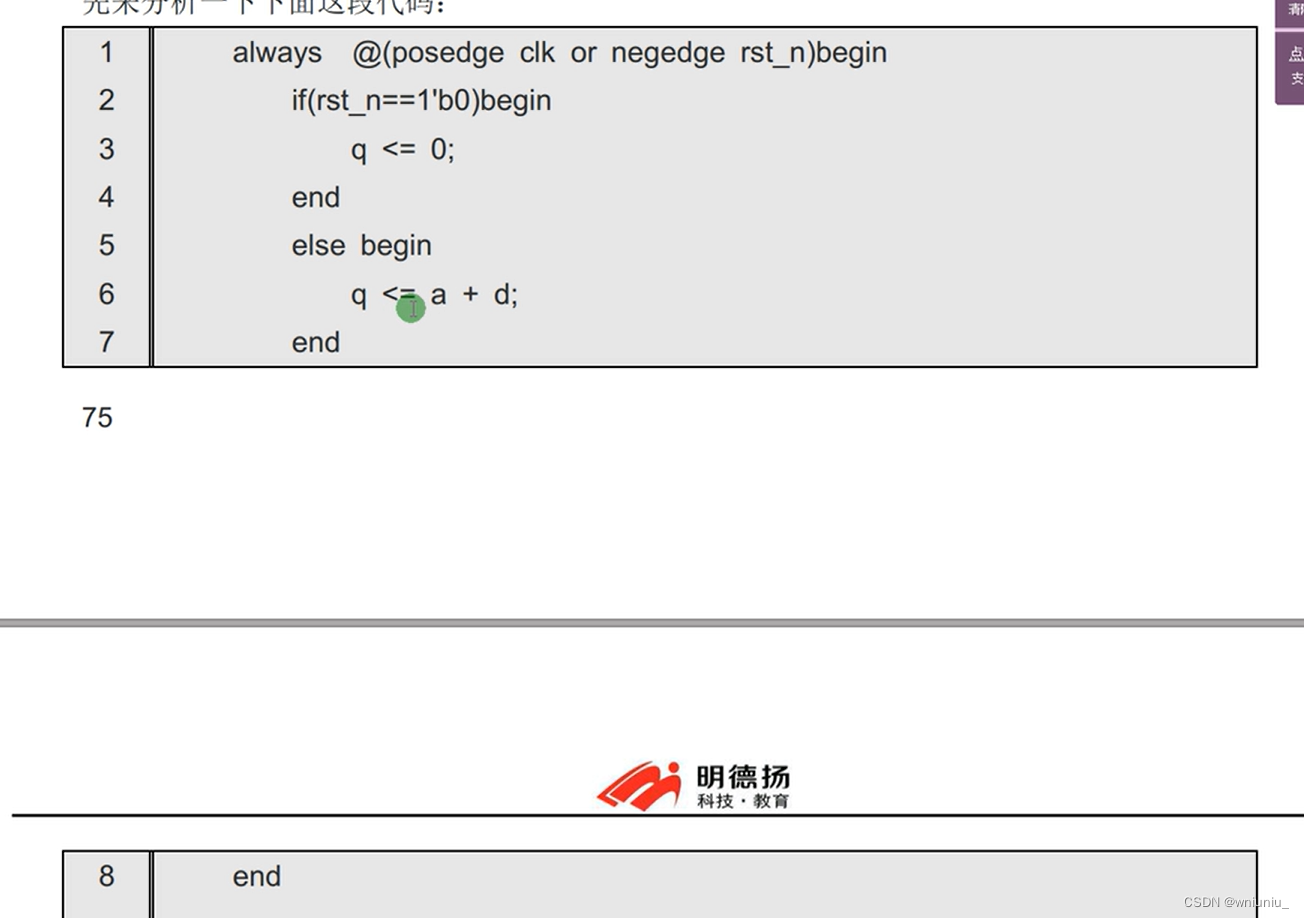

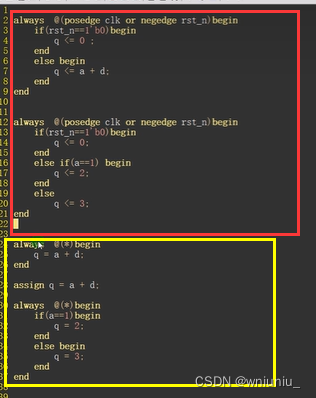

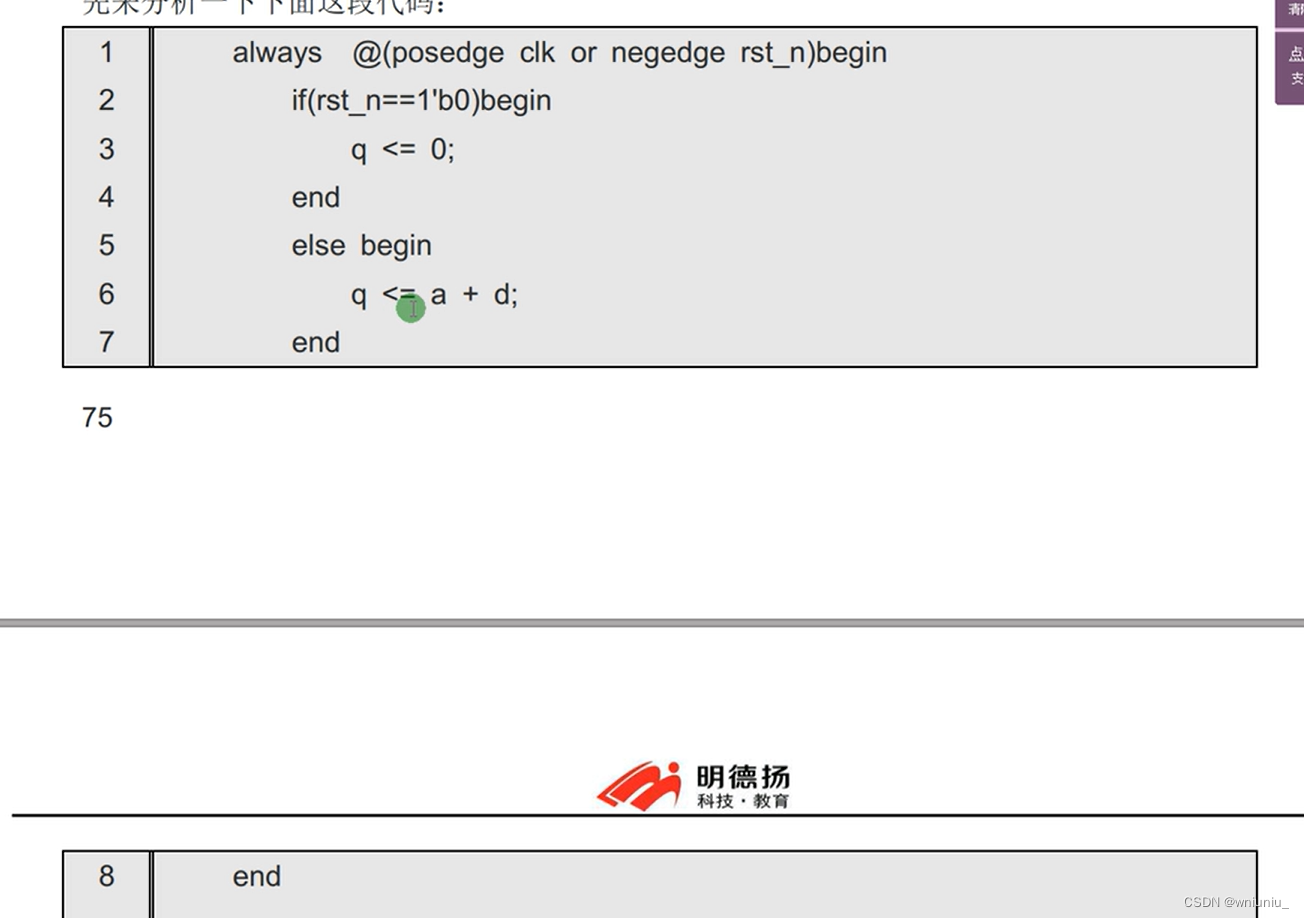

上面的是时序下面的是组合

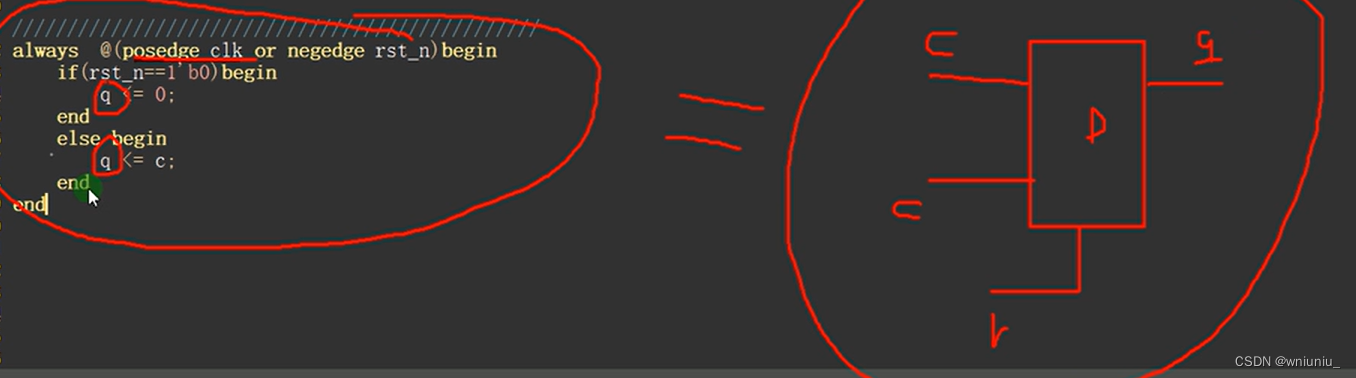

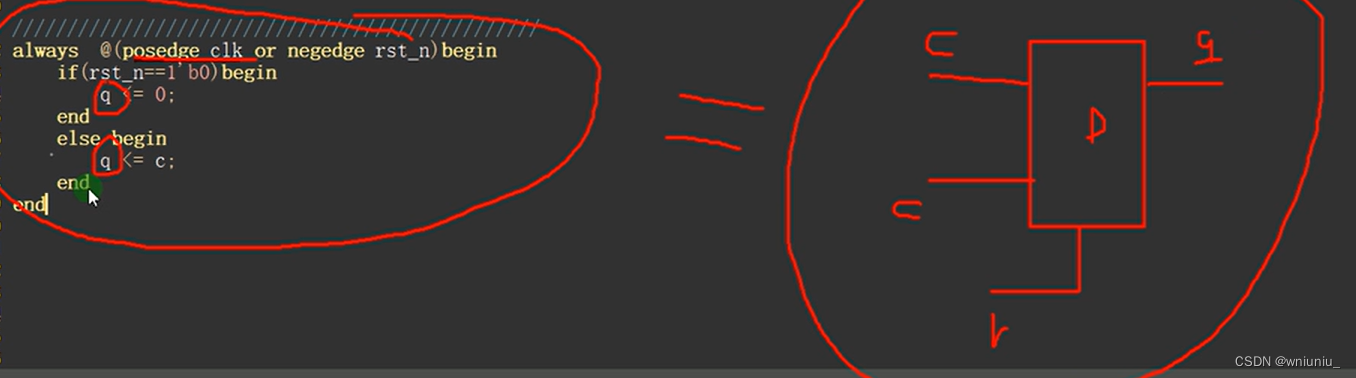

时序逻辑就是组合加上一个D触发器

注意多位和一位

上面的是时序下面的是组合

时序逻辑就是组合加上一个D触发器

2171

2171

3047

3047

6661

6661

2万+

2万+

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?