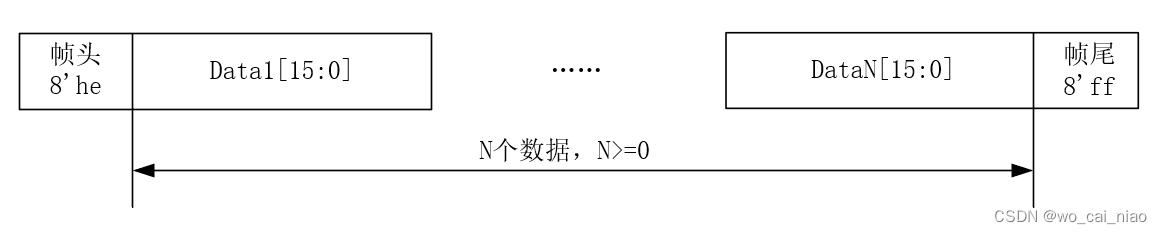

定义一个数据帧,帧头为8'he,帧尾为8'hff(有效数据不包含帧尾),当数据输入时开始检测,若检测到帧头后直接检测到帧尾,则认为数据帧为空包,拉高abort信号(持续一个clk);

若不为帧尾则为有效数据,每收到16bit数据进行输出,并拉高data_valid信号(持续一个clk);继续检测该数据流是否为帧尾,如果为帧尾,本次数据提取结束;如果不为帧尾,仍为有效数据,重复上述过程,直到数据结束。

module data_extract(

input wire clk,

input wire rst_n,

input wire din,

output reg data_abort,

output reg[15:0] data,

output reg data_valid,

);

endmodule

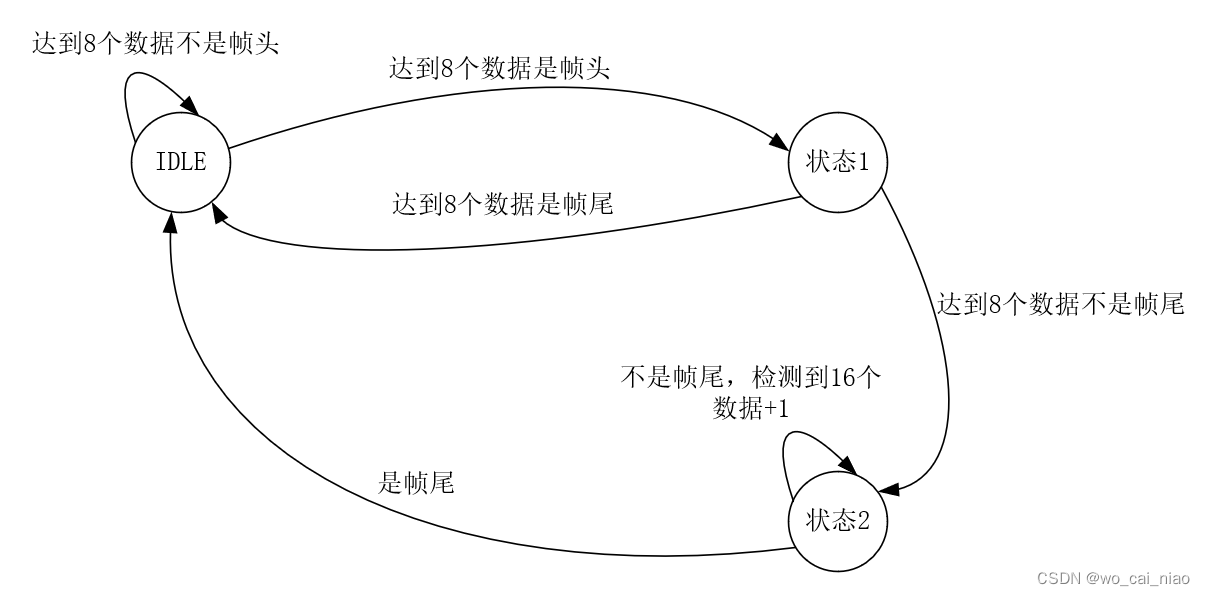

解:这明显是一个状态机,定义3个状态:IDLE、状态1、状态2

3103

3103

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?