代码锁存 : 将重要使用频率高的代码锁存到RAM甚至Cache中,提高CPU的访问速度,加快程序运行。

RAM相比众所周知,这里主要先总结介绍和学习一下Cache的原理和设计结构。

---------------------------------------------------------------------------------------------------------

Cache:

*首先介绍一下cache发发展背景和趋势:

虽然CPU主频的提升会带动系统性能的改善,但系统性能的提高不仅仅取决于CPU,还与系统架构、指令结构、信息在各个部件之间的传送速度及存储部件的存取速度等因素有关,特别是与CPU/内存之间的存取速度有关。

若CPU工作速度较高,但内存存取速度相对较低,则造成CPU等待,降低处理速度,浪费CPU的能力。

如何减少CPU与内存之间的速度差异?有4种办法:

一种是在基本总线周期中插入等待,但这样会浪费CPU的能力。

另一种方法是采用存取时间较快的SRAM作存储器,这样虽然解决了CPU与存储器间速度不匹配的问题,但却大幅提升了系统成本。

第三种方法是在慢速的DRAM和快速CPU之间插入一速度较快、容量较小的SRAM,起到缓冲作用;使CPU既可以以较快速度存取SRAM中的数据,又不使系统成本上升过高,这就是Cache法。

再有一种方法,采用新型存储器。

目前,一般采用第三种方法。它是PC系统在不大增加成本的前提下,使性能提升的一个非常有效的技术。

------------------------------

*Cache的工作原理:

Cache的工作原理是基于程序访问的局部性。

对大量典型程序运行情况的分析结果表明,在一个较短的时间间隔内,由程序产生的地址往往集中在存储器逻辑地址空间的很小范围内。指令地址的分布本来就是连续的,再加上循环程序段和子程序段要重复执行多次。因此,对这些地址的访问就自然地具有时间上集中分布的倾向。

数据分布的这种集中倾向不如指令明显,但对数组的存储和访问以及工作单元的选择都可以使存储器地址相对集中。这种对局部范围的存储器地址频繁访问,而对此范围以外的地址则访问甚少的现象,就称为程序访问的局部性。

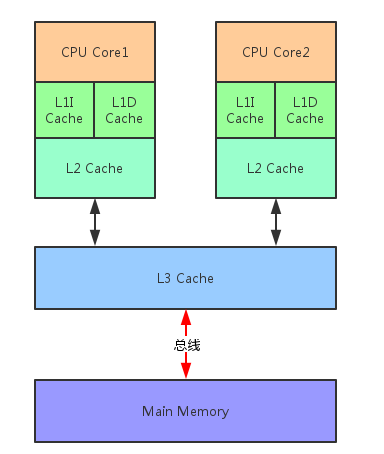

根据程序的局部性原理,可以在主存和CPU通用寄存器之间设置一个高速的容量相对较小的存储器,把正在执行的指令地址附近的一部分指令或数据从主存调入这个存储器,供CPU在一段时间内使用。这对提高程序的运行速度有很大的作用。这个介于主存和CPU之间的高速小容量存储器称作高速缓冲存储器(Cache)。

操作系统正是依据此原理,不断地将与当前指令集相关联的一个不太大的后继指令集从内存读到Cache,然后再与CPU高速传送,从而达到速度匹配。CPU对存储器进行数据请求时,通常先访问Cache。由于局部性原理不能保证所请求的数据百分之百地在Cache中,这里便存在一个命中率。即CPU在任一时刻从Cache中可靠获取数据的几率。命中率越高,正确获取数据的可靠性就越大。一般来说,Cache的存储容量比主存的容量小得多,但不能太小,太小会使命中率太低;也没有必要过大,过大不仅会增加成本,而且当容量超过一定值后,命中率随容量的增加将不会有明显地增长。

只要Cache的空间与主存空间在一定范围内保持适当比例的映射关系,Cache的命中率还是相当高的。 一般规定Cache与内存的空间比为4:1000,即128kB Cache可映射32MB内存;256kB Cache可映射64MB内存。在这种情况下,命中率都在90%以上。至于没有命中的数据,CPU只好直接从内存获取。获取的同时,也把它拷进Cache,以备下次访问。

----------------------------------------------------------------------------------------------------------------

当CPU需要数据时,首先到cache内部去寻找,如果找到了,则称为命中了(cache hit),如果没有找到,则称为丢失(cache miss),这时CPU必须到内存去读取数据,并且将其保存在cache中以备后用。

*Cache的基本结构

————————————————————————————————————————————————————

Cache的组织结构

* 参见回答:https://www.zhihu.com/question/24612442/answer/53107450 (用心阁)*

————————————————————————————————————————————

i-cache和d-cache区别:

Cache存储器其一般实现方式主要有三种,分别是全相联,直接映射和组相联。全相联最灵活但是实现比较复杂。直接映射比较容易实现,但是可能产生快速抖动。组相联则是前两者的一个折衷。

DCache控制器在整个DCache中处于非常重要的地位,它控制了整个DCache所要进行的操作,同时会在发生缺失时采取相应的对策。其主要功能如下:

读操作

写操作

参考:

http://www.cnblogs.com/waytofall/p/3998854.html (CPU 与 Cache)

http://www.jianshu.com/p/061a5d66ea20 (Cache结构)

http://blog.csdn.net/zdl1016/article/details/8882092 (概述)

http://blog.chinaunix.net/uid-24517893-id-334964.html (可能的不一致性)

1786

1786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?