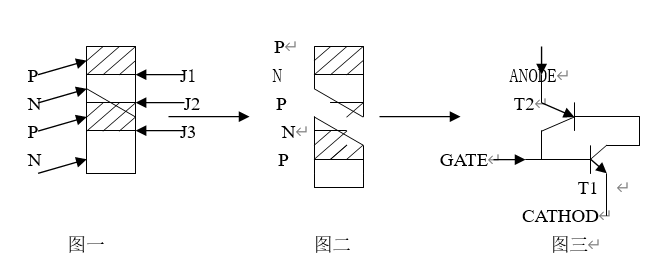

可控硅物理结构如下图所示,P-N-P-N,就象两只背靠背的三极管。我们先来分析栅极不作电气联接的情况。当可控硅阴极电位大于阳极电位,J1和J3结反偏,器件截止。当可控硅阴极电位小于阳极电位,J1和J3正偏,但J2反偏,器件仍然截止。如果J2的反偏电压达到引发雪崩击穿时,器件的导通特性就象单个正偏的PN结一样。

进而分析图三:可控硅可等效为一个PNP晶体管和一个NPN晶体管集基相联而成,T1的集电极为T2提供基极电流,T1的基极电流由外电路通过栅极加T2的集电极电流提供。如果T1、T2集基环路的增益超过单位增益。则环路电流持续保持增加,T1、T2进入饱和,可控硅被称为锁定,阳极到阴极的电流由外部偏置电路决定。因此有几种情况能使可控硅进入锁定状态。

- 超过击穿电压使可控硅进入导通

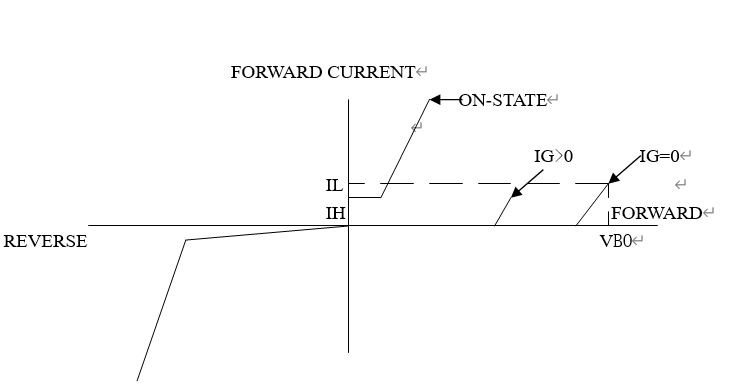

当加在可控硅阳极和阴极之间的电压超过击穿电压VBO时,可控硅导通,VBO大于器件的额定电压。在击穿电压时可控硅的阳极电流被称作为锁定电流IL。

击穿电压触发在大多数电路设计中是避免使用的。它的特点是正向电压的下降沿很陡,下降时间是栅极触发的二十分之一;但它允许的di/dt却比栅极触发的低。

- 靠漏电流使可控硅进入导通

可控硅的结温升高,漏电流也增大。如果结温允许升得足够高,使漏电流大到足以触发

可控硅体内的集基耦合正反馈环路进入锁定而导通。在结温超过Tjmax的某一温度,可控硅将不存在截止电压。

3.利用dv/dt使可控硅导通

任何PN结都有电容,结面积越大,电容也越大。当一锯齿电压加到可控硅的阳极和阴极之间,充电电流由下式表示:

ic=Cdv/dt

如果电流足够大,将引起可控硅导通。

4.利用栅极触发可控硅导通

这是一种常用的方法使可控硅导通,提供栅极电流触发可控硅体内的集基耦合正反馈环,使可控硅进入锁定状态。如图四所示。

当栅流大于零时,使可控硅进入导通的正向偏压小于VBO。手册上提供要保证某一可控硅可靠触发导通的栅流和偏压条件。同时,可控硅的触发特性和温度有关,所以要保证栅极触发脉冲的宽度和时间必须足够保证在所有条件下使可控硅进入锁定。

设计时注意几点:

- 电路设计上要保证dIF/dt不能超过规定指标,否则可控硅将被损坏。

- 在栅极触发电流设计上,比较好的方法是提供高速大电流过驱动脉冲(dIG/dt)(不超过额定功率),使可控硅快速导通,怎样可提高dIF/dt的额定值。

- 一旦可控硅锁定,栅极驱动即可减小或完全取消。使用脉冲信号触发可控硅可减小栅极功耗。

- 在栅极触发方式中,触发脉冲必须持续到可控硅的阳、极之间电流超过锁定电流IL才能取消。一旦稳定的导通状态建立,IH是维持可控硅导通的最小电流。要关断可控硅,必须使可控硅的导通电流降至IH之下。具体做法可减小可控硅两端所施加的电压。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?