Lab3 Rewrite V1.0

版本控制

| 版本 | 描述 |

|---|---|

| V0 | 没有使用原书上的Lab3,而是自己重新写了一个lab3 |

| V1.0 | 相对V0变化: 修改了文件名,各阶段以_stage结尾(因为if是关键词,所以module名不能叫if,遂改为if_stage,为了统一命名,将所有module后缀加上_stage) 删除了imm_sign信号(默认对立即数进行有符号数扩展) 由于对sw指令进行了重新理解:无论如何都是需要将rt_data传递给EXE阶段,故将部分译码逻辑进行后移至EXE阶段,避免id_to_exe_data总线过于庞大 将ins_shmat剔除出id_to_exe_data,因为imm包括ins_shamt 对信号进行重命名(例如在ID阶段有个信号叫rf_we,最终要传递给WB阶段,那么在EXE阶段,该信号叫作exe_rf_we,同理mem_rf_we,wb_rf_we),不然都叫rf_we,Debug的时候太痛苦了。 |

Top顶层

接口信号

MYCPU_TOP.v(TOP)

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 取指端访存接口 | |||

| inst_sram_en | 1 | O | 指令RAM使能信号,高电平有效 |

| inst_sram_wen | 4 | O | 指令RAM字节写使能信号,高电平有效 |

| inst_sram_addr | 32 | O | 指令RMA读写地址,字节寻址 |

| inst_sram_wdata | 32 | O | 指令RAM写数据 |

| inst_sram_rdata | 32 | I | 指令RAM读数据 |

| 数据端访存接口 | |||

| data_sram_en | 1 | O | 数据RAM使能信号,高电平有效 |

| data_sram_wen | 4 | O | 数据RAM字节写使能信号,高电平有效 |

| data_sram_addr | 32 | O | 数据RAM读写地址,字节寻址 |

| data_sram_wdata | 32 | O | 数据RAM写数据 |

| data_sram_rdata | 32 | I | 数据RAM读数据 |

| debug信号,供验证平台使用 | |||

| debug_wb_pc | 32 | O | 写回级(多周期最后一级)的PC,需要myCPU里将PC一路传递到写回级 |

| debug_wb_rf_wen | 4 | O | 写回级写寄存器堆(regfiles)的写使能,为字节使能,如果myCPU写regfiles为单字节写使能,则将写使能扩展成4位即可 |

| debug_wb_rf_wnum | 5 | O | 写回级写regfiles的目的寄存器号 |

| debug_wb_rf_wdata | 32 | O | 写回级写regfiles的写数据 |

接口时序

略(MIPS经典五级流水线)

代码结构

MYCPU_TOP.v

|____IF.v

|____ID.v

|____RF.v(2个读端口,1个写端口)

|____EXE.v

|____ALU.v

|____MEM.v

|____WB.v

|____MYCPU.h

DATA_RAM.v

IF.v(修改为IF_STAGE,因为会与关键词if冲突)

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I | 复位信号,低电平同步复位 |

| 与TOP | |||

| inst_sram_en | 1 | O | RAM使能信号,高电平有效 |

| inst_sram_wen | 4 | O | RAM字节写使能信号,高电平有效 |

| inst_sram_addr | 32 | O | RMA读写地址,字节寻址 |

| inst_sram_wdata | 32 | O | RAM写数据 |

| inst_sram_rdata | 32 | I | RAM读数据 |

| 与ID | |||

| id_to_if_allowin | 1 | I | pipe allowin |

| if_to_id_vld | 1 | O | pipe valid |

| if_to_id_data | 64 | O | pipe data(instruction 32-bits, pc 32-bits) |

| jump_bus | 33 | I | branch instructions(enable 1bit,address 32-bits) |

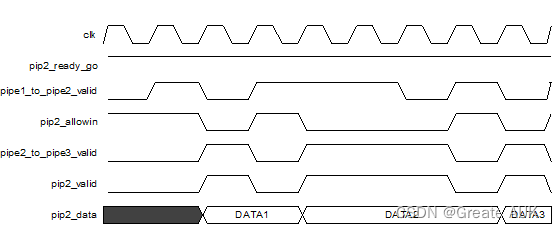

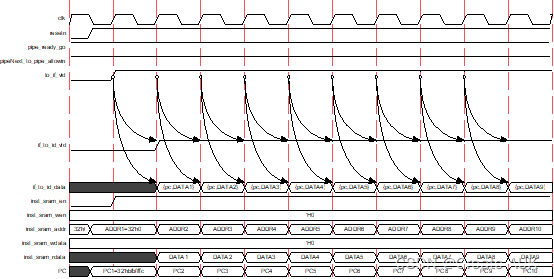

接口时序

ID.v

接口信号

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| 时钟与复位 | |||

| clk | 1 | I | 时钟信号,来自clk_pll的输出时钟 |

| resetn | 1 | I |

本文详细记录了CPU设计Lab3的重构过程,包括版本控制、Top顶层接口信号和时序、各阶段代码结构及优化。在IF、ID、EXE、MEM和WB阶段分别进行了接口和时序的处理,并解决了PC复位、寄存器零值、数据高阻、跳转指令PC值、译码错误等问题。通过Debug,修复了包括lui、addiu、lw、subu、slt、nor、srl、sra、sw/lw、bne等多个指令的执行错误,完善了流水线设计。

本文详细记录了CPU设计Lab3的重构过程,包括版本控制、Top顶层接口信号和时序、各阶段代码结构及优化。在IF、ID、EXE、MEM和WB阶段分别进行了接口和时序的处理,并解决了PC复位、寄存器零值、数据高阻、跳转指令PC值、译码错误等问题。通过Debug,修复了包括lui、addiu、lw、subu、slt、nor、srl、sra、sw/lw、bne等多个指令的执行错误,完善了流水线设计。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

826

826

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?