首先要明白的一点是,在线逻辑分析仪属于一种硬核,集成在FPGA芯片中。传统的FPGA板级调试是由外接的逻辑分析仪连接到FPGA的控制管脚上,然后将内部信号引至引脚IO上,进行板级调试。逻辑分析仪的价格非常昂贵,并且要测试几十个引脚的适合,选择使用外接的逻辑分析仪就比较繁琐了。

而在线逻辑分析仪位于FPGA中,通过一个或多个探针来采集我们所希望观察到的信号,通过片内的JTAG硬件组件,来将捕获到的数据传送给下载器,进而上传到vivado的IDE给用户查看结果。

下面以一个LED闪烁的程序来说明问题

//Author:Liu zhenhua

//Data:2021.10.01 1 @HIT ATCI438

//系统时钟是74.25MHz时钟

module test_adc_clk(

input sys_ret_p, //ZCU板子上的独立按键,按下是高电平

input clk_74_25_P,//ZCU102的差分时钟P端口,74.25MHz时钟

input clk_74_25_N,//ZCU102的差分时钟N端口

output [7:0] led

);

reg [27:0] cnt;

wire sys_clk_bufg; //差分时钟,经过IBUFGDS后的单端信号时钟

wire sys_clk; //经过全局缓冲BUFG之后的单端信号时钟

assign led = (cnt<28'd74250000) ? 8'b11111111 : 8'b00000000;

always@(posedge sys_clk or posedge sys_ret_p)begin

if(sys_ret_p)

cnt <= 28'd0;

else if(cnt < 28'd148500000)

cnt <= cnt + 1'b1;

else

cnt <= 28'd0;

end

//IBUFGDS是时钟信号专用的输入缓冲器,它是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时

//必须使用IBUFGDS作为全局输入缓冲,它支持LVDS的IO标准

IBUFGDS i_ibufgds_adc_0

(.I (clk_74_25_P),

.IB (clk_74_25_N),

.O (sys_clk_bufg) //单端信号时钟

);

BUFG BUFG_inst (

.O(sys_clk), // 1-bit output: Clock output

.I(sys_clk_bufg) // 1-bit input: Clock input

);

ila_0 instance_ila (

.clk(sys_clk), // input wire clk

.probe0(sys_ret_p), // input wire [0:0] probe0

.probe1(led), // input wire [7:0] probe1

.probe2(cnt) // input wire [27:0] probe2

);

endmodule采用的时钟是74.25MHz的时钟,每个时钟的上升沿计数器进行一次累加,刚好1s后,LED的电平进行反转。复位按键按下的时候,计数器清零。

当逻辑部分的代码编写完毕后,再添加ILA的代码,由于它是一个硬核,所以可以直接在vivado软件中进行可视化的配置

在IP catalog中,搜索到ILA(Intergrated Logic Analyzer)

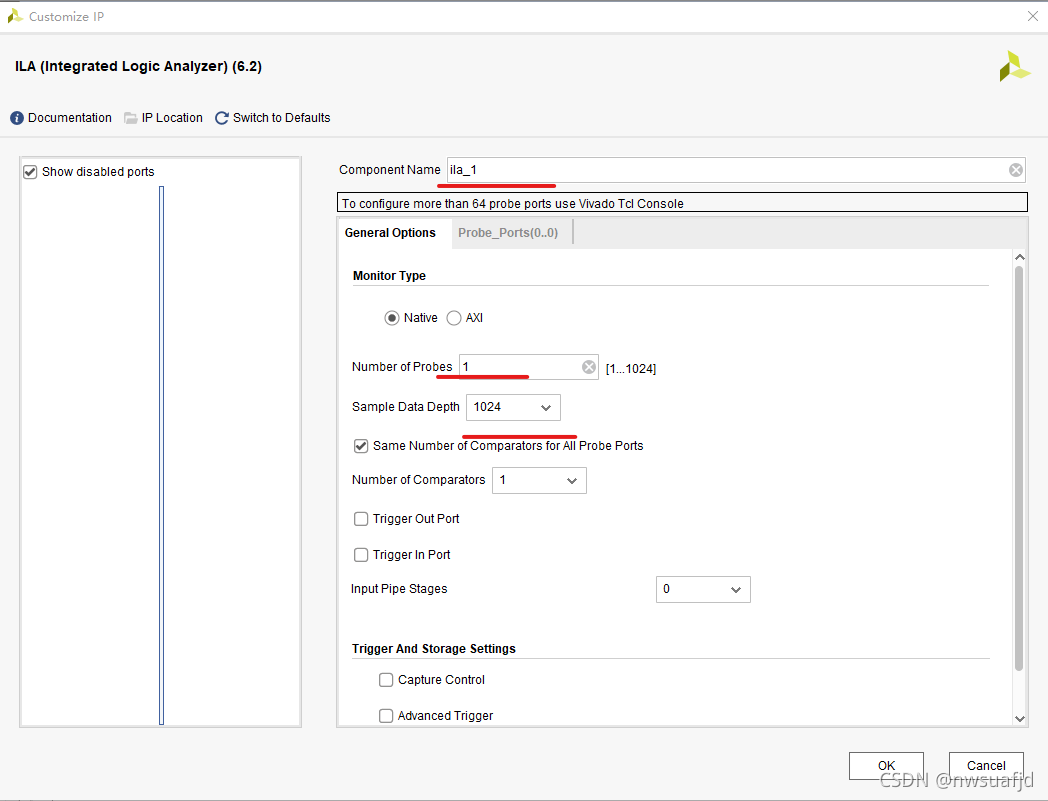

然后设置IP核的名字,默认即可,“Number of probes”是指探针数,也就是你想要观看的信号的数量,注意,即便是一个信号有8位,那么它依然属于一个探针, “Samples data depth”用于设置采样的深度,就是说我们想要观看的信号的时间是固定的一段,不能动态的随时看。

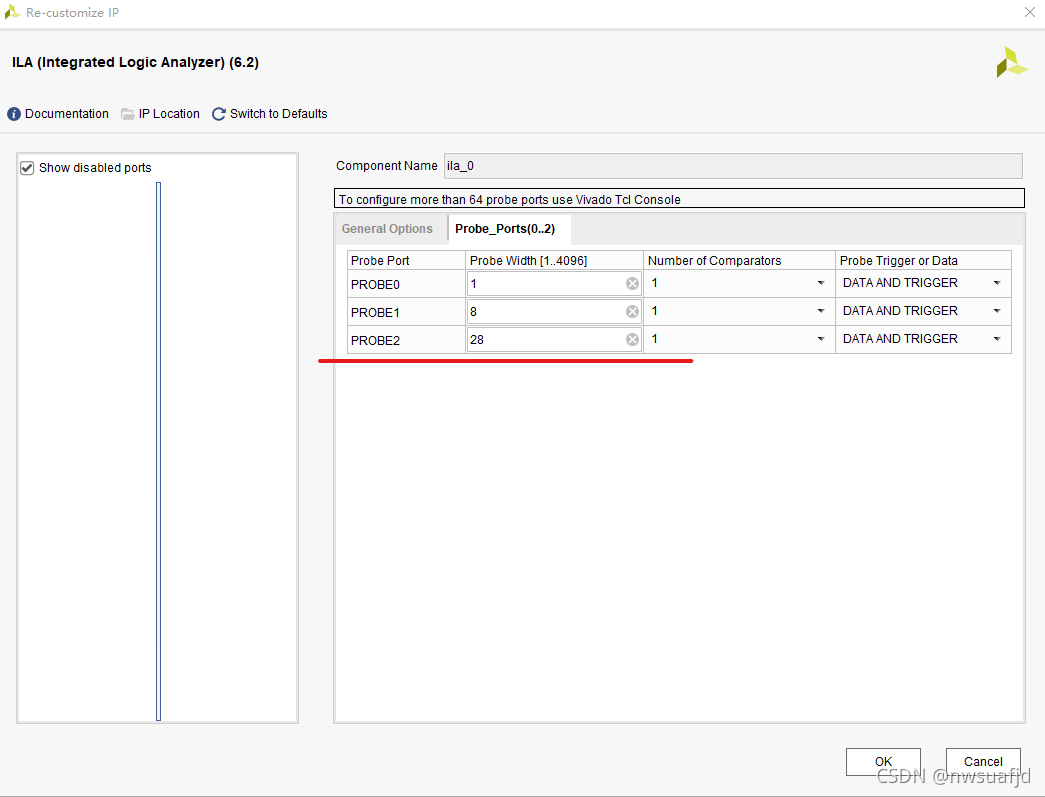

然后是设置每个探针的宽度,其实就是你要观测的信号的位宽。

设置号之后,会进行分析综合 。完成之后,找到例化文件,拷贝到自己的顶层文件中

ila_0 instance_ila (

.clk(sys_clk), // input wire clk

.probe0(sys_ret_p), // input wire [0:0] probe0

.probe1(led), // input wire [7:0] probe1

.probe2(cnt) // input wire [27:0] probe2

);首次要例化时钟,然后就是探针所对应的信号名。

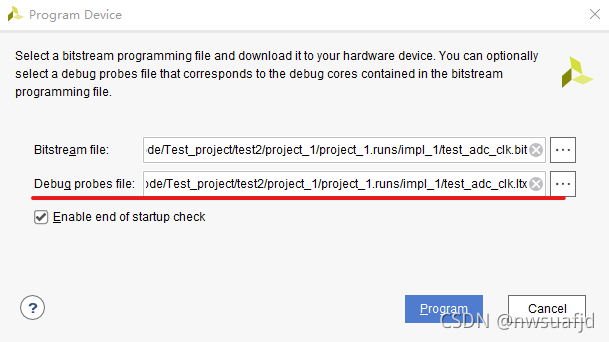

最后生成比特流文件,进行下载,下载的时候,软件会自定识别探针调试文件

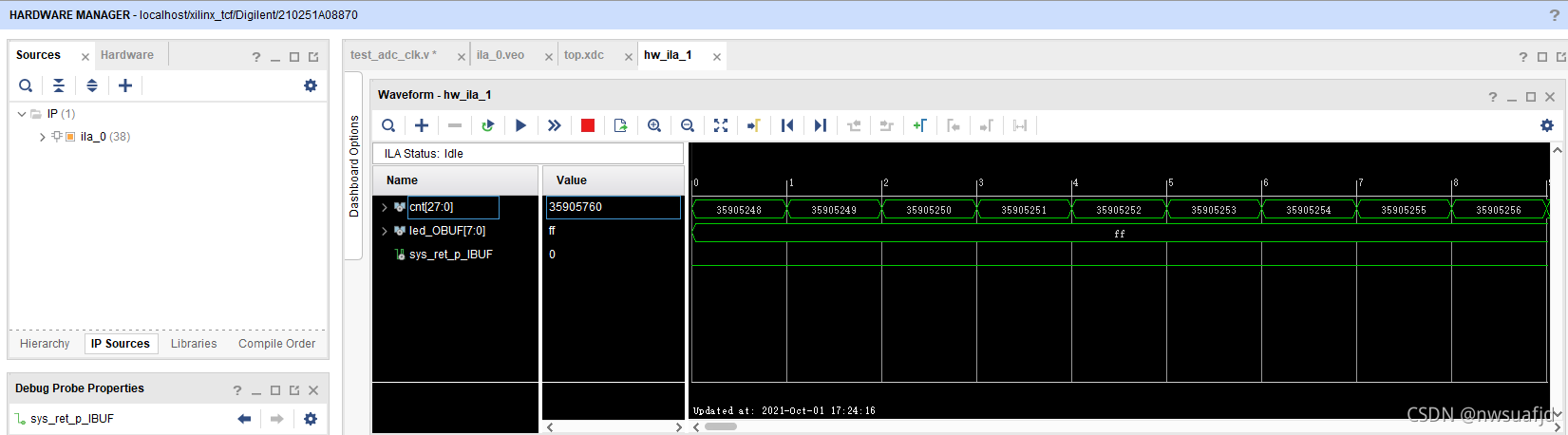

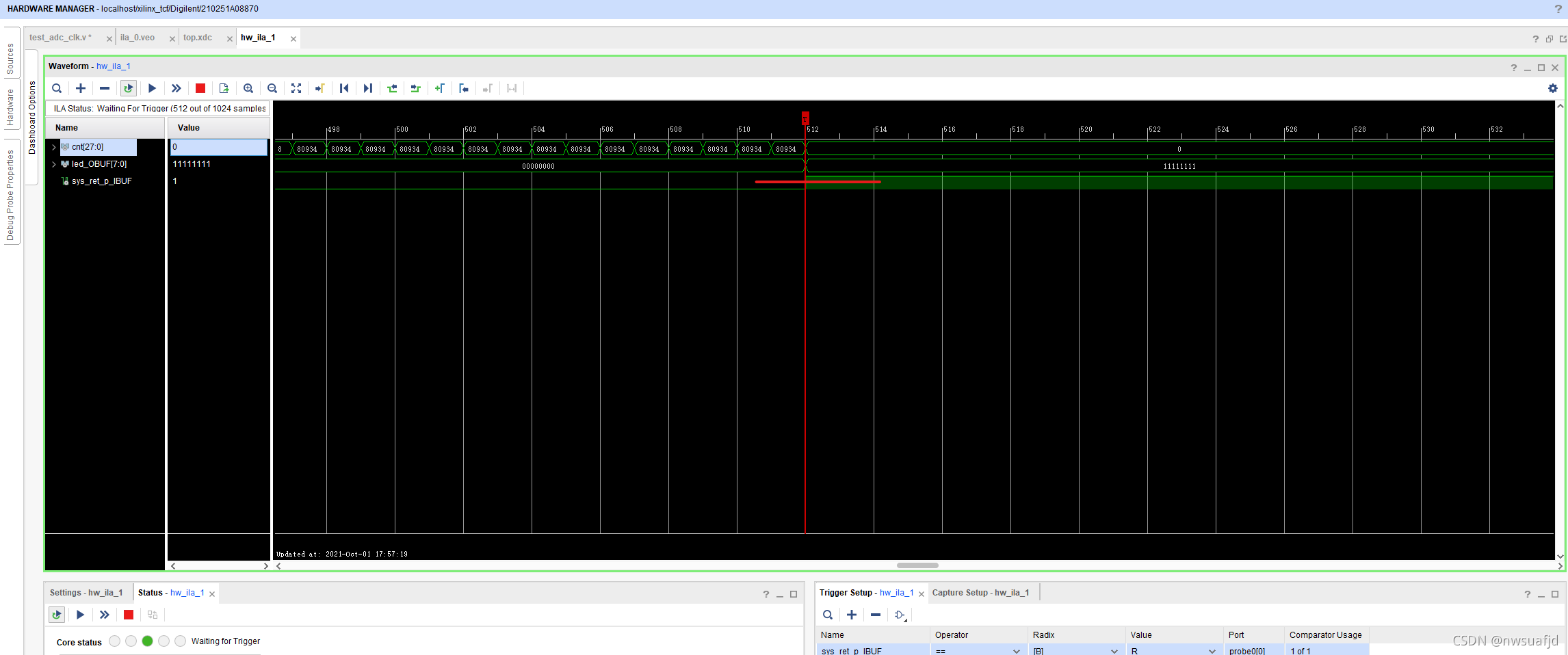

下载好之后,会弹出来波形界面

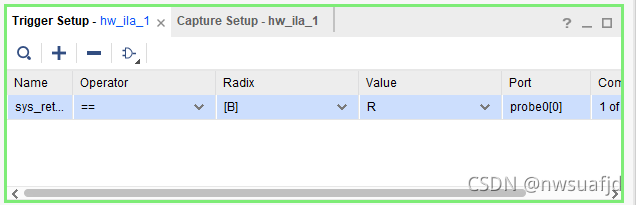

可以添加触发条件

右下角的Trigger Setup,点击+号可以添加某个信号的触发,例如我添加复位键按下的触发:

结果有点不太正确,我实在不明白为什么复位之后,计数器的值始终为0

985

985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?