名称:具有四种信号灯的交通灯控制器Verilog代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

设计具有四种信号灯的交通灯控制器

设计任务

由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄、左拐允许

四盏信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行

线外,左拐灯亮允许车辆向左拐弯。信号灯变换次序为:主支干道交替通行,主干道每次放行亮5s黄灯让行驶中的车辆有时间停到禁行线外,左拐放行15s,亮5s黄灯,支干道放行30s,亮5s黄灯,左拐放行15s,亮5s黄灯。各计时电路为倒计时显示

任务分析

将红、绿、黄、左拐允许四盏信号灯输岀到指示灯上显示,将停放时间结果输岀到数码管上显示。

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

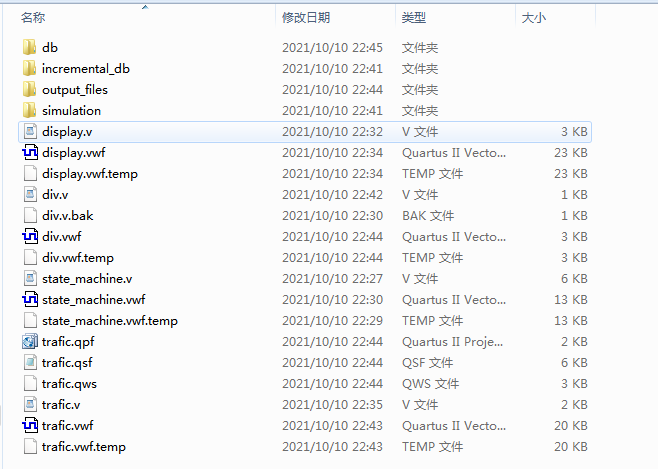

1. 工程文件

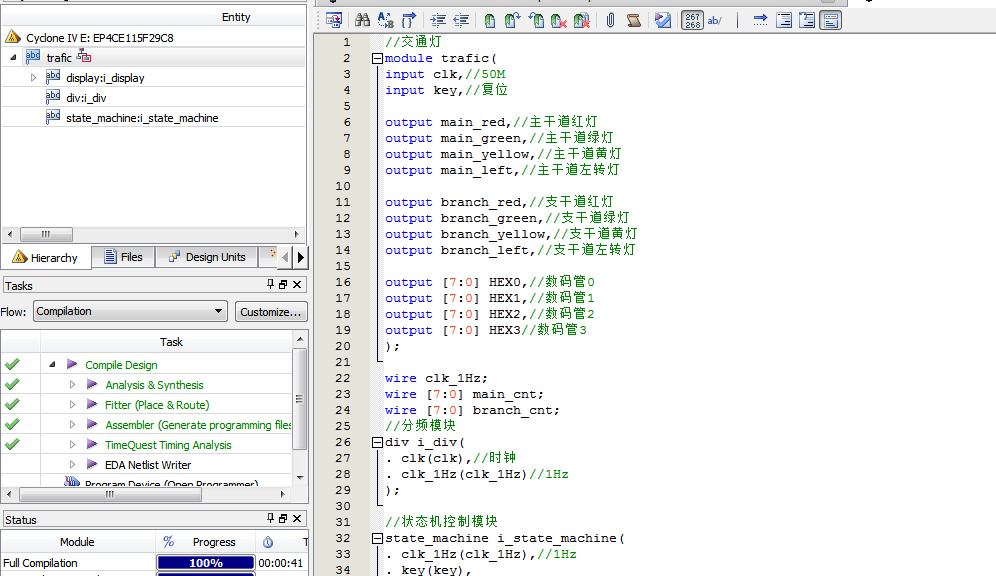

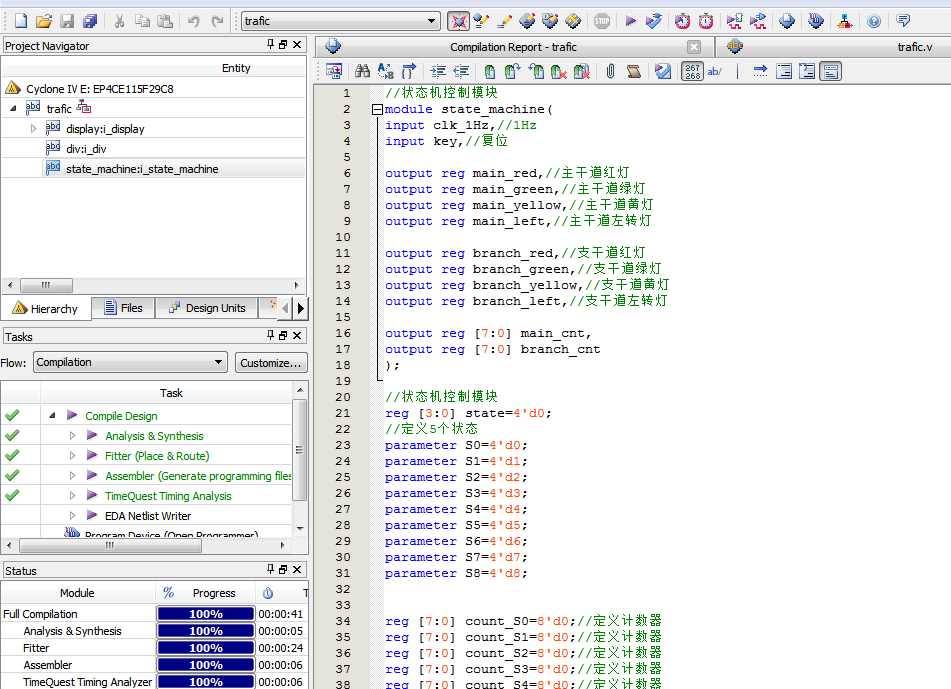

2. 程序文件

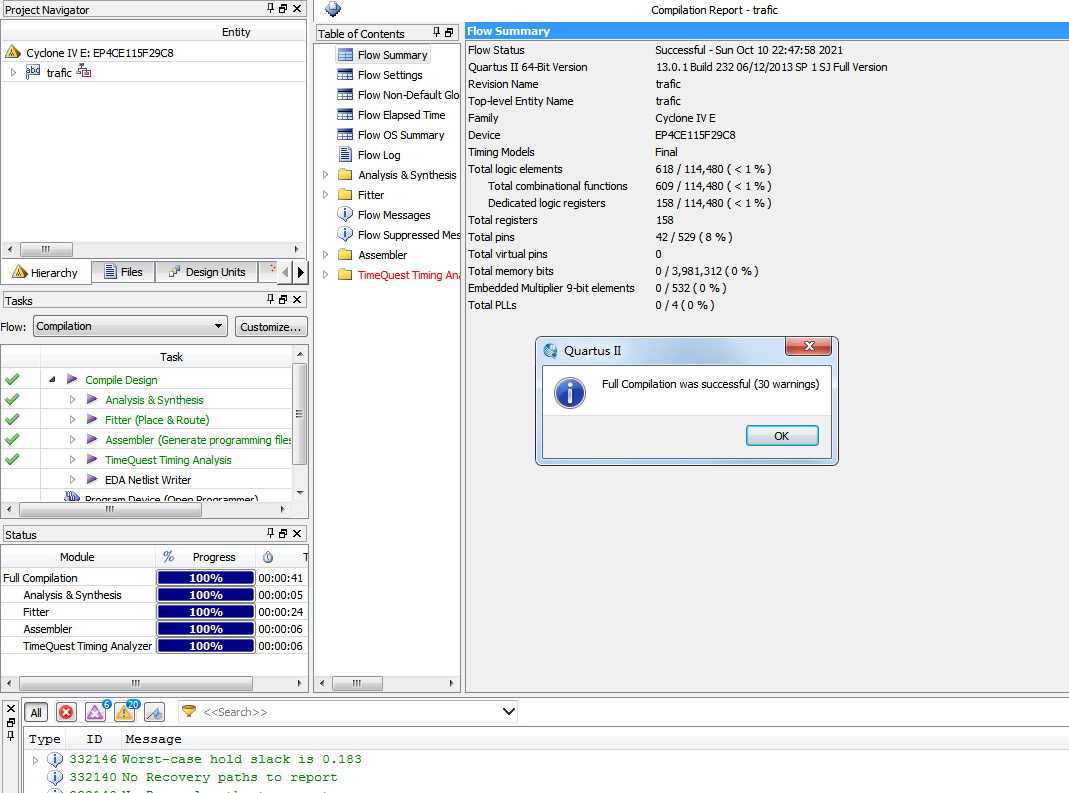

3. 程序编译

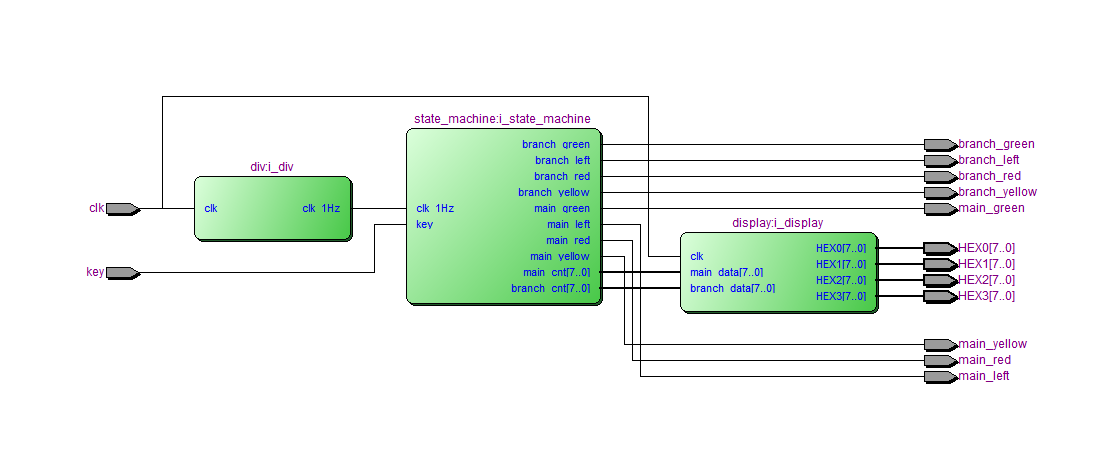

4. RTL图

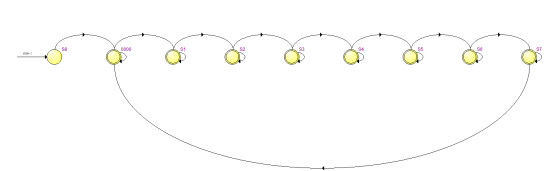

状态图

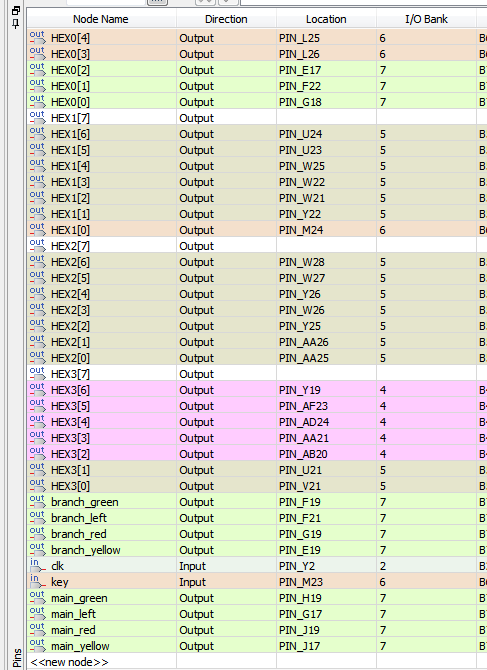

5. 管脚分配

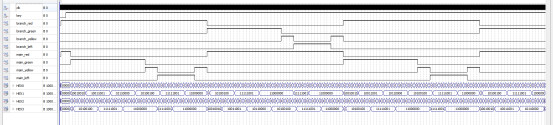

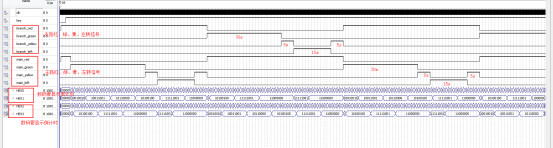

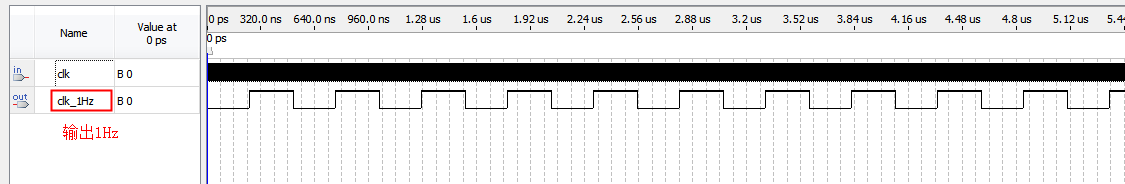

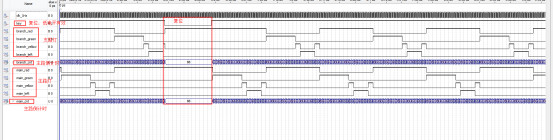

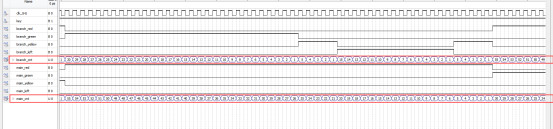

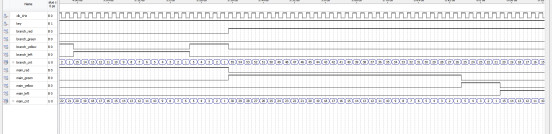

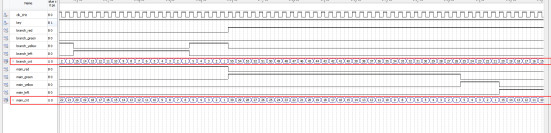

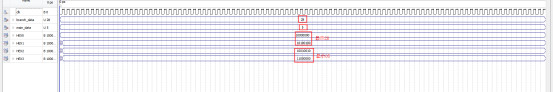

6. 仿真图

整体仿真图

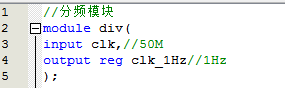

分频模块

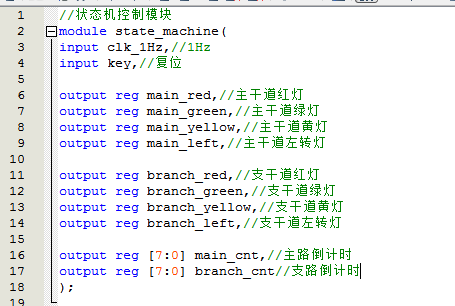

状态机控制模块

显示模块

部分代码展示:

//交通灯 module trafic( input clk,//50M input key,//复位 output main_red,//主干道红灯 output main_green,//主干道绿灯 output main_yellow,//主干道黄灯 output main_left,//主干道左转灯 output branch_red,//支干道红灯 output branch_green,//支干道绿灯 output branch_yellow,//支干道黄灯 output branch_left,//支干道左转灯 output [7:0] HEX0,//数码管0 output [7:0] HEX1,//数码管1 output [7:0] HEX2,//数码管2 output [7:0] HEX3//数码管3 ); wire clk_1Hz; wire [7:0] main_cnt; wire [7:0] branch_cnt; //分频模块 div i_div( . clk(clk),//时钟 . clk_1Hz(clk_1Hz)//1Hz ); //状态机控制模块 state_machine i_state_machine( . clk_1Hz(clk_1Hz),//1Hz . key(key), . main_red(main_red), . main_green(main_green), . main_yellow(main_yellow), . main_left(main_left), . branch_red(branch_red), . branch_green(branch_green), . branch_yellow(branch_yellow), . branch_left(branch_left), . main_cnt(main_cnt), . branch_cnt(branch_cnt) );

源代码

扫描文章末尾的公众号二维码

1401

1401

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?