名称:mealy型状态机设计Verilog代码Quartus 开发板 (文末获取)

软件:Quartus

语言:Verilog

代码功能:

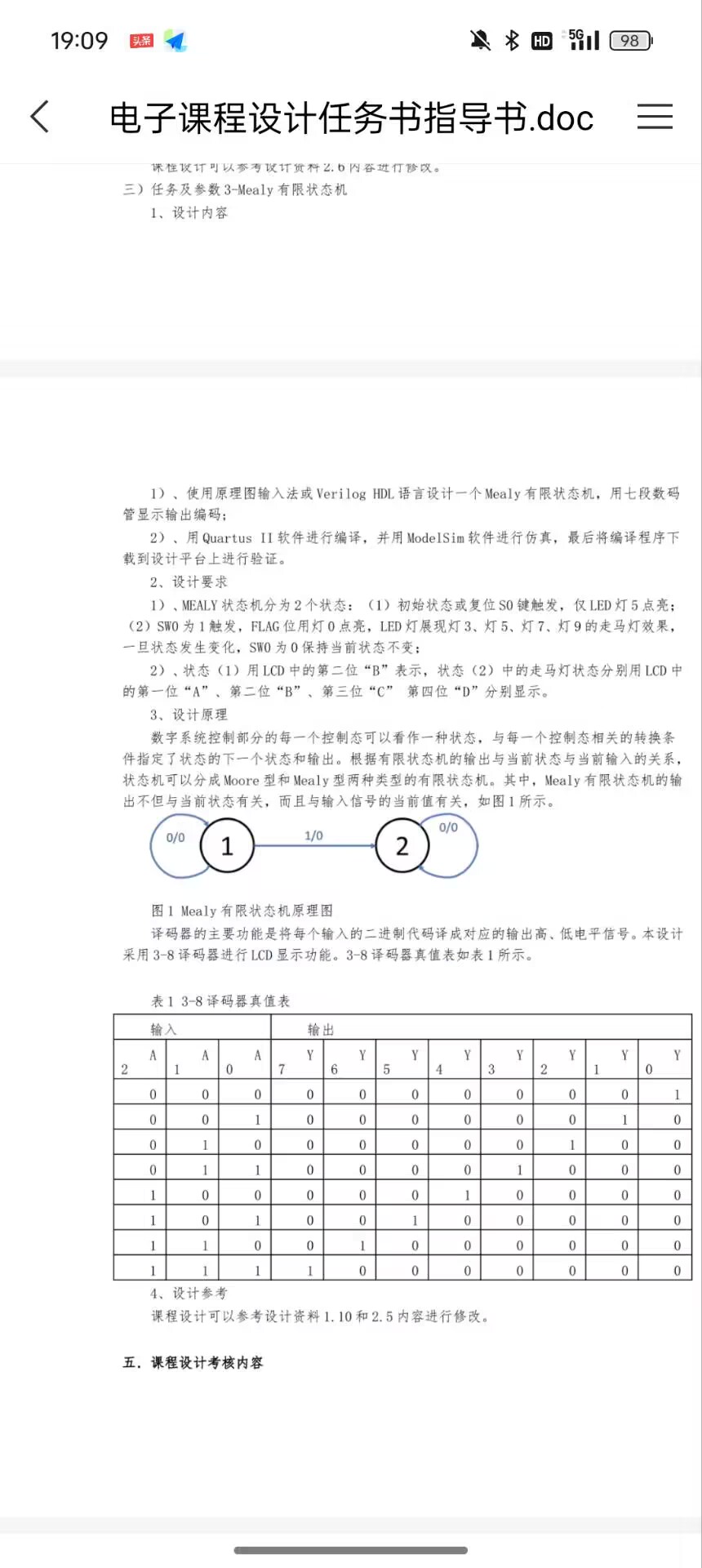

l)、使用原理图输入法或 Verilog HDI语言设计一个 Mealy有限状态机,用七段数码管显示输出编码;

2)、用 Quartus II软件进行编译,并用 Mode lsim软件进行仿真,最后将编译程序下载到设计平台上进行验证。

2、设计要求

1)、 MEALY状态机分为2个状态:(1)初始状态或复位SO键触发,仅LED灯5点亮

(2)SW0为1触发,FLAG位用灯0点亮,LED灯展现灯3、灯5、灯7、灯9的走马灯效果,

旦状态发生变化,SW0为0保持当前状态不变

2)、状态(1)用LCD中的第二位“B”表示,状态(2)中的走马灯状态分别用LCD中

的第一位“A”、第二位“B”、第三位“C”第四位“D”分别显示。

3、设计原理

数字系统控制部分的每一个控制态可以看作一种状态,与每一个控制态相关的转换条件指定了状态的下一个状态和输出。根据有限状态机的输出与当前状态与当前输入的关系,状态机可以分成 Moore型和 Mealy型两种类型的有限状态机。其中, Mealy有限状态机的输出不但与当前状态有关,而且与输入信号的当前值有关,如图1所示。

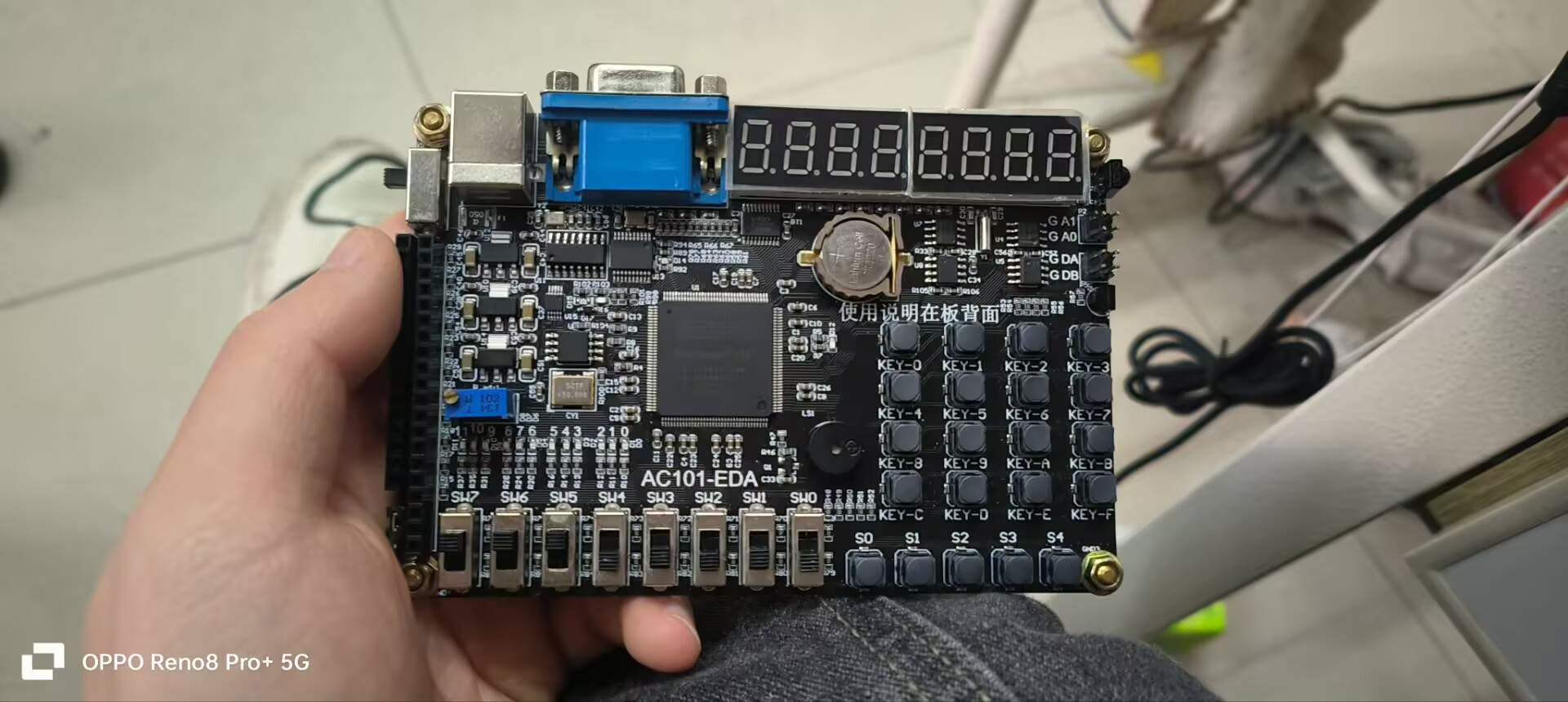

本代码已在开发板验证,开发板如下,其他开发板可以修改管脚适配:

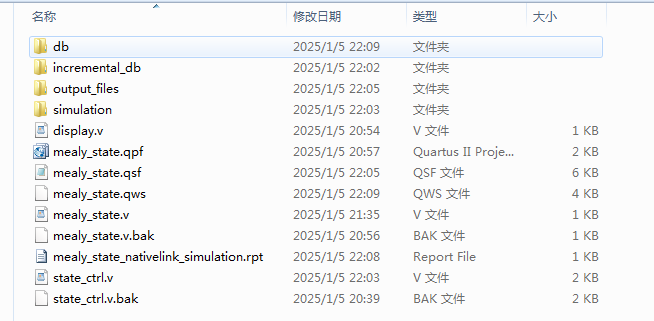

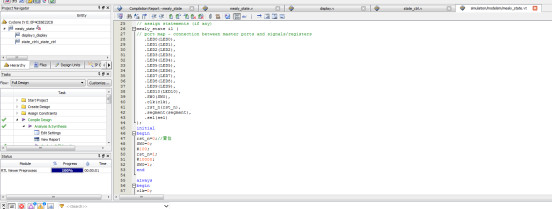

1、工程文件

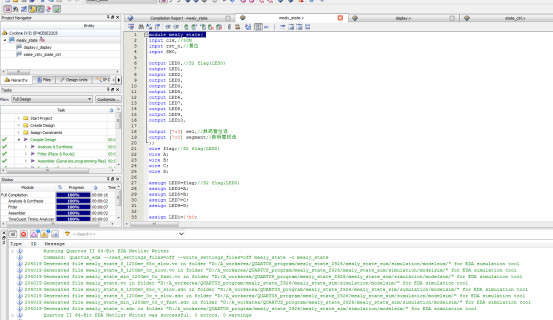

2、程序文件

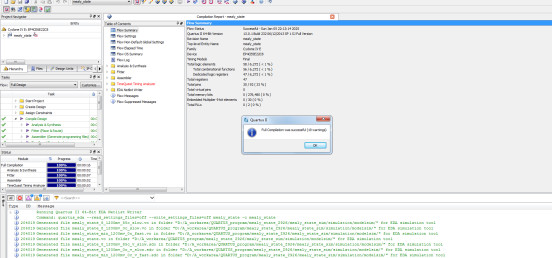

3、程序编译

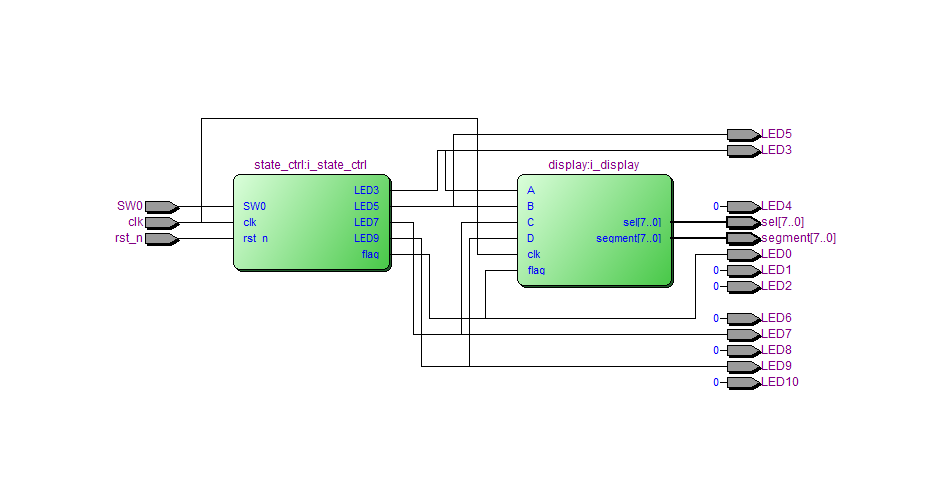

4、RTL图

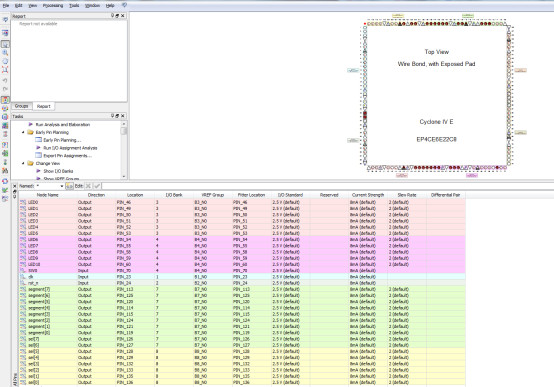

5、管脚分配

6、Testbench

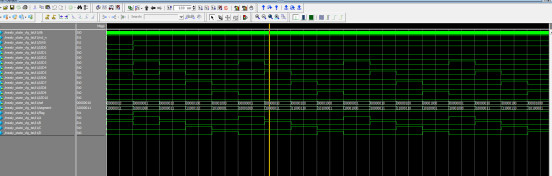

7、仿真图

整体仿真图

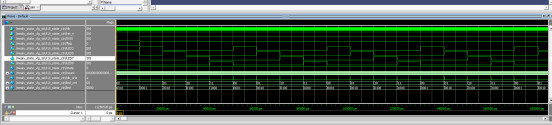

状态控制模块

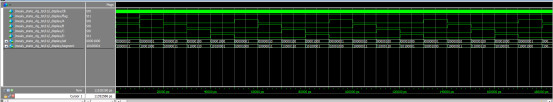

数码管显示模块

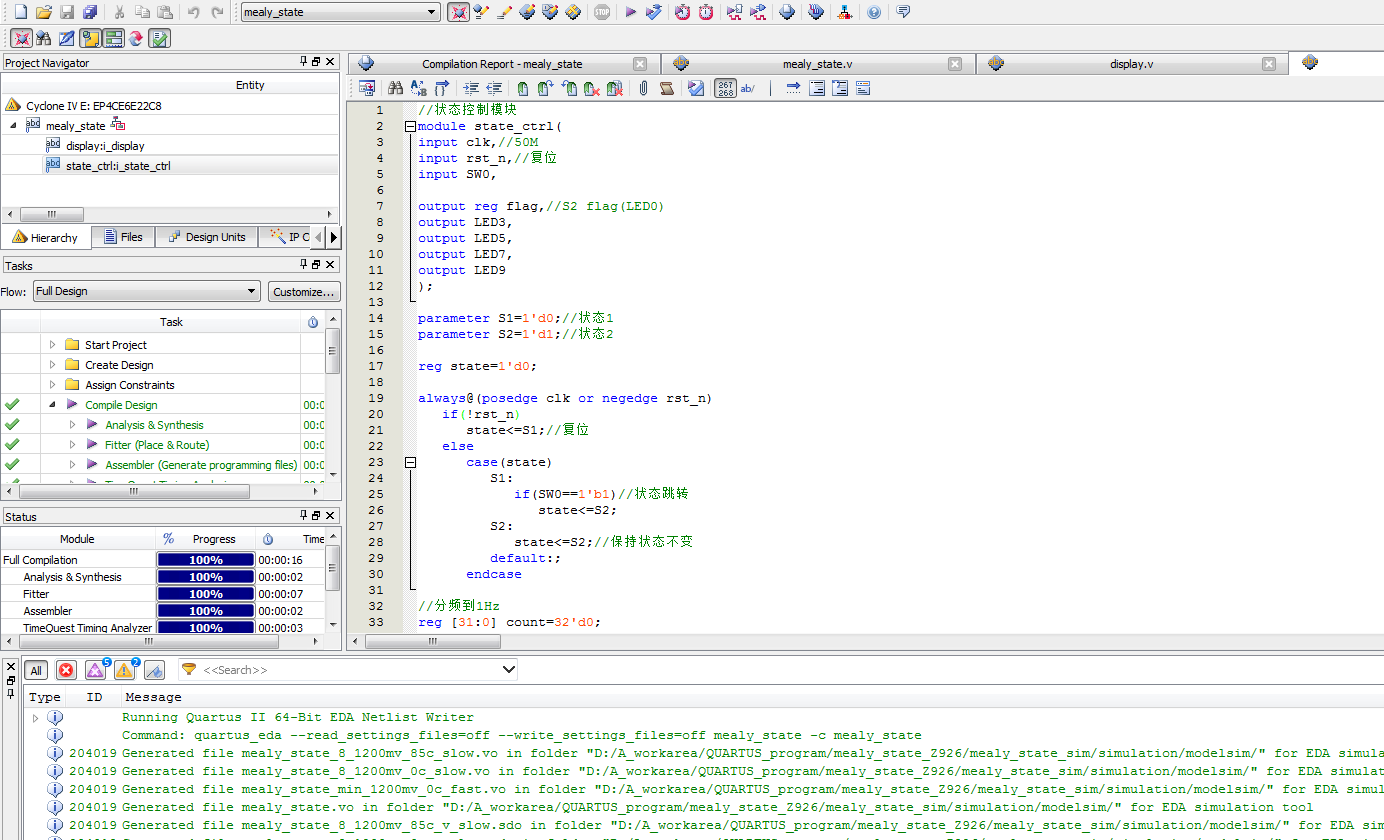

部分代码展示:

module mealy_state( input clk,//50M input rst_n,//复位 input SW0, output LED0,//S2 flag(LED0) output LED1, output LED2, output LED3, output LED4, output LED5, output LED6, output LED7, output LED8, output LED9, output LED10, output [7:0] sel,//数码管位选 output [7:0] segment//数码管段选 ); wire flag;//S2 flag(LED0) wire A; wire B; wire C; wire D; assign LED0=flag;//S2 flag(LED0) assign LED3=A; assign LED5=B; assign LED7=C; assign LED9=D; assign LED1=1'b0; assign LED2=1'b0; assign LED4=1'b0; assign LED6=1'b0; assign LED8=1'b0; assign LED10=1'b0;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?