名称:FFT计算信号频谱设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

FFT计算信号频谱

将模拟信号进行AD采样后,通过FFT变换计算信号频谱

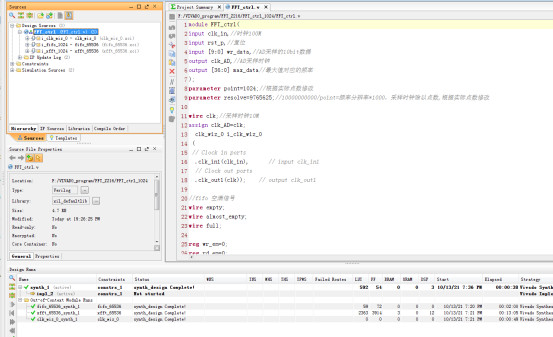

1. 工程文件

2. 程序文件

1024点

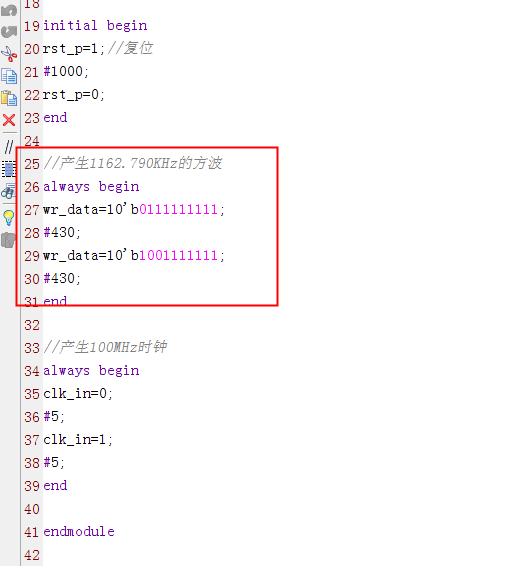

3. Testbench

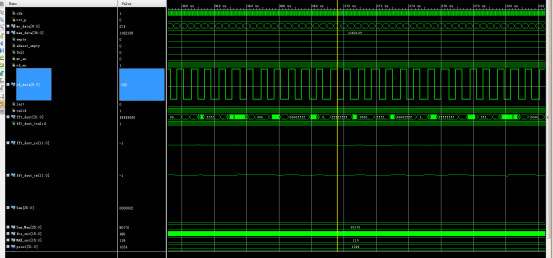

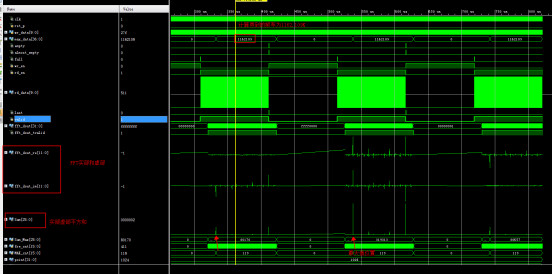

4. 仿真图

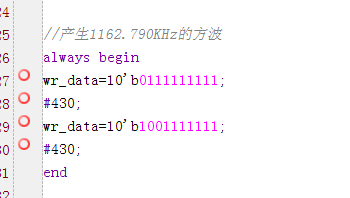

部分代码展示:

module FFT_ctrl( input clk_in,//时钟100M input rst_p,//复位 input [9:0] wr_data,//AD采样的10bit数据 output clk_AD,//AD采样时钟 output [36:0] max_data//最大值对应的频率 ); parameter point=1024;//根据实际点数修改 parameter resolve=9765625;//10000000000/point=频率分辨率*1000,采样时钟除以点数,根据实际点数修改 wire clk;//采样时钟10M assign clk_AD=clk; clk_wiz_0 i_clk_wiz_0 ( // Clock in ports .clk_in1(clk_in), // input clk_in1 // Clock out ports .clk_out1(clk)); // output clk_out1 //fifo 空满信号 wire empty; wire almost_empty; wire full; reg wr_en=0; reg rd_en=0; wire [9:0] rd_data; wire last; reg valid=0; wire [31:0] fft_dout; wire fft_dout_tvalid; wire signed [11:0] fft_dout_re; wire signed [11:0] fft_dout_im; //控制FIFO写使能 always@(posedge clk or posedge rst_p) if(rst_p) wr_en<=0; else if(empty==1) wr_en<=1; else if(full==1) wr_en<=0; //控制FIFO读使能 always@(posedge clk or posedge rst_p) if(rst_p) rd_en<=0; else if(full==1 && fft_dout_tvalid==0) rd_en<=1; else if(almost_empty==1) rd_en<=0; //产生FFT数据使能信号 always@(posedge clk or posedge rst_p) if(rst_p) valid<=0; else if(rd_en==1) valid<=1;//相对rd_en延迟一个时钟周期 else valid<=0;

源代码

点击下方的公众号卡片获取

4649

4649

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?