名称:量程自动转换数字式频率计设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

量程自动转换数式频率计设计

设备及软件;装有 Quartus I软件完成设计数字系统的计算机

目的:1.了解系统相关功能电路图与印刷电路图的设计、绘制,并完成相关流程的设计以及硬件描述语言

VHDL程序的编写、设计与综合和调试仿真工作;

2.学会 Quartus软件完成设计系统的设计与综合

3.掌握该数字电路系统的仿真调试,分析系统功能实现的可行性等

任务:1.设计一个3位十进制数字式频率计,其测量范围为1MHZ量程分10kHz,100kHz和1MHz三档(最大读数分别为9.99kHZ999kHZ,999kHz)。被测信号由信号发生器提供

2.要求量程可以根据被测量的大小自动转换,规则如下

)当读数大于999时,频率计处于超量程状态,此时显示器发出溢出指示(最高位显示F,其余各

位不显示数字),下一次测量时,量程自动增大一档

2)读数小于000时,频宰计处于欠量程状态。下次测量时,量程减小一档

3要求实现溢出报警功能。即当读数大于999KHZ时,频率计处于超量程状态,产生一个报警信号

点亮LED灯警报

4显示方式如下

1)用记忆显示方式,即计数过程中不显示数据,待计数过程结束后,显示计数结果,并将此显示结果保持到下一次计数结束。显示时间应不小于1秒

2)小数点位置随量程变更自动移位

提示:1、脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为,f为被测信号的频率,N为计

数器所累计的脉冲个数,T为产生N个脉冲所需的时间。所以,在1秒时间内计数器所记录的结果,就是被

测信号的频率。

2、被测频率信号取自实验箱晶体振荡器输出信号,加到主控门的输入端3、再取品体振荡器的另一标准频率信号,经分频后产生各种时基脉冲时基信号的选择可以控制,即量程可以改变

4、时基信号经控制电路产生闸门信号至主控门,只有在闸门信号采样期间内(时基信号的一个周期)输入信号才通过主控门。

5、fN/T,改变时基信号的周期T,即可得到不同的测频范围

6、当主控门关闭时,计数器停止计数,显示器显示记录结果,此时控制电路输出一个置零信号计数器和所有触发器复位,为新的一次采样做好准备。

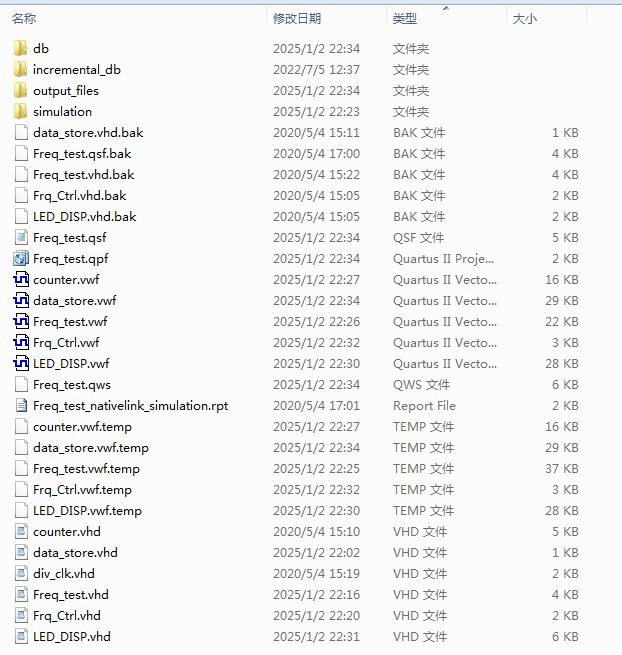

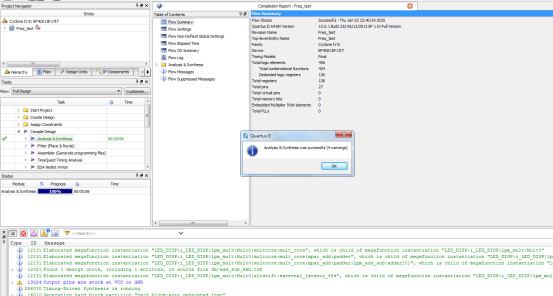

1、工程文件

2、程序文件

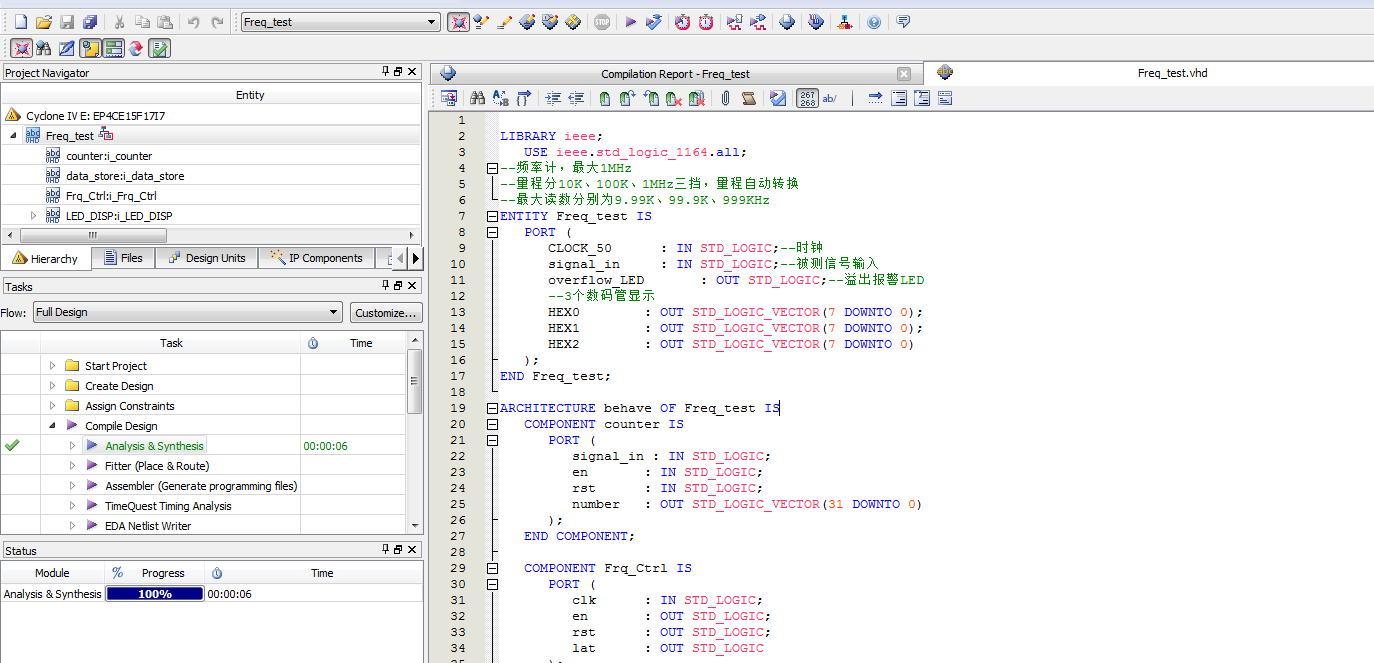

3、程序编译

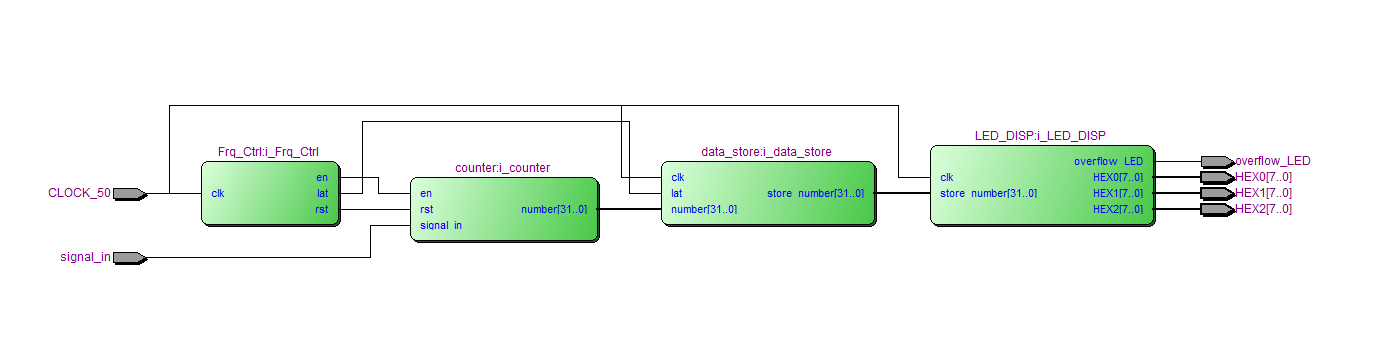

4、RTL图

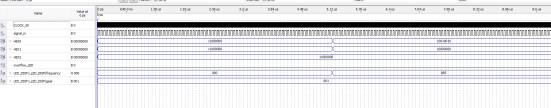

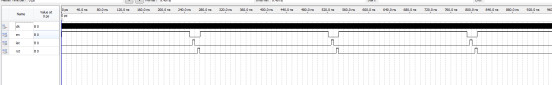

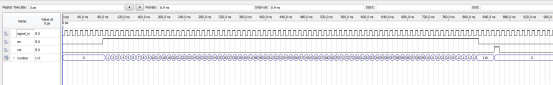

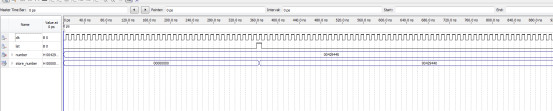

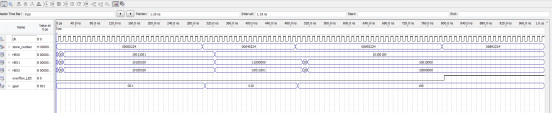

5、仿真图

整体仿真图

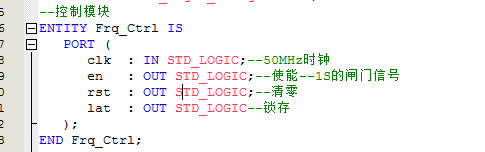

控制模块

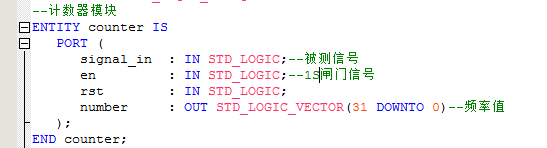

计数器模块

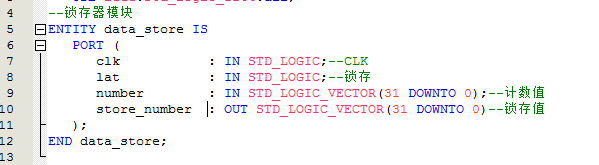

锁存器模块

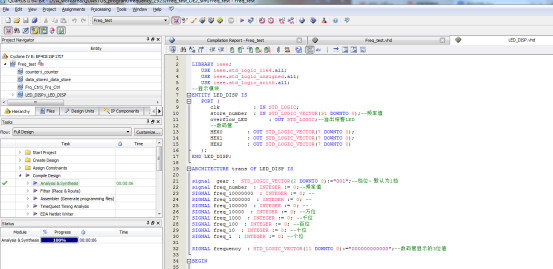

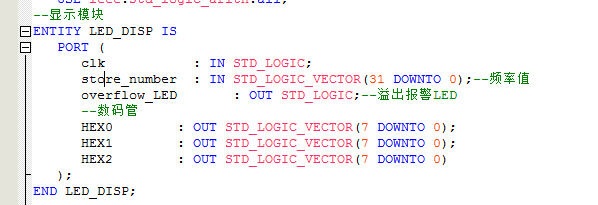

显示模块

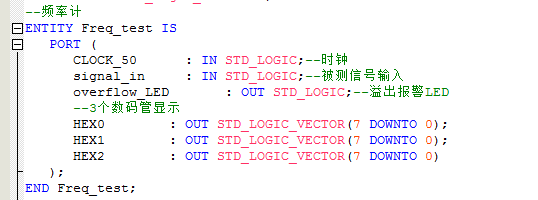

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --频率计 ENTITY Freq_test IS PORT ( CLOCK_50 : IN STD_LOGIC;--时钟 signal_in : IN STD_LOGIC;--被测信号输入 overflow_LED : OUT STD_LOGIC;--溢出报警LED --3个数码管显示 HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END Freq_test; ARCHITECTURE behave OF Freq_test IS COMPONENT counter IS PORT ( signal_in : IN STD_LOGIC; en : IN STD_LOGIC; rst : IN STD_LOGIC; number : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END COMPONENT; COMPONENT Frq_Ctrl IS PORT ( clk : IN STD_LOGIC; en : OUT STD_LOGIC; rst : OUT STD_LOGIC; lat : OUT STD_LOGIC ); END COMPONENT; COMPONENT LED_DISP IS PORT ( clk : IN STD_LOGIC; store_number : IN STD_LOGIC_VECTOR(31 DOWNTO 0);--频率值 overflow_LED : OUT STD_LOGIC;--溢出报警LED --数码管 HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; COMPONENT div_clk IS PORT ( clk_in : IN STD_LOGIC; SW : IN STD_LOGIC_VECTOR(2 DOWNTO 0); clk_out : OUT STD_LOGIC ); END COMPONENT; COMPONENT data_store IS PORT ( clk : IN STD_LOGIC; lat : IN STD_LOGIC; number : IN STD_LOGIC_VECTOR(31 DOWNTO 0); store_number : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); END COMPONENT;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?