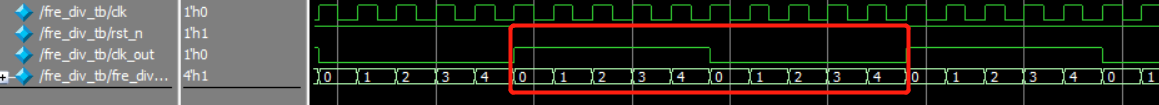

分频代码如下,clk_div传的虽然是4,但其实实现的是2 * (4 + 1) 分频

`timescale 1ns / 1ps

module fre_div (

input clk,

input rst_n,

input[3:0] clk_div,

output reg clk_out

);

reg[3:0] cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

clk_out <= 1'b1;

end

else begin

if(cnt == clk_div) begin

clk_out <= ~clk_out;

end

else begin

clk_out <= clk_out;

end

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt <= 4'd0;

end

else if (cnt == clk_div) begin

cnt <= 4'd0;

end

else begin

cnt <= cnt + 4'd1;

end

end

endmodule

`timescale 1ns / 1ps

module fre_div_tb();

reg clk;

reg rst_n;

wire clk_out;

always #10 clk = ~clk;

initial begin

clk = 0;

rst_n = 0;

#100;

rst_n = 1;

end

fre_div fre_div_m0 (

.clk(clk),

.rst_n(rst_n),

.clk_div(4'd4),

.clk_out(clk_out)

);

endmodule

390

390

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?