Cortex-A510——IOMMU

小狼@http://blog.csdn.net/xiaolangyangyang

1、IOMMU的作用

- DMA

- 虚拟化(stage2)

- 硬件加速器访问的内存隔离

- 访问非连续的地址

- 32位转换成64位

- 限制Master的访问空间

- 用户态驱动

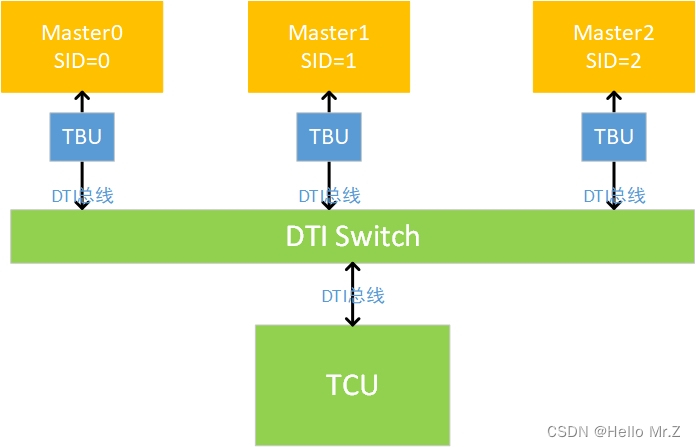

2、IOMMU系统结构

3、STE、CD和页表

STE、CD和页表都保存在内存里;

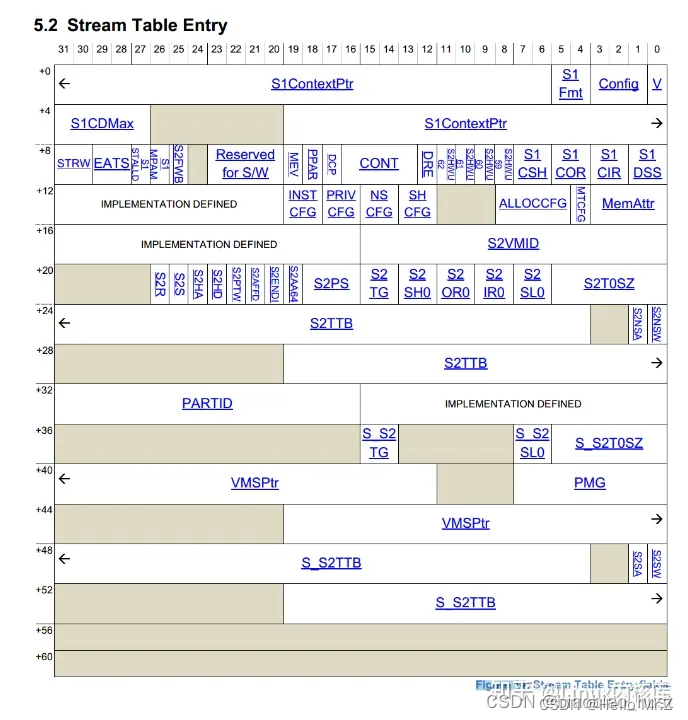

STE每个大小512btye,有多少SID就有多少个STE,线性排列;

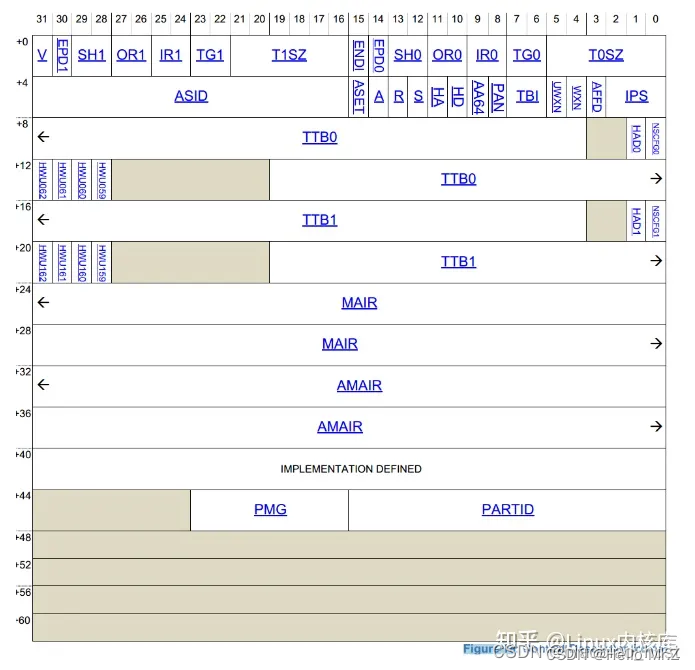

每个STE指向一个CD,CD大小为512btye。

根据SID查找页表过程

STE表

CD表

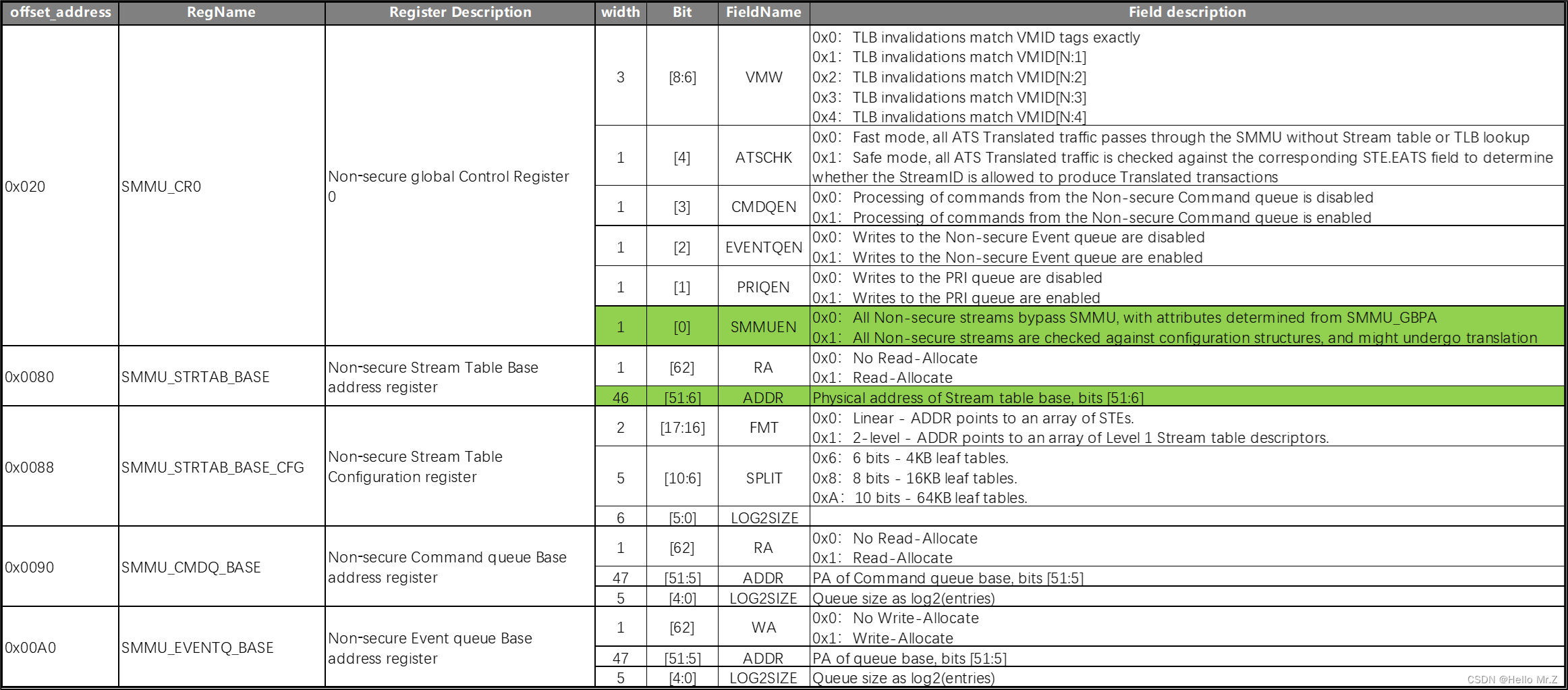

4、主要寄存器

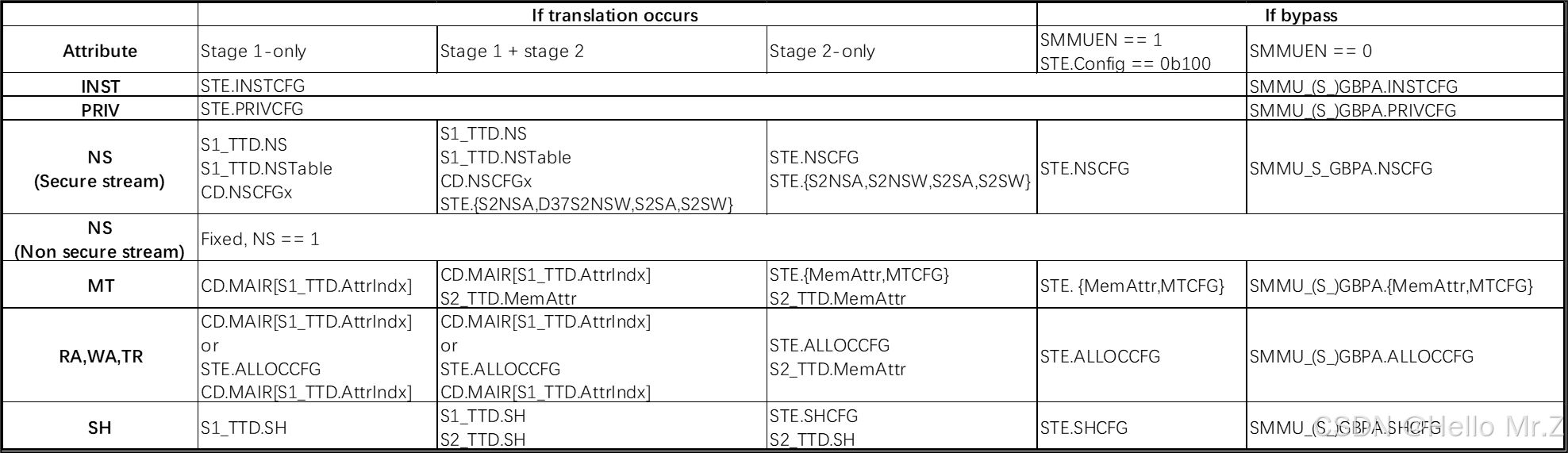

5、The attributes output from the SMMU

6、CMD和EVENT

系统软件通过Command Queue和Event Queue来和SMMU打交道,这2个Queue都是循环队列

Command queue:用于软件与SMMU的硬件交互,软件写命令到command queue, SMMU从command queue中读取命令处理;

Event Queue:用于SMMU发生软件配置错误的状态信息记录,SMMU将配置错误信息写到Event queue中,软件通过读取Event queue获得配置错误信息并进行配置错误处理。

可以使用CMD_CFGI_STE、CMD_CFGI_STE_RANGE、CMD_CFGI_CD、CMD_CFGI_CD_ALL命令对STE、CD进行valid;

可以使用CMD_TLBI_NH_ALL、CMD_TLBI_NH_ASID、CMD_TLBI_NH_VA、CMD_TLBI_NH_VAA、CMD_TLBI_EL3_ALL、CMD_TLBI_EL3_VA、CMD_TLBI_EL2_ALL、CMD_TLBI_EL2_ASID、CMD_TLBI_EL2_VA、CMD_TLBI_EL2_VAA、CMD_TLBI_S12_VMALL、CMD_TLBI_S2_IPA、CMD_TLBI_NSNH_ALL、CMD_ATC_INV、CMD_PRI_RESP、CMD_RESUME、CMD_STALL_TERM、CMD_SYNC、CMD_TLBI_S_EL2_ALL、CMD_TLBI_S_EL2_ASID、CMD_TLBI_S_EL2_VA、CMD_TLBI_S_EL2_VAA、CMD_TLBI_S_S12_VMALL、CMD_TLBI_S_S2_IPA、CMD_TLBI_SNH_ALL命令操作TLB。

6、切换到SLC通路

SMMU_GBPA.SHCFG = Outer Shareable

SMMU_GBPA.ALLOCCFG = Read Allocate | Write Allocate

SMMU_GBPA.MTCFG = 0x1

SMMU_GBPA.MemAttr = 0xf

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?