写得有点混乱,但大致是对的

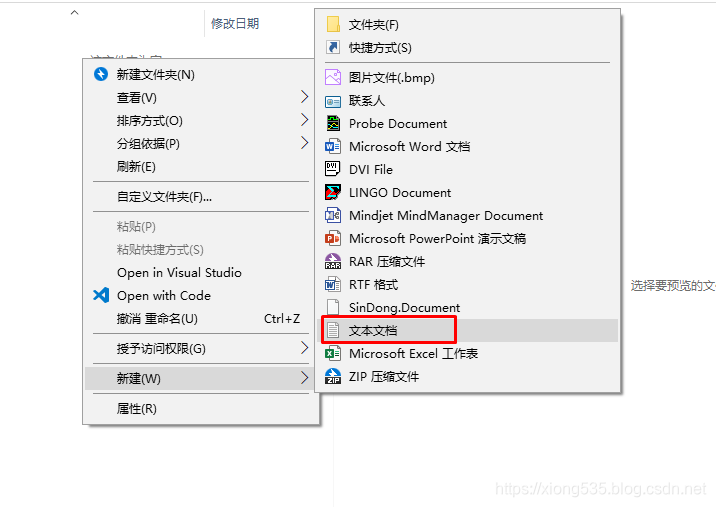

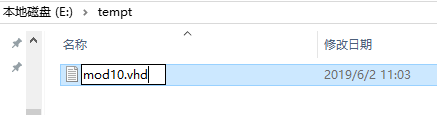

- 新建一个文件夹,名字任意 (不要有中文,以英文开头)

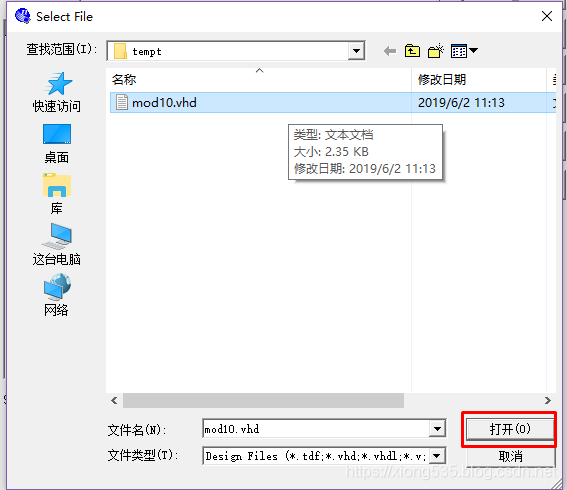

- 在文件夹里放v/vhd文件

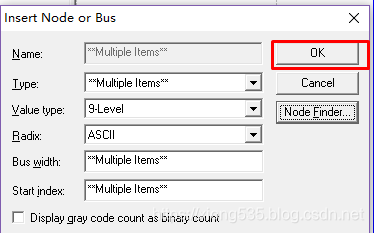

⚠点确定

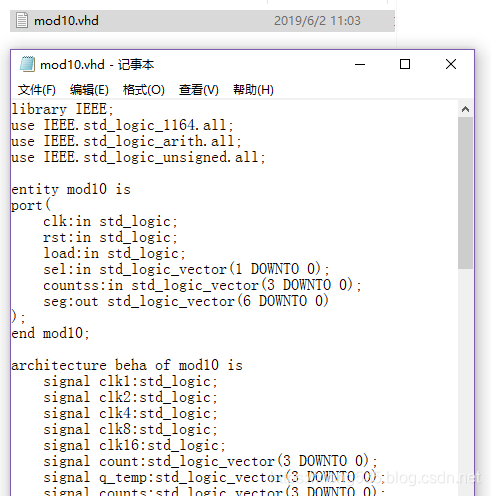

- 程序复制进去,保存关闭

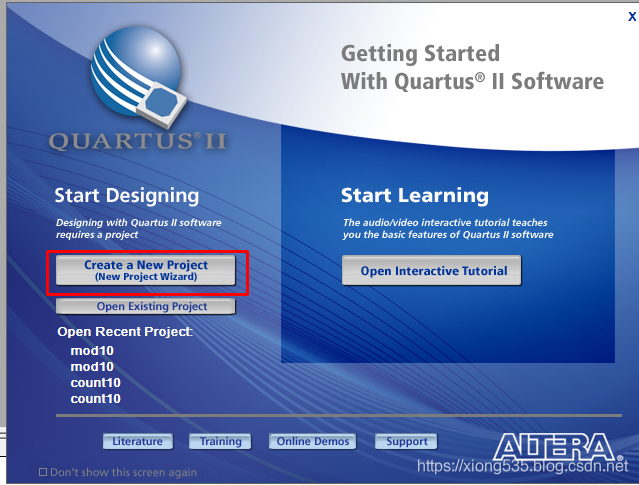

- Quartus,启动

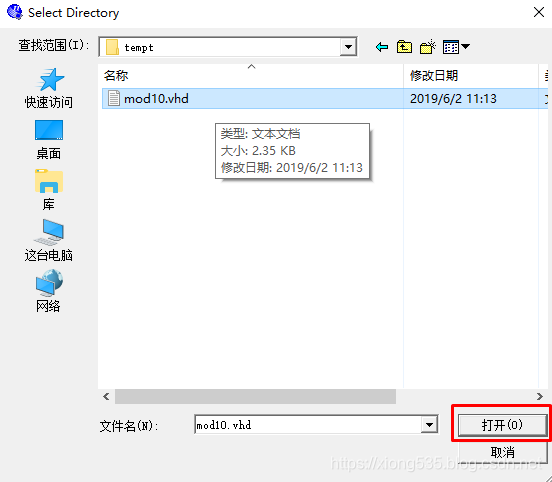

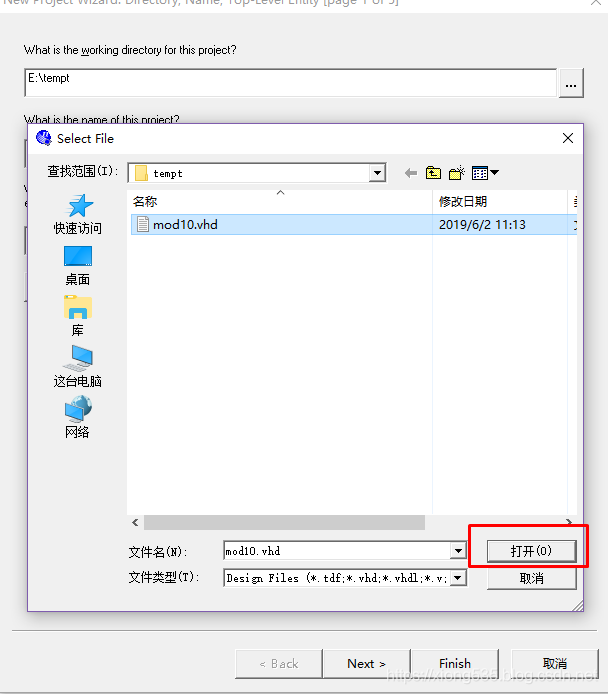

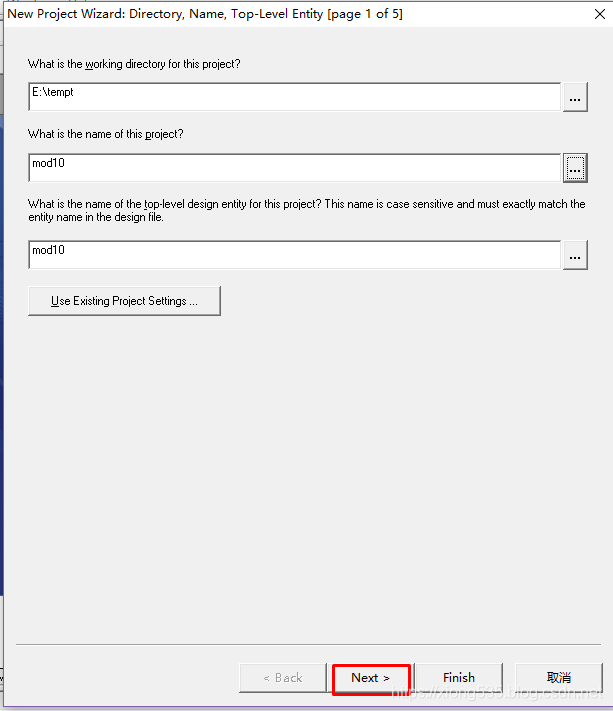

- 找你刚才创建的文件夹

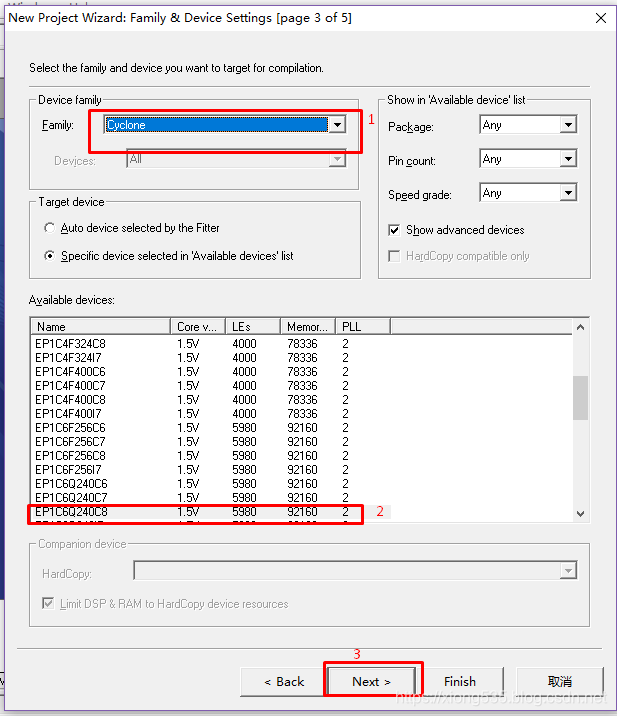

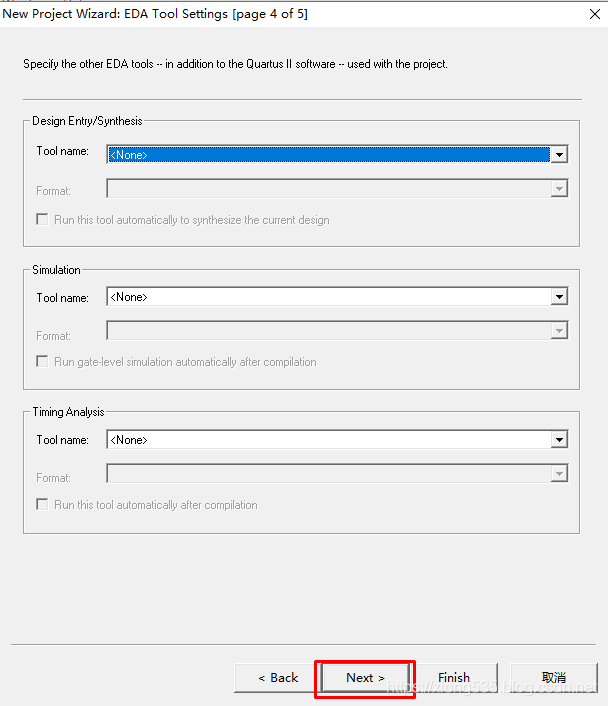

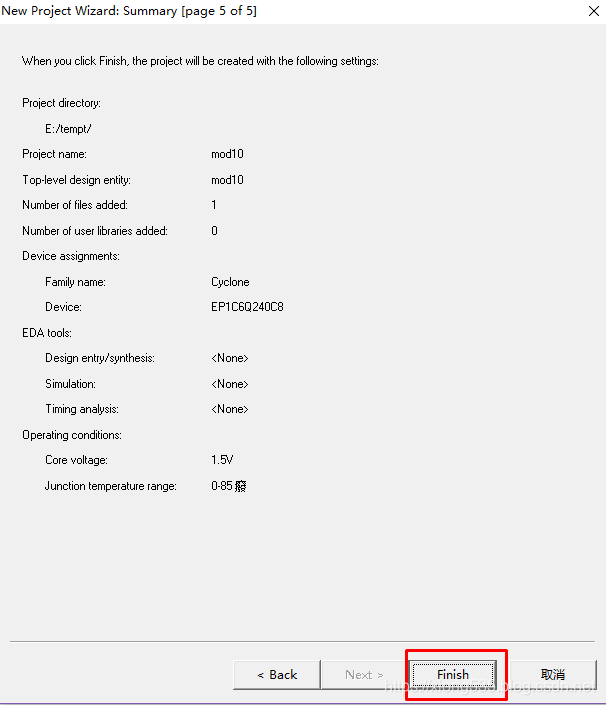

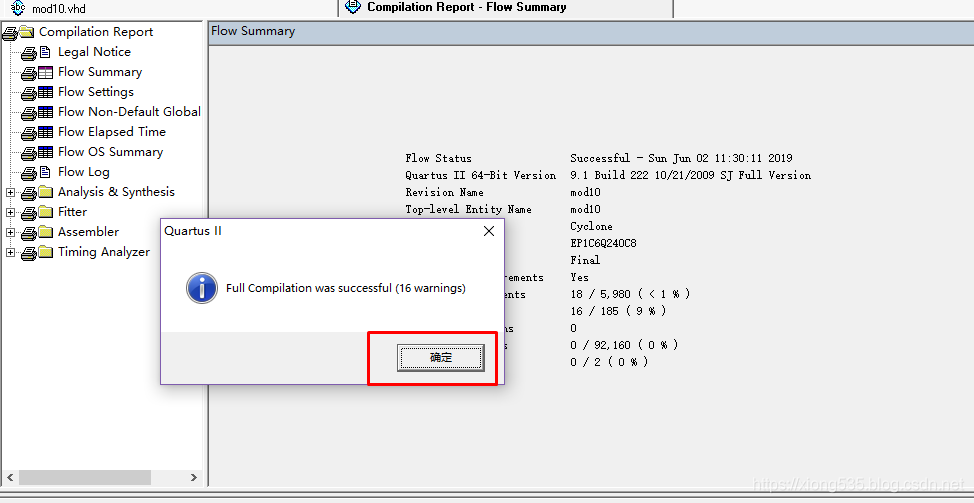

怕同学们看不清,我把型号写一下(我也是看百度文库里的,Cyclone-EP1C6Q240C8,感觉这个无所谓┑( ̄Д  ̄)┍

- 第一步大功告成

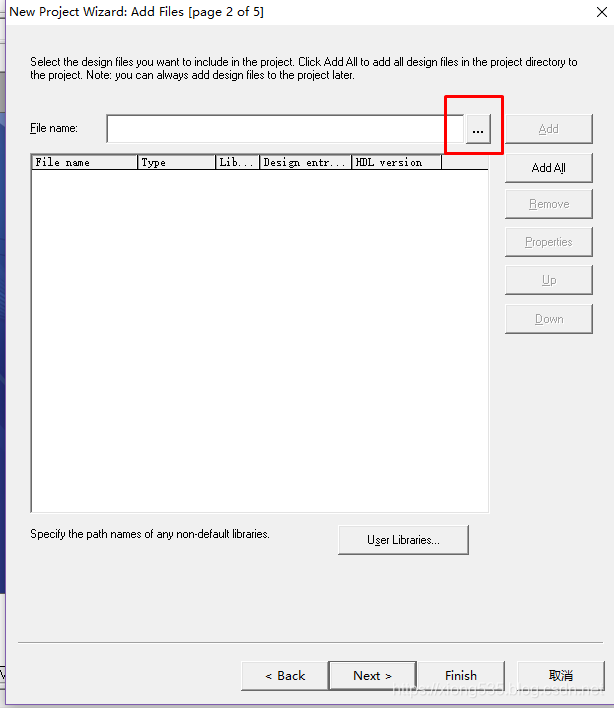

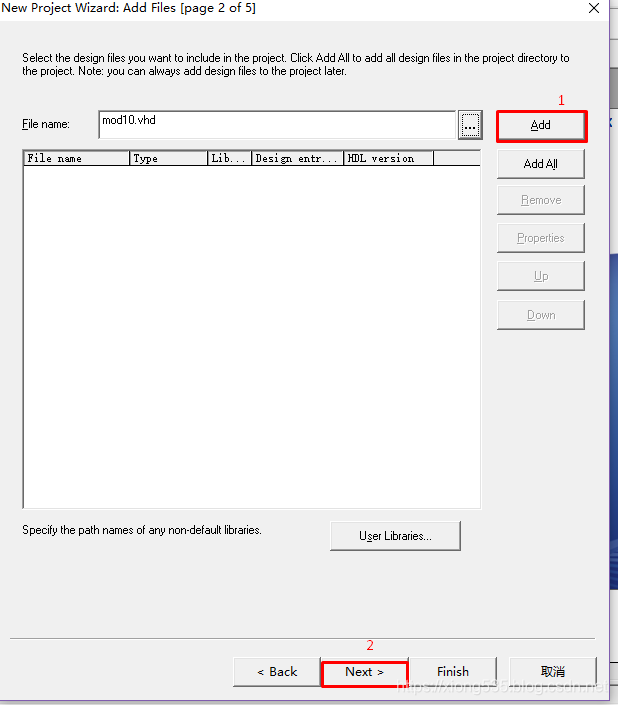

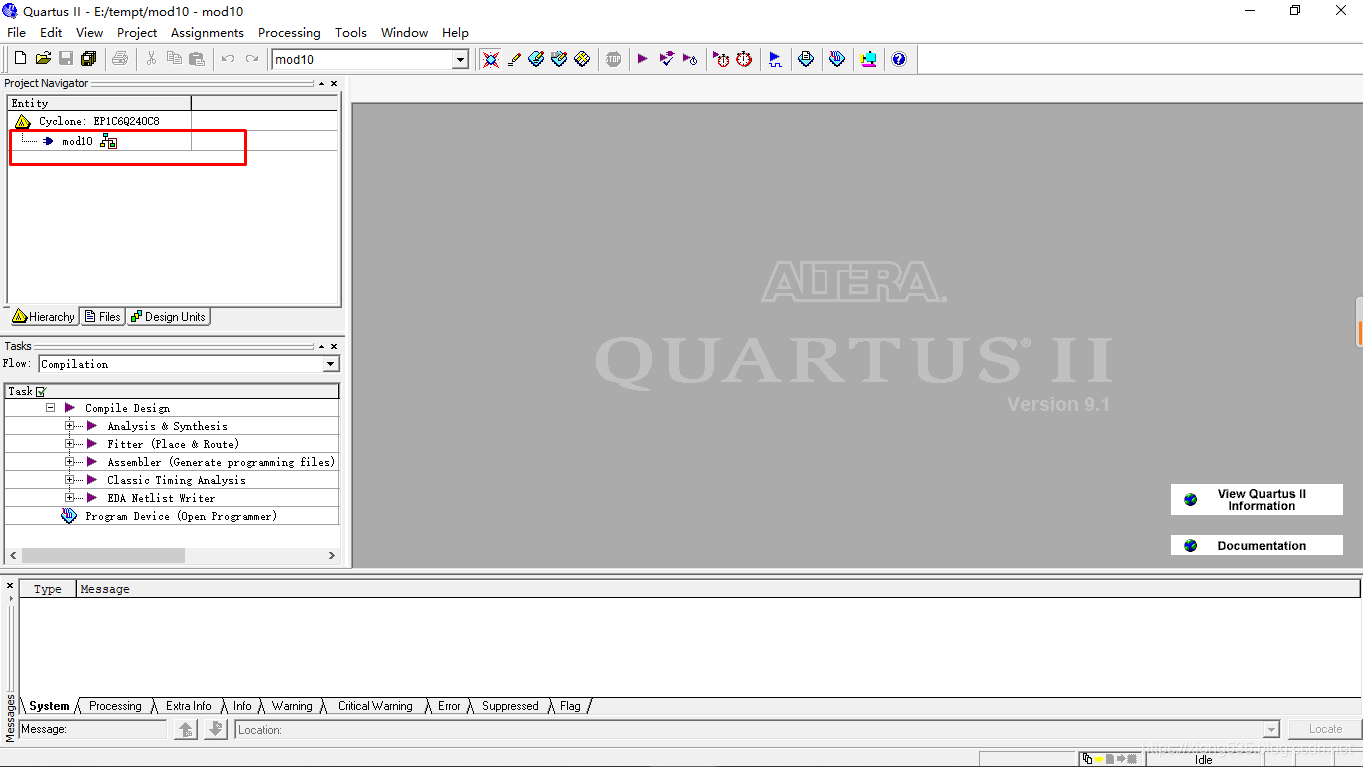

- 双击这里,弹出文件

我是怎么反应过来我文件类型错了,就是看见这里里面库的类型和变量都没有高亮。。。

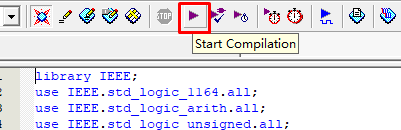

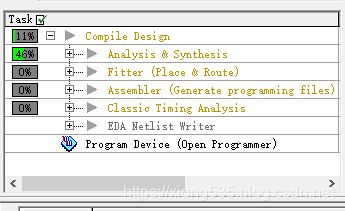

- 开始编译,warnnings可以不用管,出错就看是哪一行继续调试

第一次调试会有点慢

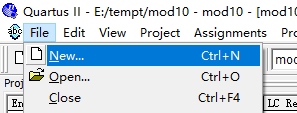

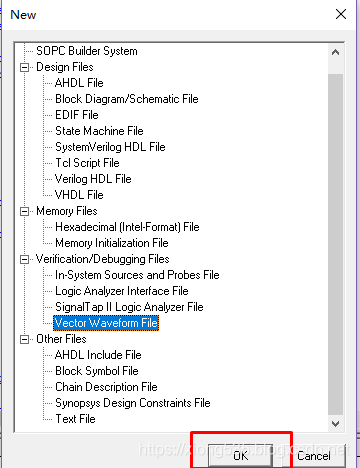

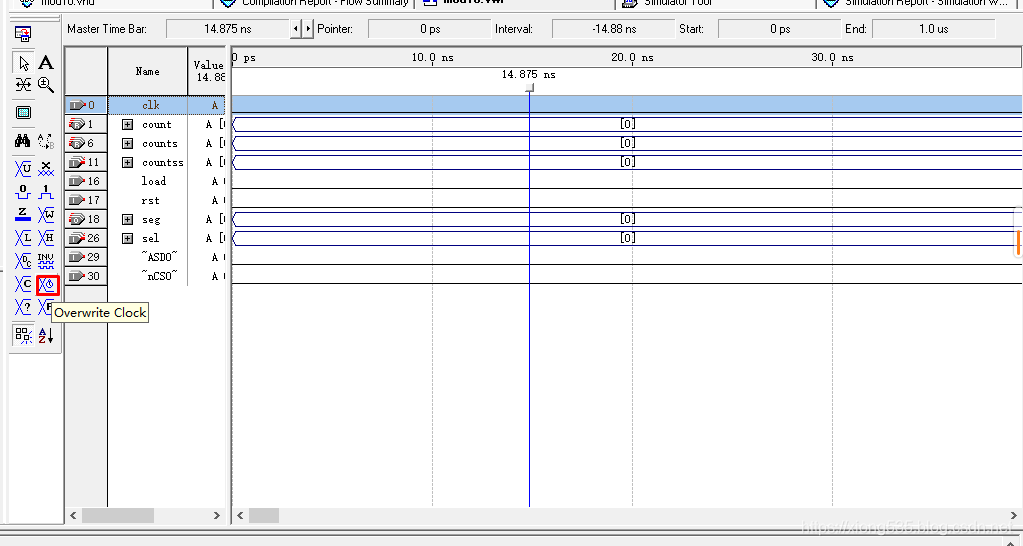

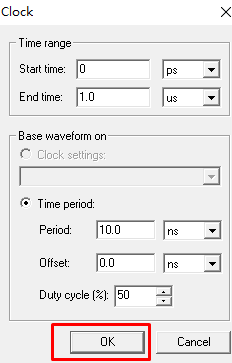

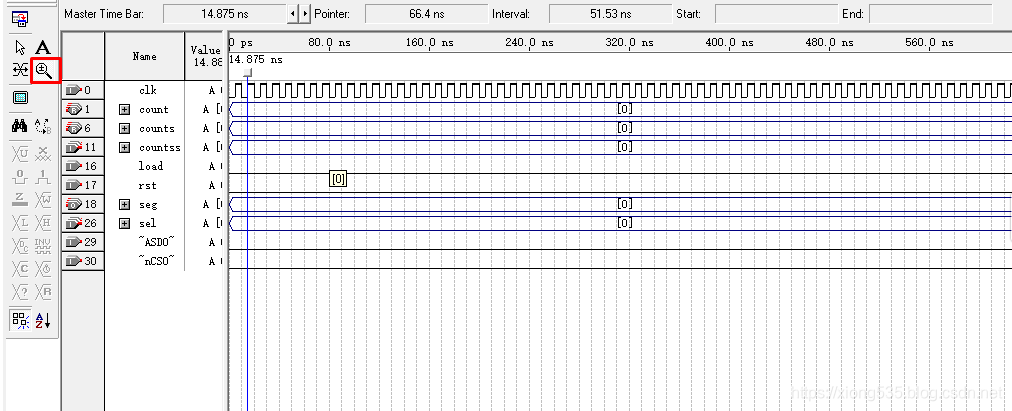

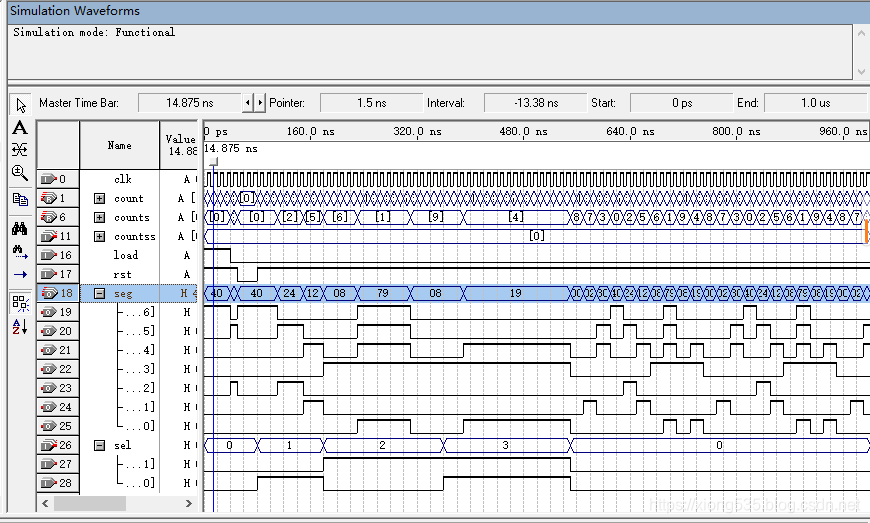

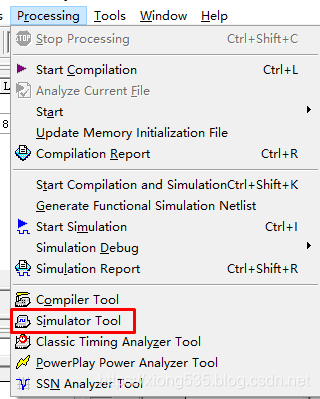

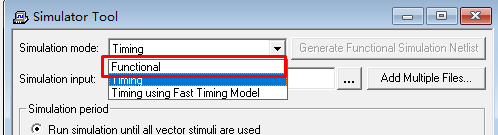

- 跑波形仿真

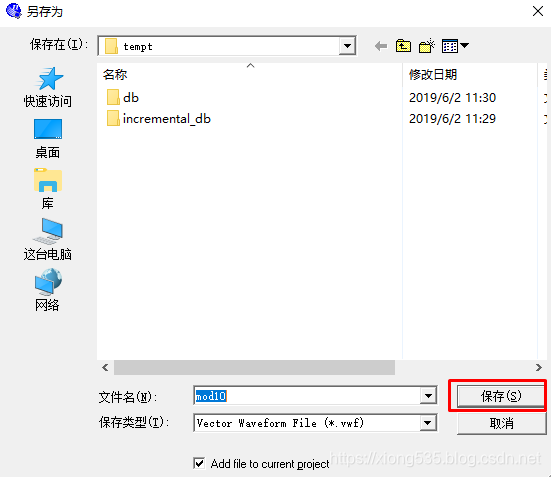

- 保存同名文件

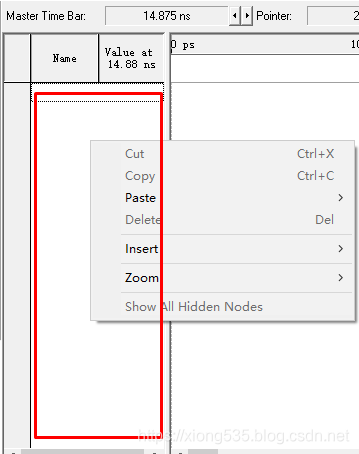

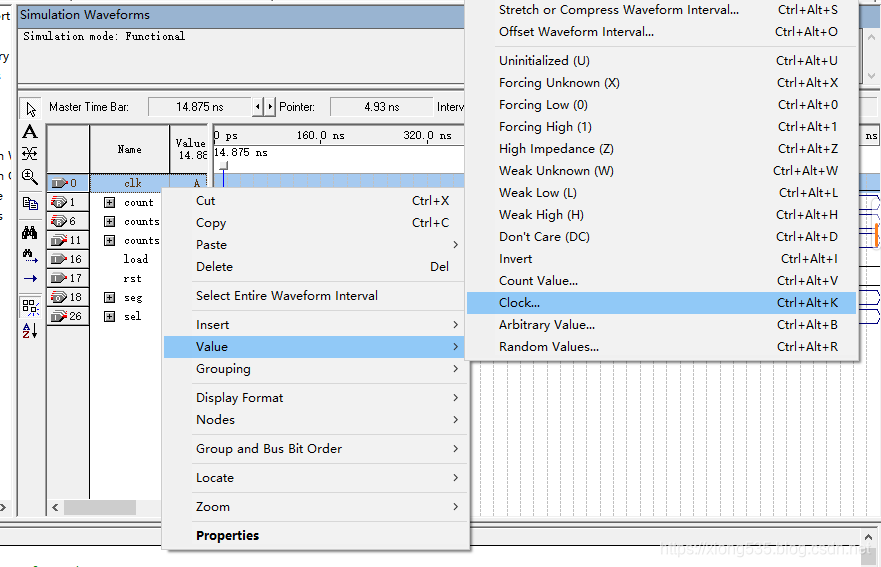

- 在这块区域点鼠标右键

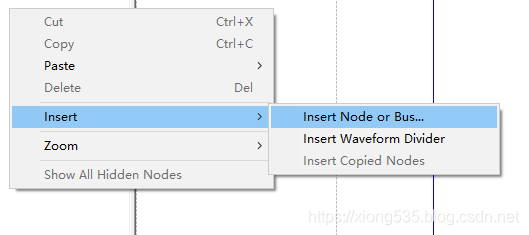

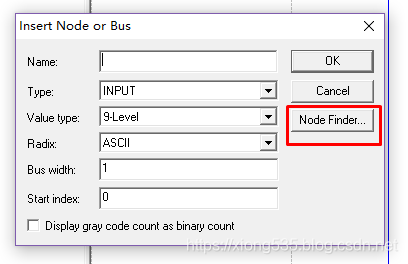

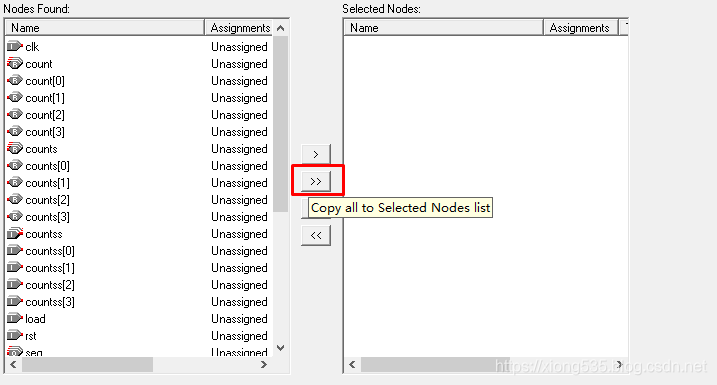

- 选择节点

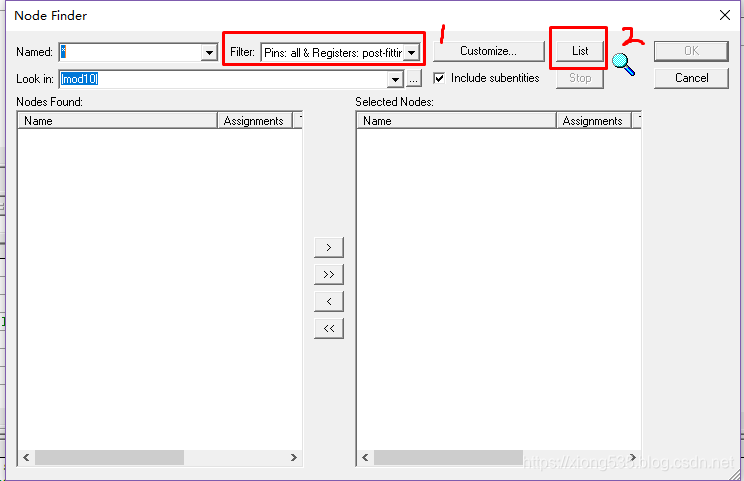

如果你是第一次做,Filter这里选Pins,一定得注意

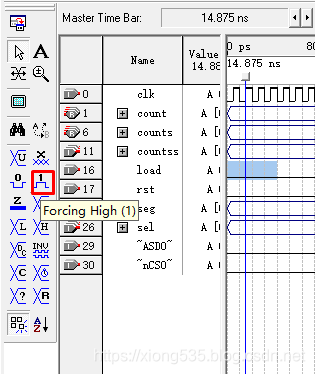

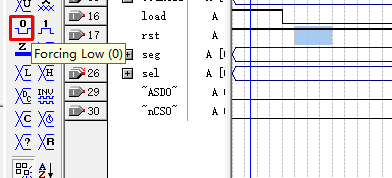

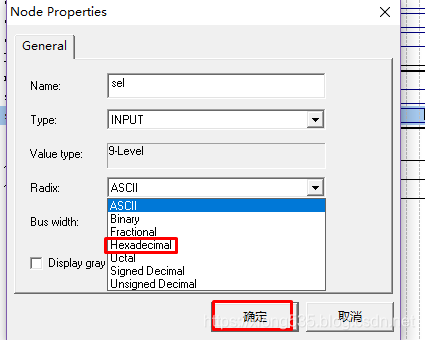

- 还可以改properties,H-16进制

啥值也不改

- 更改大小,鼠标右键缩小

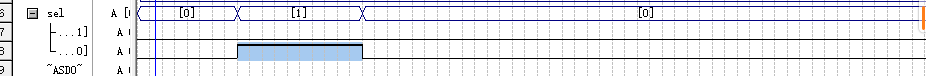

- 根据定义,clk为系统时钟,load为置位信号(高有效),rst为复位(清零)信号(低有效),sel为频率选择信号,countss为置位信号,seg为七段译码器输出,counts为状态信号输出。

- 以下为测试,load拉高一段

- 清零信号全部拉高后拉低一段

- 更改选择信号

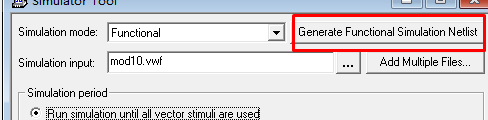

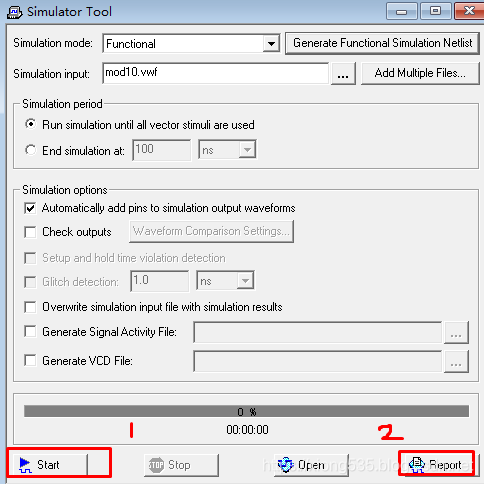

- 重新生成表单,开始仿真

部分步骤可以继续优化

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity mod10 is

port(

clk:in std_logic;

rst:in std_logic;

load:in std_logic;

sel:in std_logic_vector(1 DOWNTO 0);

countss:in std_logic_vector(3 DOWNTO 0);

seg:out std_logic_vector(6 DOWNTO 0)

);

end mod10;

architecture beha of mod10 is

signal clk1:std_logic;

signal clk2:std_logic;

signal clk4:std_logic;

signal clk8:std_logic;

signal clk16:std_logic;

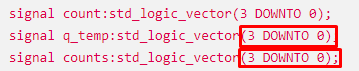

signal count:std_logic_vector(3 DOWNTO 0);

signal q_temp:std_logic_vector(3 DOWNTO 0);

signal counts:std_logic_vector(3 DOWNTO 0);

begin

process(clk,rst)

begin

if(rst = '0')

then count <= "0000";

elsif(clk'event and clk = '0') then

count <= count + 1;

end if;

clk2 <= count(0);

clk4 <= count(1);

clk8 <= count(2);

clk16 <= count(3);

end process;

process(sel)

begin

case sel is

when "00" => clk1 <= clk2;

when "01" => clk1 <= clk4;

when "10" => clk1 <= clk8;

when "11" => clk1 <= clk16;

when others => null;

end case;

end process;

process(clk1,rst,load)

begin

if(rst = '0') then counts <= "0000";

elsif(load = '1') then counts <= countss;

elsif(clk1'event and clk1 = '0') then

case counts is

when "0000" => counts <= "0010";

when "0010" => counts <= "0101";

when "0101" => counts <= "0110";

when "0110" => counts <= "0001";

when "0001" => counts <= "1001";

when "1001" => counts <= "0100";

when "0100" => counts <= "1000";

when "1000" => counts <= "0111";

when "0111" => counts <= "0011";

when "0011" => counts <= "0000";

when others => counts <= "0000";

end case;

end if;

q_temp <= counts;

end process;

process(q_temp)

begin

case q_temp is

when "0000" => seg <= "1000000";

when "0001" => seg <= "1111001";

when "0010" => seg <= "0100100";

when "0011" => seg <= "0110000";

when "0100" => seg <= "0011001";

when "0101" => seg <= "0010010";

when "0111" => seg <= "0000010";

when "1000" => seg <= "0000000";

when "1001" => seg <= "0001000";

when others => seg <= "0001000";

end case;

end process;

end beha;

几个小坑,这百度文库里的程序不能用v文件而得建立vhd文件,别说我菜,这才第二节实验课。。。有Bug都是我当场一点点调试出来的。。。

这也必须全都写好定义,我偷懒一下没写,就GG了,变量名还是这样规范全部列出比较好,你列了一行最后会忘了自己定义了啥子玩意

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?