1. on-chip and off-chip

2. L1 and L2

3. terminology:

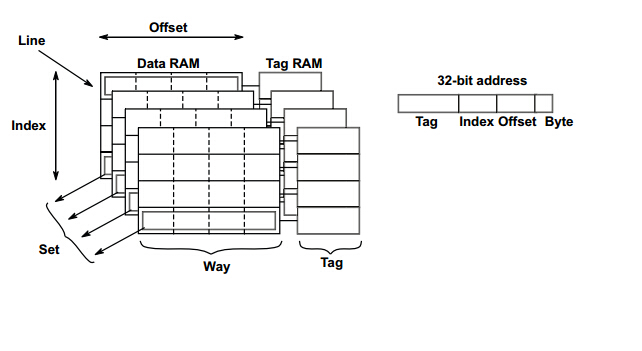

4. Cache architecture

4.1 Harvard architecture have I-Cache and D-cache. Data level 1 caches backed by a unified level 2 cache.

4.2 Cache有地址, 数据,和状态信息。地址告诉Cache信息是从主存储区的哪里来的,这个地址就是tag来标注的。

存储数据至少是一行(line)——A5 A9的一行是8个字(words),A8 A15的一行是16个字(words)。

Associated with each line of data are one or more status bits. Typically, we will have a valid bit,

which marks the line as containing data that can be used. (This means that the address tag

represents some real value.) We will also have one or more dirty bits which mark whether the

cache line (or part of it) holds data which is not the same as (newer than) the contents of main

memory. We will treat this in more detail later in the chapter.(红色表示重要)

5. Cache controller(缓存控制器)

系统自己完成,知道做了什么就行。

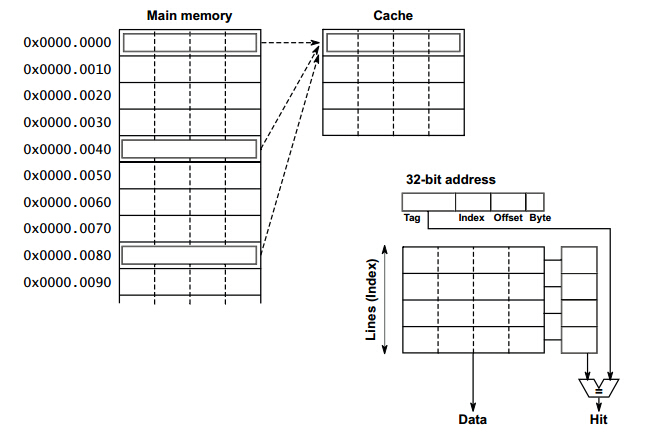

6. Direct mapped caches

cache controller will use two bits of the address (bits 3:2) as the offset to select a word

within the line and two bits of the address (bits 5:4) as the index to select one of the four

available lines. The remaining bits of the address (bits 31:6) will be stored as a tag value.

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?